Broadwell: Neue Details zur Grafik von Intel der 8. Generation

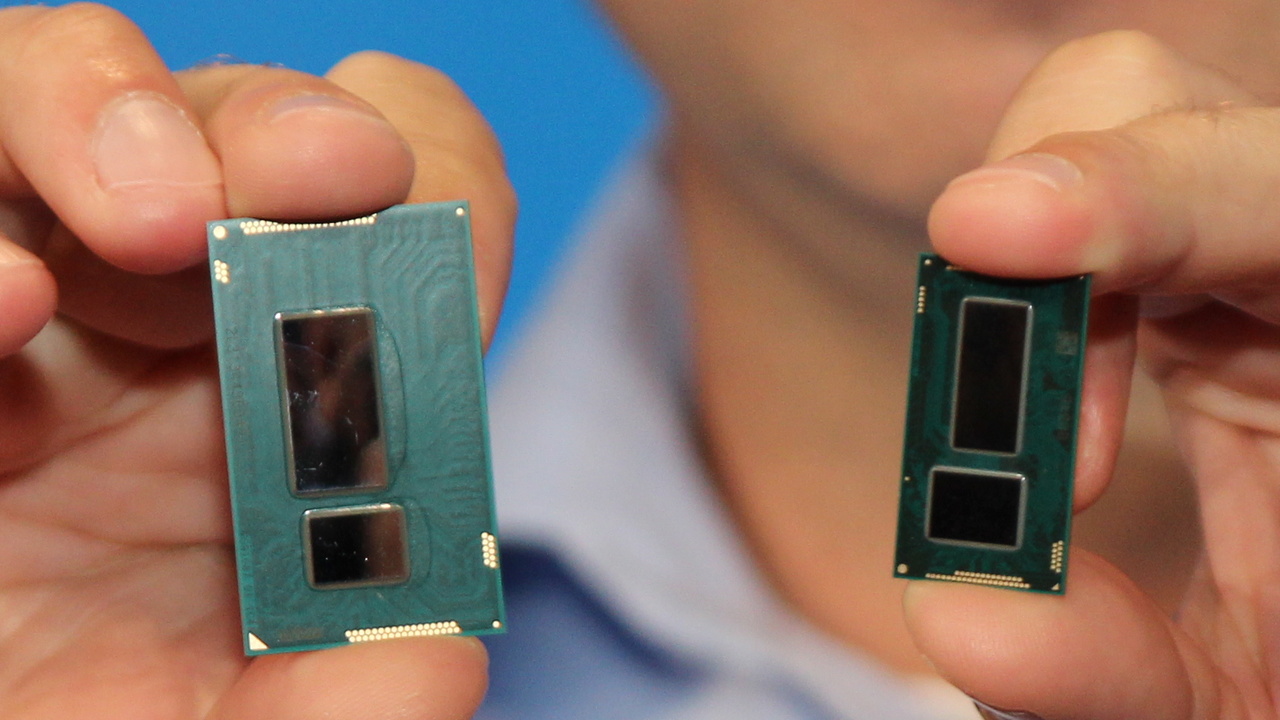

Zum IDF 2014 hat Intel viele Details der Grafik der 8. Generation, die erstmals mit den „Broadwell“-Prozessoren eingeführt wurde, erläutert. Diese Weiterentwicklung ist bis zu 48 Execution Units (EU) groß und kann je nach Modell auf bis zu 128 MByte EDRAM zurückgreifen.

Bereits vor einem Monat hatte Intel erste wenige Details im Rahmen eines Workshop bekannt gegeben. Dabei wurde bereits erklärt, dass die Grundausführung 20 Prozent mehr EUs fassen würde als der Vorgänger, folglich bietet Core M bereits 24 dieser Ausführungseinheiten. Bei diesen Execution Units hat Intel viele kleine Details geändert, die zu einer gesteigerten Leistung in allen Bereichen und erhöhten Effizienz führen. Für den Core M mit 24 EUs gibt Intel bei einer TDP von 4,5 Watt einen Peak-GFLOPS-Wert von 326,4 an – eine deutliche Optimierung zum 11,5-Watt-Vorgänger mit 272 GFLOPS.

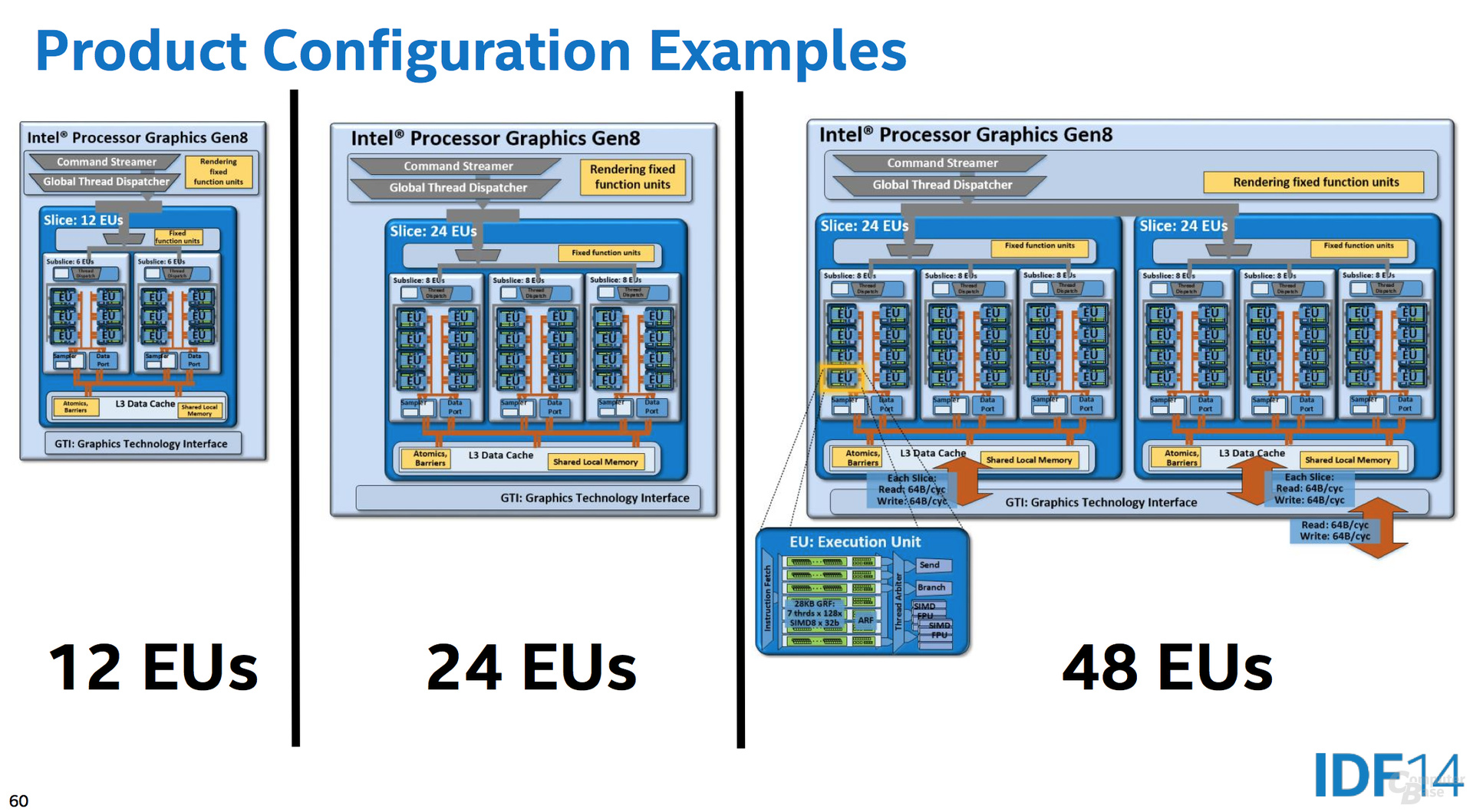

Auf die Slices folgen die Subslices, die acht dieser EUs zusammenfassen. Ein Slice besteht in der typischen Konfiguration aus drei Subslices inklusive den notwendigen Bausteinen zur Anbindung an den Rest der CPU, wie beispielsweise zum L3-Cache über den Ringbus. Wie in den Jahren zuvor ist die Grafiklösung aber einfach skalierbar, Slices können zusammengeschaltet werden. Die bisher als größte Ausbaustufe geplante Lösung für „Broadwell“ verfügt über zwei Slices und somit 48 EUs. Theoretisch sind noch größere Ausbaustufen denkbar, wenn auch für diese Generation unwahrscheinlich. Slices können jedoch auch kastriert werden, beispielsweise auf 12 EUs herunter. Dies ist für die nächste Atom-Generation denkbar.

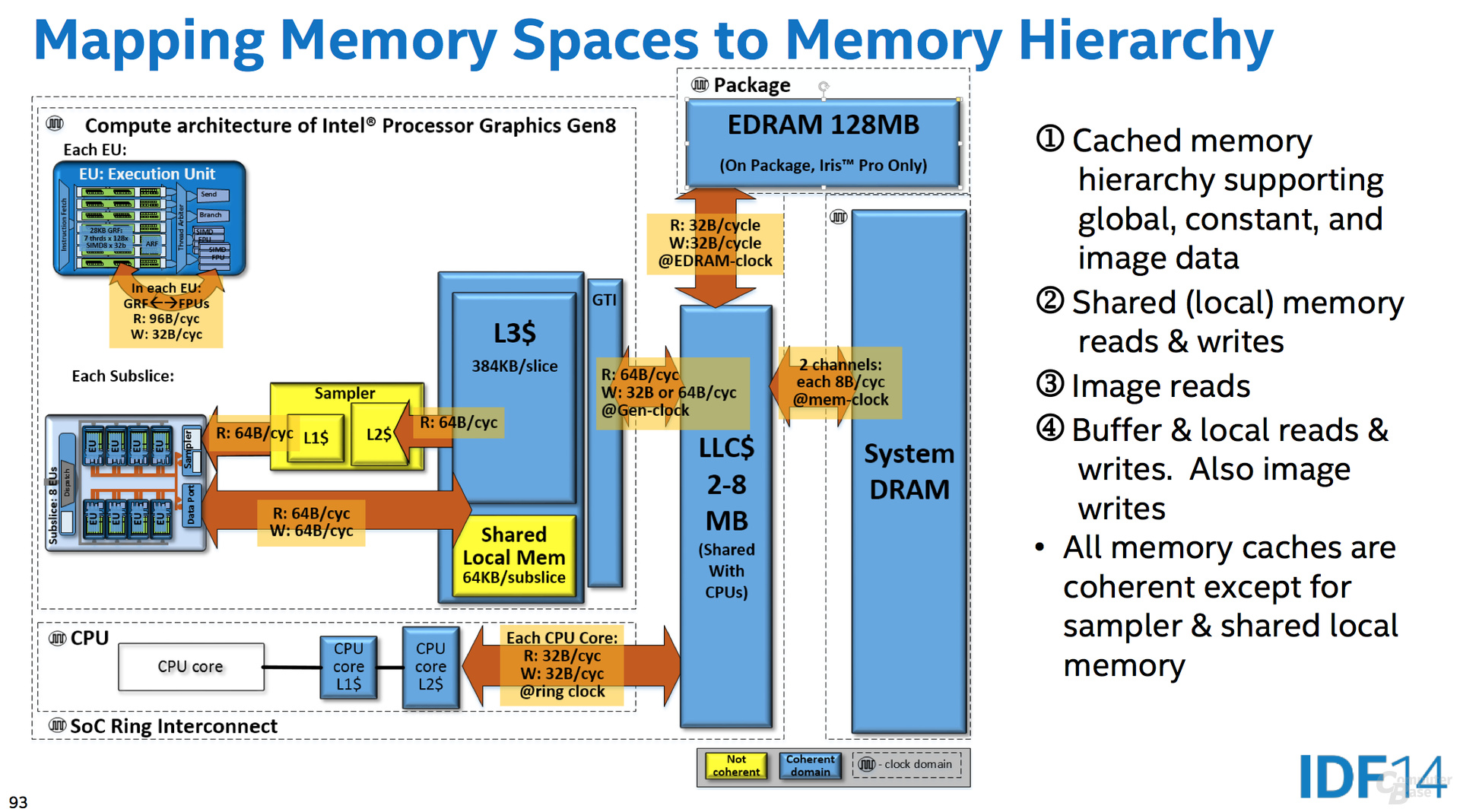

Dem Ringbus kommt bei der Grafikeinheit wie bei den drei Vorgängern eine gewichtige Aufgabe zu. Dieser verbindet die Grafikeinheit nicht nur mit dem L3-Cache, sondern auch mit den CPU-Kernen, dem Speicherinterface und bei Bedarf dem EDRAM, der je nach Modell seinen eigenen Ring-Stop bekommt. Der EDRAM wird wie bei „Haswell“ maximal 128 MByte groß sein können. Im Vergleich zur Gen7.5-Grafikeinheit in „Haswell“ sind nun alle Memory-Caches kohärent, damit konnte der Vorgänger noch nicht dienen.