High Bandwidth Memory: Schnellerer Speicher für Grafikkarten noch 2014

Im Internet ist eine relativ aktuelle Präsentation zu einer der kommenden Speichertechnologien von SK Hynix aufgetaucht. High Bandwidth Memory (HBM) ist gestapelter DRAM-Speicher mit hoher Bandbreite. Eine Roadmap besagt, dass mit ersten Produkten gegen Ende 2014 zu rechnen ist.

Sofern der Zeitplan zutrifft, wäre dann etwa ein Jahr seit der Ankündigung der ersten HBM-Muster im Dezember 2013 vergangen. Seinerzeit hatte SK Hynix zusammen mit Partner AMD die Werbetrommel für die neue Speichertechnik gerührt, die unter anderem bei Grafikkarten und SoCs Einzug halten soll.

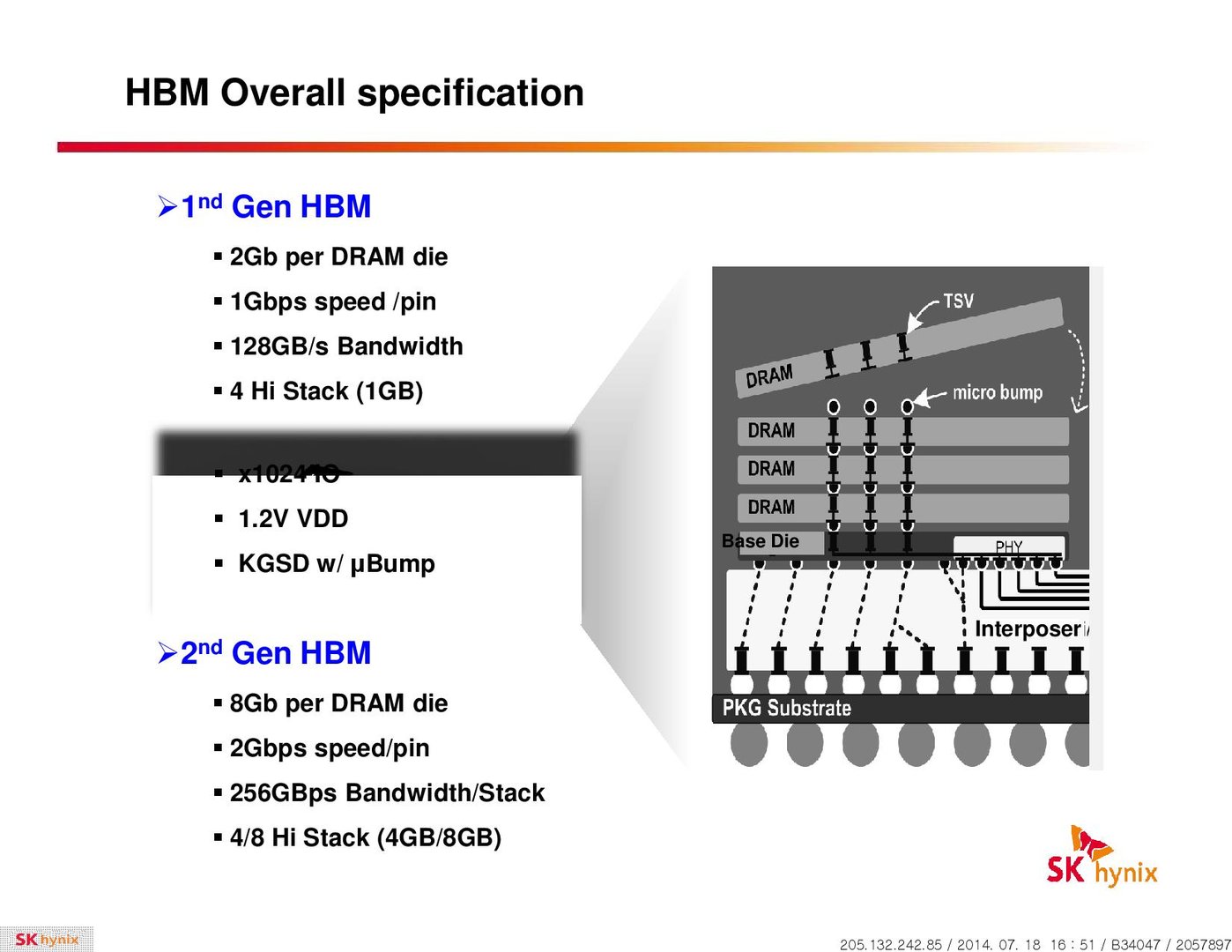

Bei HBM werden mehrere DRAM-Dies übereinander gestapelt (Stacked DRAM) und mittels Silizium-Durchkontaktierung (TSV) vertikal miteinander verbunden. Die erste HBM-Generation soll vier DRAM-Lagen a 2 Gigabit vorweisen, womit ein Chip (Stack) über ein Gigabyte Speicherkapazität verfügt. Die Stapelbauweise ermöglicht nicht nur eine höhere Speicherdichte und damit mehr Speicherkapazität pro Fläche, sondern auch Vorteile bei Leistungsaufnahme und dem Durchsatz. Die höhere Speicherbandbreite besitzt die höhere Priorität.

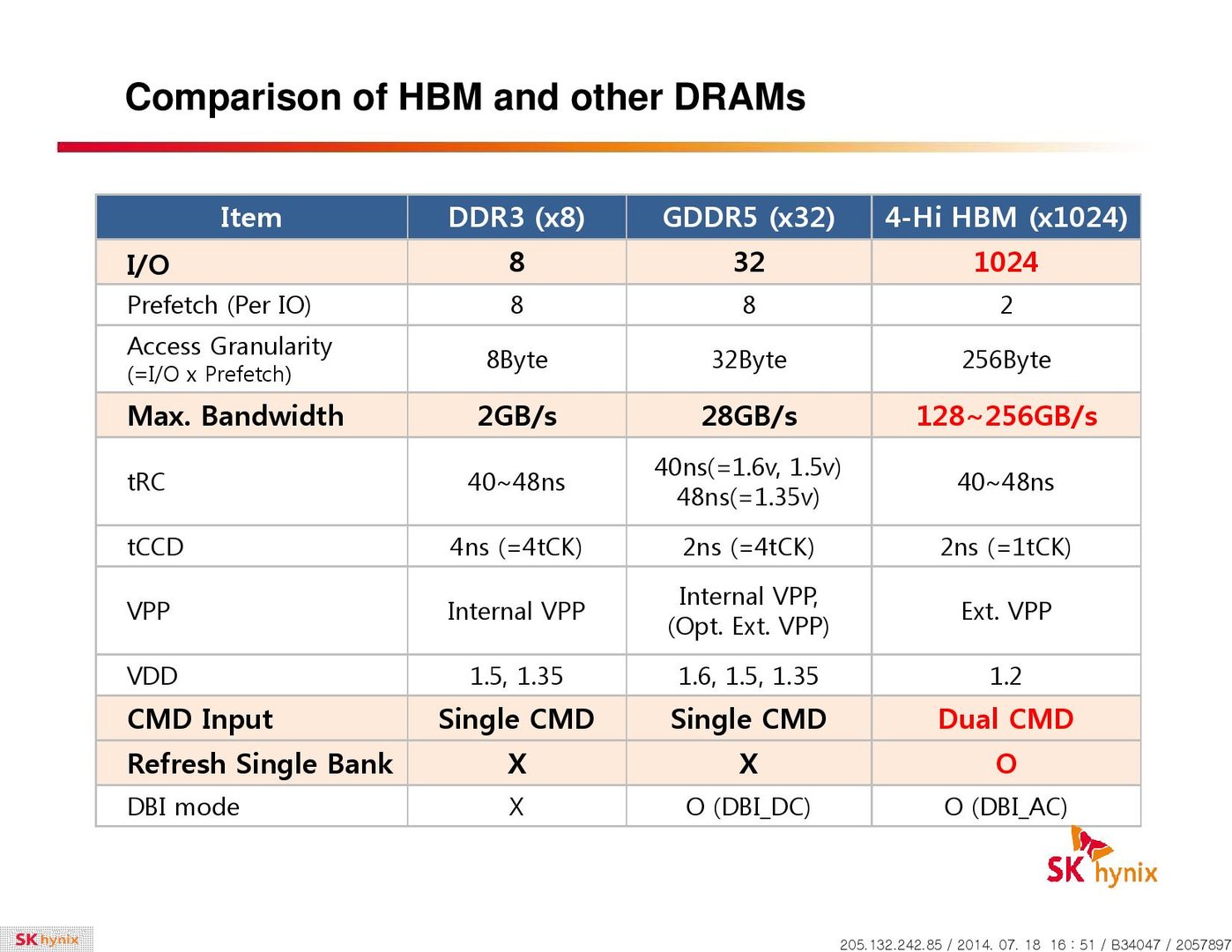

Ein HBM-Chip der ersten Generation soll einen Speicherdurchsatz von 128 Gigabyte pro Sekunde ermöglichen und damit DDR- und GDDR-Speicher weit hinter sich lassen. Bei der nachfolgenden Generation werden bis zu acht DRAM-Schichten mit höherer Speicherdichte und ein Durchsatz von 256 GB/s prognostiziert. GDDR5 erreicht bei aktuell maximal 3.500 MHz einen Durchsatz von 28 GB/s pro Chip.

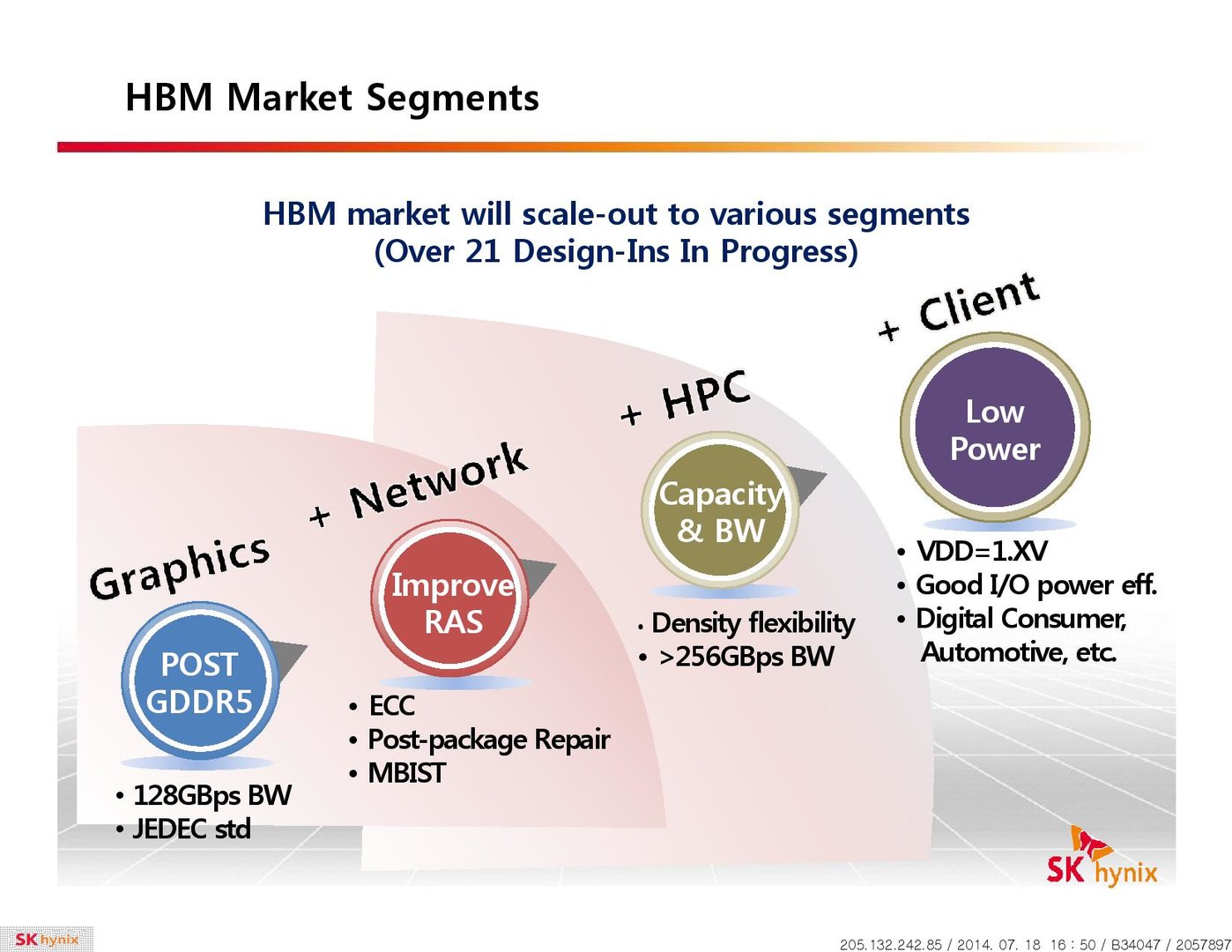

Eine weitere Roadmap suggeriert, dass HBM zunächst im Bereich der Computer-Grafiklösungen als Nachfolger von GDDR5-Speicher eingesetzt und später auf weitere Segmente wie Netzwerke und High Performance Computing ausgedehnt werden soll. Die anfängliche Konzentration auf den GPU-Sektor zeigt sich auch daran, dass SK Hynix auf der eigenen Homepage unter der Rubrik „Graphics Memory“ bereits mit HBM wirbt.

Die enge Zusammenarbeit mit AMD lässt vermuten, dass HBM sein Debüt in Grafiklösungen des Chipentwicklers geben könnte. Vor Monaten tauchten Gerüchte auf, dass die für 2015 erwartete APU „Carrizo“ mit dem Stapelspeicher kombiniert wird, obgleich in durchgesickerten Präsentationen keine Rede davon ist. Auf dem Zettel hat AMD den Einsatz von Stacked DRAM bei APUs aber in jedem Fall.

Ebenfalls denkbar ist der Einsatz bei kommenden Grafikkarten. Ob die für das erste Quartal 2015 erwarteten „Fiji“-GPUs der „Pirate Islands“-Generation bereits mit HBM kombiniert werden, bleibt abzuwarten. Nvidia hat Stacked DRAM ab 2016 für die „Pascal“-Architektur angekündigt.