Forschung: Stanford kombiniert Logikbausteine und Speicherchips

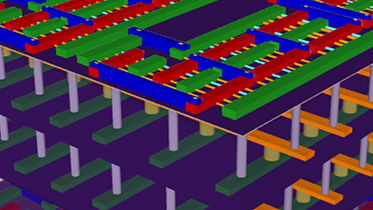

Die Stanford University arbeitet an Chips, bei denen Logikbausteinen und Speicherchips vertikal angeordnet werden. Durch diese Anordnung sollen sich auf dem Weg zu schneller, kleiner und billiger einige Probleme aktueller Computertechnik überwinden lassen.

Die Stanford University beansprucht dabei gleich drei Forschungsdurchbrüche für sich: Eine neue Art, Transistoren herzustellen, eine neue Speichertechnologie und einen „radikal“ neuen Weg, Computerchips zu stapeln.

Anstatt auf klassische Leitungen zu setzen, sollen die kombinierten Chips tausende, nur Nanometer große „elektronische Fahrstühle“ enthalten, um Daten zwischen den einzelnen Schichten und damit zwischen den Speicher- und Logikbausteinen zu transportieren. Für diese Leitungen werden CNTs, also Kohlenstoffnanoröhren genutzt.

Die Speicherchips bestehen dabei nicht aus Silizium, sondern aus Titan- und Hafnium-Oxid und Platin, wobei eine Oxidschicht zwischen zwei Metallschichten angeordnet ist. Dieser RRAM verbraucht im Vergleich zu aktuellen Speichertechnologien weniger Energie. Eine weitere wichtige Eigenschaft: Das Sandwich aus Metall und Oxid lässt sich bei wesentlich geringeren Temperaturen fertigen als herkömmlicher, auf Silizium basierender Speicher. Erst dies macht die Anordnung und Verbindung mit Kohlenstoffnanoröhrchen möglich, da Logikbausteine bei aktuellen Fertigungstemperaturen von 1.000 Grad Celsius schmelzen würden.

Philip Wong, der die Arbeitsgruppe in Kooperation leitet, äußert sich optimistisch über die neue Technik: „Mit dieser neuen Architektur können Elektronikhersteller die Kraft eines Supercomputers in ihre Hand bringen.“

Die Technologie befindet sich noch in einem frühen Stadium, die Fertigungsweise soll allerdings bereits skalierbar sein. Bisherige Versuche wurden lediglich in einem akademischen Labor mit weniger hochentwickelten Werkzeugen durchgeführt als sie Technologieunternehmen bereits zur Verfügung stehen, was weitere Fortschritte verspricht.