Quad-Level Cell: Intel sieht 3D-NAND als Wegbereiter für 4 Bit pro Zelle

Nach TLC mit drei Bit pro Speicherzelle ist der nächste Schritt zur Kapazitätssteigerung bei NAND-Flash der auf vier Bit. Intel forscht wie andere Branchen bereits länger an Quad-Level Cell (QLC) und sieht im gestapelten 3D-NAND eine Möglichkeit, die Probleme der Technik in den Griff zu bekommen. Einen Termin gibt es noch nicht.

Wie Computerworld berichtet, erklärte Intels Bill Leszinske, dass QLC Technik zu einer höheren Datendichte bei einer ganzen Reihe von Geräten verhelfen könnte. Unter anderem in ihrer Speicherkapazität begrenzte Smartphones könnten davon profitieren. Nach SLC mit einem Bit, MLC mit zwei Bit und TLC mit drei Bit pro Zelle wäre QLC nur der nächste logische Schritt.

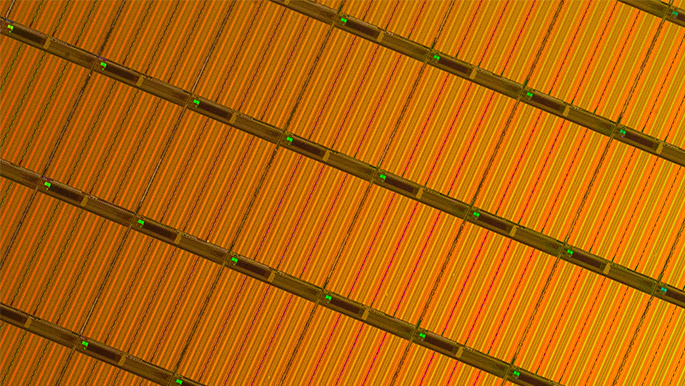

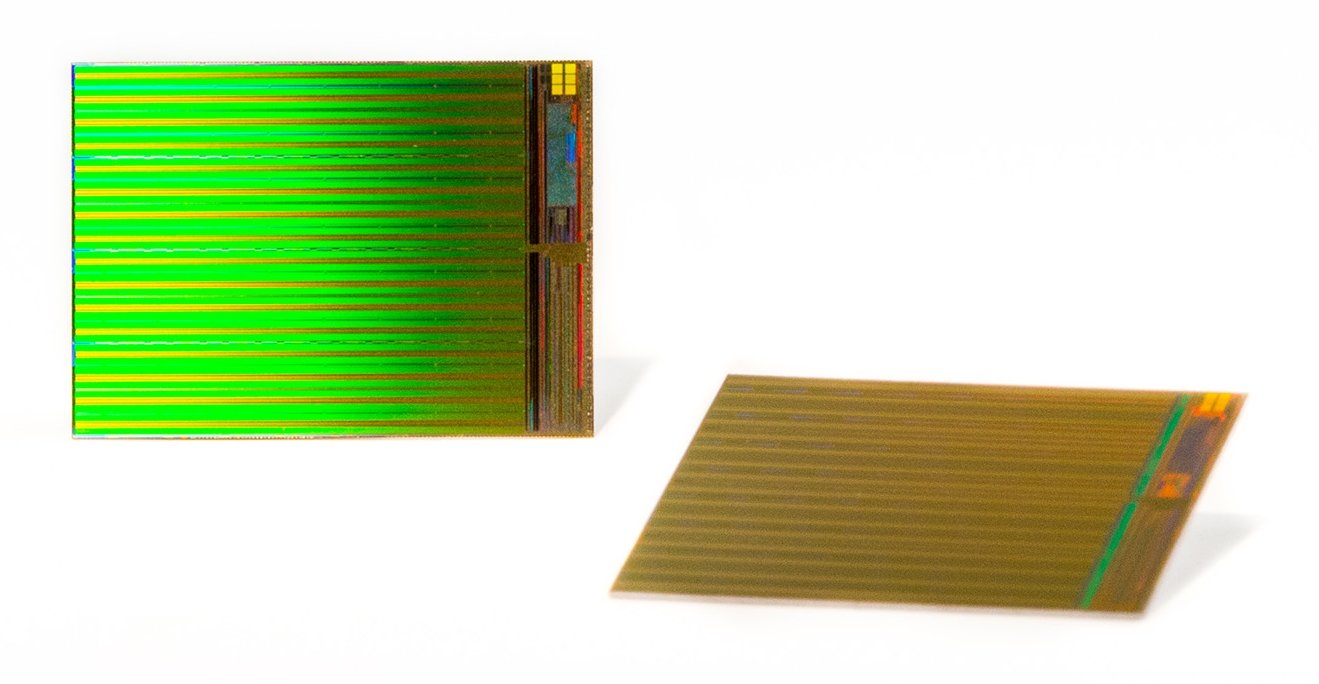

Bevor QLC den Markt erreicht, wird Intel zunächst gemeinsam mit Micron die Datendichte von NAND-Flash-Dies dank neuer 3D-Technik auf 256 Gbit (MLC) respektive 384 Bit (TLC) steigern und damit 2,5-Zoll-SSDs mit bis zu 10 Terabyte oder mehr ermöglichen. Mit QLC wären künftig noch höhere Kapazitäten denkbar.

Völlig neu ist die Idee von 4 Bits pro Speicherzelle allerdings nicht, bereits 2006 gab es erste Versuche und neben Intel forschen weitere Vertreter der Branche seit Jahren an entsprechenden Lösungen.

Ohne weiteres lässt sich die Zahl der Informationsbits nicht erhöhen, denn pro Bit steigt die Zahl der benötigten Ladungszustände in der Zelle exponentiell. Genügten bei SLC noch zwei unterschiedliche Ladungen für die Binärwerte 0 oder 1 sind es bei MLC bereits vier, bei TLC acht und bei QLC ganze 16 verschiedene Zustände. Dadurch nimmt auch die Fehleranfälligkeit zu – bereits für TLC werden umfangreiche Maßnahmen zur Fehlerkorrektur benötigt. Die durch die möglichen Schreib-/Löschzyklen bedingte Haltbarkeit des NAND-Flash nahm von SLC bis TLC ab und könnte mit QLC weiter sinken.

Eine Lösung, um QLC mit höherer Haltbarkeit zu realisieren, könnte im neuartigen 3D-NAND liegen. Die „Flucht“ in die Vertikale mit übereinander liegenden Zellschichten ermöglicht es, auf gleicher Fläche mehr Daten zu sichern, ohne die Zellstruktur weiter zu verkleinern. Immer feinere Herstellungsprozesse führen zu einer Verkürzung der Haltbarkeit von NAND-Flash, da die Speicherzellen dichter „zusammenrücken“ und somit Interferenzen zunehmen, wodurch Ladungszustände schon früher nicht klar unterschieden werden können.

Mit Anhebung der Ladungszustände in den Zellen verstärkt sich die Problematik, weshalb eine Umsetzung mit höherem Zellabstand, wie sie die dreidimensionale Bauweise ermöglicht, plausibel erscheint. Entsprechend optimistisch zeigte sich Leszinske, der erklärte, dass Intels 3D-NAND-Technologie „mit hoher Kapazität und geringer Interferenz“ QLC-Speicher zu einer „echten Chance“ machen würde.

Für Anwendungsbereiche mit hohen Anforderungen an die Haltbarkeit und Datenintegrität wird QLC genau wie TLC aber noch lange kein Thema sein.