TSMC 16FFC: Weniger Leistungsaufnahme für das Internet der Dinge

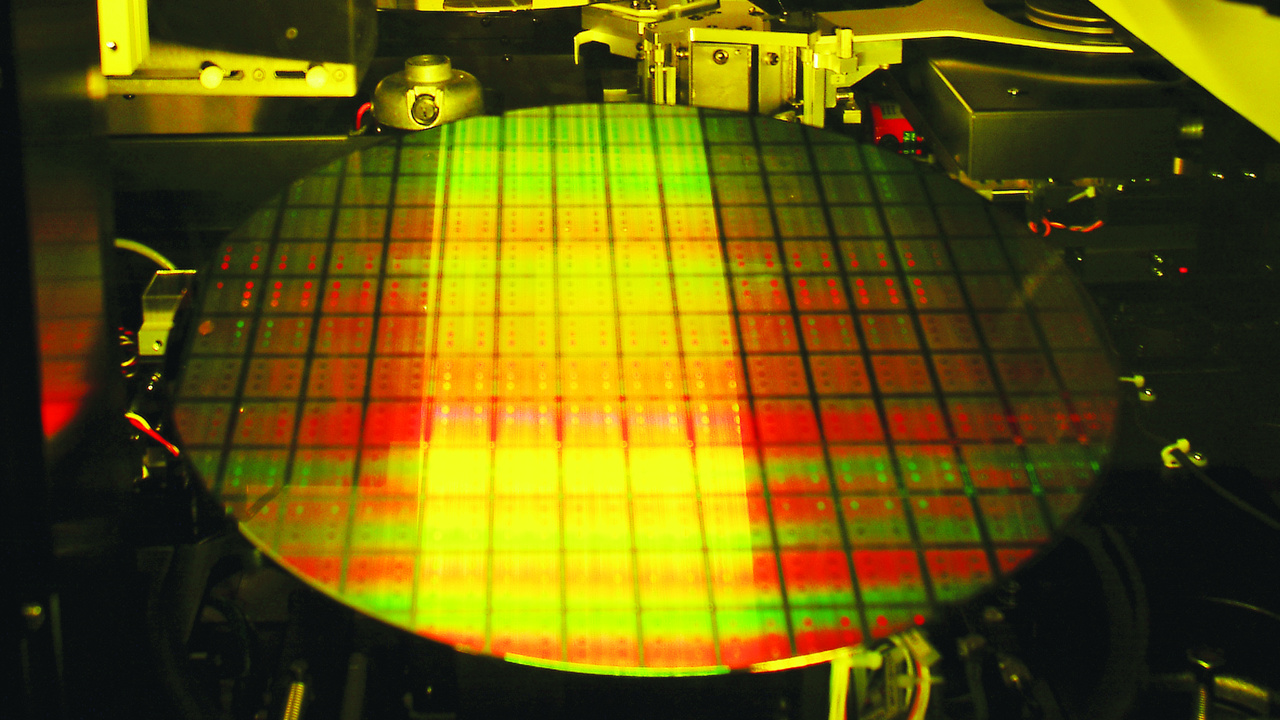

Im Rahmen des TSMC 2015 Technology Symposium hat der weltgrößte Auftragsfertiger einen zusätzlichen 16-nm-FinFET-Prozess angekündigt. Dieser basiert auf dem bereits optimierten Design „16FF+“ und soll als „Compact“-Version kostengünstige Lösungen für das Internet of Things bereitstellen.

Dem Internet der Dinge werden in diesem Zusammenhang aber auch Wearables zugeordnet, für die das zusätzliche Prozessdesign geeignet sein soll. Dr. Mark Liu, Co-CEO und Präsident von TSMC erklärt, dass das 16FFC (16 nm FinFET Compact) getaufte Verfahren eine Ultra-Low-Power-Variante von 16FF+ ist. Unterm Strich soll die Leistungsaufnahme um 50 Prozent gegenüber 16FF+ gesenkt werden, nur noch 0,55 Volt sollen als nominale Eingangsspannung anliegen. Durch eine Vereinfachung des Designprozesses, kleinere Dies aber auch viele Gemeinsamkeiten mit 16FF+ soll 16FFC kostengünstige Möglichkeiten bieten.

Liu erwartet, dass Anfang 2016 die risk production von 16FFC hochgefahren wird. Bis zum zweiten Quartal sollen alle weiteren Baustellen aus der Welt geschafft sein, da Kunden die bestehenden Designtools von 16FF+ weiter nutzen können. TSMC will damit einen möglichst nahtlosen Übergang schaffen und so am Ende mit 16FFC die „most cost-effective solution for the mid- to low-end market“ schaffen. Ab dem zweiten Halbjahr könnten so deshalb schon die ersten Produkte auf Basis von 16FFC im Handel stehen.

Parallel zur Ankündigung von 16FFC hat TSMC auch die aktuellsten Meldungen zu 16FF+ als Nachfolgestandard bei TSMC für die aktuelle 20-nm-Fertigung im Gepäck. Im Sommer dieses Jahres soll die Massenproduktion anlaufen, über ein Dutzend tape-outs von Produkten sind bereits erfolgt. Insgesamt erwartet der Auftragsfertiger bis zum Jahresende mehr als 50 dieser designtechnisch fertigen Produkte. Die optimierte 16-nm-FinFET-Produktion soll nicht nur wahlweise 50 Prozent weniger Strom bei gleicher Leistung verbrauchen beziehungsweise 40 Prozent schneller bei gleicher Leistungsaufnahme sein als der aus eigenem Haus stammende 20-nm-Prozess. Auch im Vergleich zur Konkurrenz sieht TSMC noch einen Vorsprung von zehn Prozent. Bei der Yield-Rate sei der Hersteller auf einem guten Weg, die bisherige Ausbeute der 20-nm-Fertigung zu erreichen.

Mit dem Prozess 28HPC+ bietet TSMC zudem in Kürze eine noch einmal verbesserte 28-nm-Fertigungstechnologie. Diese soll mit überarbeiteten SRAM-Designs, geringen Leckströmen und weiteren Optimierungen das schnellste 28-nm-Verfahren bilden. Im sechsten Jahr der 28-nm-Technologie könne die Fertigung so laut TSMC noch einmal eine 15 bis 45 Prozent höhere Leistung bei gleicher Leistungsaufnahme als das bisherige 28HPC-Verfahren bieten.

Zur Thematik der 10-nm-Fertigung hat TSMC erneut den bereits seit letztem Oktober bekannten Fahrplan bestätigt. Erste Testprodukte sind bereits voll funktionsfähig, im vierten Quartal 2015 soll die risk production anlaufen. Ein Jahr später soll dann die Massenproduktion beginnen. EDA-Software-Anbieter Cadence hatte bereits in der letzten Woche verkündet, dass digitale und analoge Design-Tools für den 10-nm-Prozess die ersten Zertifizierungsprozesse von TSMC erfolgreich abgeschlossen haben, bis Juni 2015 sollen alle Überprüfungen fertiggestellt sein.

Weitere Details zu einigen dieser Themen werden am 16. April erwartet. Dann gibt TSMC die Quartalszahlen für die ersten drei Monate des Jahres bekannt und äußert sich gegenüber Analysten zu den Zukunftsplänen.