Zen: AMDs neue CPU angeblich modular und mit vier Kernen

Mit Zen, so der Codename für AMDs neue High-End-Prozessorarchitektur, möchte der Hersteller wieder an den Erfolg alter Tage anknüpfen. Im Forum von Planet3DNow will ein Nutzer an einige Folien von AMDs Financial Analyst Day gekommen sein, der am 6. Mai stattfindet. Diese verraten erste technische Details.

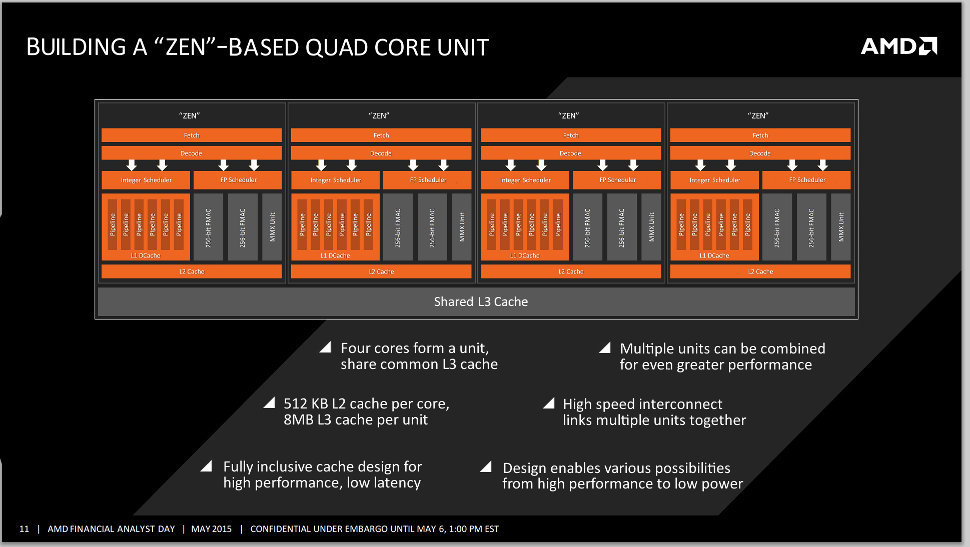

Den Folien zu Folge wird Zen ein modular aufgebauter Quad-Core-Prozessor sein. Eine „Zen Einheit“ besteht aus vier CPU-Kernen mitsamt einem geteilten L3-Cache. Da mehrere dieser Einheiten über einen „High Speed Interconnect“ zusammen geschaltet werden können, sind neben Prozessoren mit vier Kernen also genauso Modelle mit zum Beispiel acht, zwölf oder 16 Kernen denkbar. Aufgrund der modularen Bauweise soll sich Zen sowohl für High-Performance- als auch für Low-Power-Einsatzzwecke eignen.

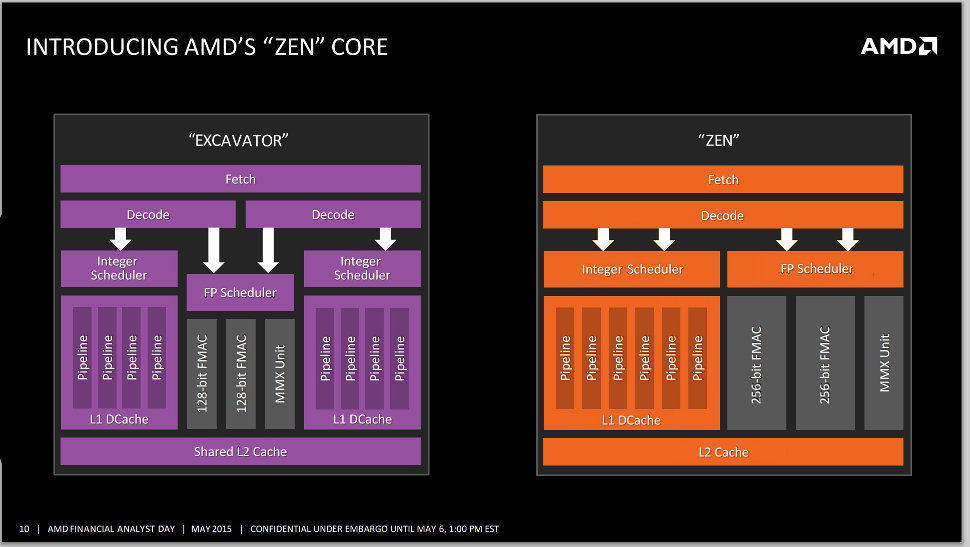

Zen an sich orientiert sich offensichtlich nicht mehr am alten Bulldozer-Prinzip und wird, anders als die letzte Ausbaustufe Excavator, nicht mehr über einen aufgeteilten Integer-Scheduler verfügen, der mehr Einheiten ansprechen soll. Sprich, die Modul-Bauweise wird es in Zen nicht mehr geben. Anstatt zwei geteilte Integer-Einheiten, die jeweils vier Pipelines ansprechen, soll es nur noch eine einzige geben, die sechs Pipelines mit Daten füttert. Dadurch sollte die Pro-MHz-Leistung, die große Schwäche des Bulldozer-Designs, steigen können. Stattdessen soll Zen, wie Intels aktuelle Prozessoren, Hyper Threading beziehungsweise SMT (Simultaneous Multithreading als „Nicht-Intel-Begriff“) unterstützen.

Auffällig ist zudem, dass die zwei 128 Bit breiten Floating-Point-Einheiten aufgebohrt worden sein sollen zu zwei 256-Bit-Einheiten. Dadurch sollte Intels AVX2-Befehlssatz unterstützt werden. Darüber hinaus stehen jedem Zen-Kern 512 KByte dedizierter L2-Cache zur Verfügung, eine Zen-Einheit hätte also zwei Megabyte. Den L3-Cache von acht Megabyte pro Einheit teilen sich die Kerne. Bei der Modul-Bauweise der Bulldozer-Derivate gehört auch der L2-Cache zu den geteilten Ressourcen. AMD soll das komplette Cache-Design auf geringe Latenzen und eine hohe Performance ausgelegt haben.

Abgesehen von den Folien hat sich der Forennutzer auch mit weiteren Details gemeldet. Demnach soll ein einzelner Zen-Kern kleiner als 10 mm² sein (14-nm-Fertigung). Ein Excavator-Kern soll dagegen eine Größe von 14,48 mm² aufweisen (28 nm).

Auch wenn die Echtheit zur Zeit nicht bestätigt werden kann, sind die Folien im üblichen Präsentationsstil von AMD gehalten. Deswegen und da der Financial Analyst Day bereits nächste Woche stattfinden wird, ist es durchaus möglich, dass die Folien der Realität entsprechen. Neben Zen soll AMD auf dem Financial Analyst Day angeblich ebenso über die neue Carrizo-APU reden, über Seattle (64-Bit-ARM im eigenen Design) und möglicherweise auch über neue Grafikkarten sprechen.

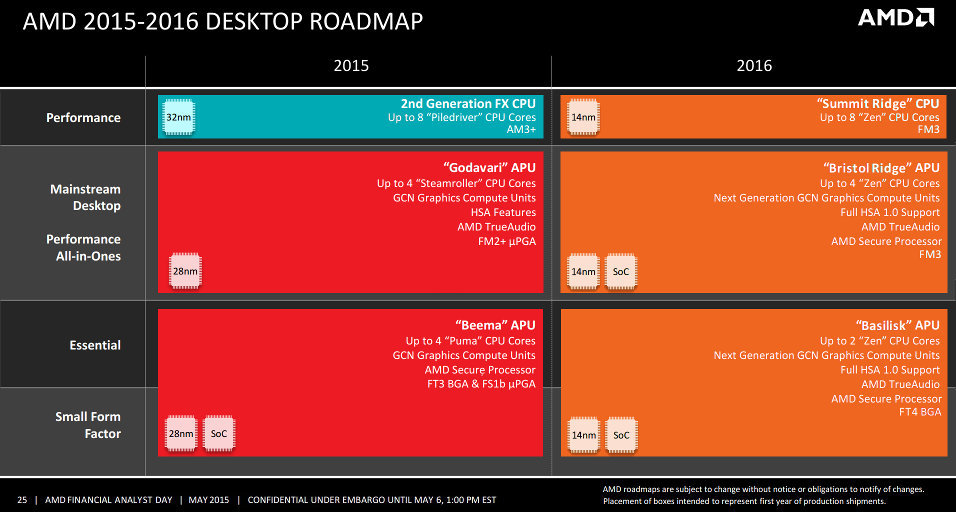

Der mysteriöse Foren-Nutzer hat wieder zugeschlagen, diesmal mit zwei Roadmaps – wahrscheinlich sind entweder sämtliche Informationen korrekt oder komplett der Phantasie entsprungen. Laut diesen Roadmaps will AMD im Desktop-Segment wieder einen High-End-Prozessor anbieten, der als reine CPU ohne GPU daher kommen wird. Unter dem Codenamen „Summit Ridge“ soll dieser acht Zen-Kerne fassen und in den Sockel FM3 passen.

Im Mainstream-Segment soll dann die „Bristol-Ridge“-APU mit vier Zen-Kernen und einer „Next-Generation-GCN“-Grafikeinheit werben. Die APU mitsamt kompletter HSA-1.0-Unterstützung passt auf den Sockel FM3. Als reiner BGA-Chip soll dann „Basilisk“ als APU mitsamt zwei Zen-Kernen und ansonsten gleichen Merkmalen erscheinen.

Bristol Ridge und Basilisk wird es laut den Roadmaps ebenso im mobilen Segment geben als BGA-Chips geben. Die Low-Power-Schiene wird dort aber von „Styx“ besetzt, AMDs erstes K12-Produkt auf ARM-Basis. Zwei CPU-Kerne mitsamt GCN-Grafik sollen vorhanden sein, dasselbe gilt für die HSA-1.0-Unterstützung. Die „Scenario Design Power“ soll zwei Watt betragen.

Sämtliche Produkte sollen nächstes Jahr erscheinen und im 14-nm-Prozess hergestellt werden.

-

Angebliche Desktop-Roadmap von AMD (Bild: insider2015)

Angebliche Desktop-Roadmap von AMD (Bild: insider2015)