PS5007-E7: Details zum ersten NVMe-SSD-Controller von Phison

Auf Messen wie der CES und der Computex waren SSD-Prototypen mit neuem PS5007-Controller von Phison bereits zu sehen. Eine Demonstration zur Leistungsfähigkeit gab es ebenfalls. Von offizieller Seite folgen die Spezifikationen.

Bereits bekannt war, dass der in einem 28-nm-Prozess gefertigte PS5007 über acht Speicherkanäle verfügt und als Schnittstelle PCI Express 3.0 x4 nutzt, wie sie bei schnellen PCIe-SSDs wie der Intel SSD 750 oder der Samsung SM951 eingesetzt wird. Bei einer Demonstration auf der Computex 2015 lieferte ein SSD-Prototyp mit PS5007 mit 2.700 MB/s und 340.000 IOPS beim Lesen und 1.190 MB/s und 264.000 IOPS beim Schreiben erste Hinweise auf das Leistungspotenzial.

Die offiziellen Spezifikationen nennen nun beim Einsatz mit MLC-Flash-Speicher Maximalwerte von 2.600 MB/s und 1.300 MB/s beim sequenziellen Lesen und Schreiben. Die Zahl der Befehle pro Sekunde wird mit 300.000 IOPS lesend und 200.000 IOPS schreibend bei wahlfreien Zugriffen angegeben. Während PCI Express 3.0 die physische Schnittstelle bildet, stellt das NVMe-Protokoll die logische Schnittstelle dar. Der PCIe-Stromsparmodus L1.2, der als Pendant zu DevSleep bei SATA zu sehen ist, wird ebenfalls unterstützt. Auf Seiten des DRAM-Cache wird von Phison die Variante DDR3L mit reduzierter Betriebsspannung angeführt.

Die Spezifikationen bescheinigen dem Controller eine Unterstützung der NAND-Flash-Typen MLC und TLC der Generation „1z nm“ sowie 3D-NAND. Zudem wird mit einer „End-to-End Data Path Protection“ geworben. Diese umfasst laut Phison eine Fehlererkennung und -korrektur beim Datentransfer zwischen Controller und DRAM sowie Controller und NAND Flash.

Pro Speicherkanal unterstützt der Controller acht und damit insgesamt 64 CE (Chip Enable). In der Regel wird maximal pro CE ein NAND-Flash-Die eingesetzt, womit die maximale Kapazität bei üblichen 128-Bit-Dies bei einem TiB liegen würde. Phison gibt allerdings an, dass der PS5007 bis zu zwei TiB respektive 2 TB nutzbaren Speicher unterstützt. Denkbar ist dabei die Konfiguration von zwei Dies pro CE. Bei SSDs, bei denen ein Terabyte Speicherplatz über einen Vier-Kanal-Controller realisiert wird, wie dies zum Beispiel bei Terabyte-SSDs mit SM2246EN-Controller der Fall ist, kommt letztere Methode zum Einsatz. Der Nachteil ist, dass beide Dies nicht simultan ansprechbar sind, da nur ein CE-Signal zur Verfügung steht.

Für den SATA-Controller PS3110-S10 gibt Phison bei nur 32 CE ebenfalls bis zu 2 TB Kapazität an, was zeigt, dass auch Lösungen mit vier 128-Bit-Dies pro CE denkbar sind.

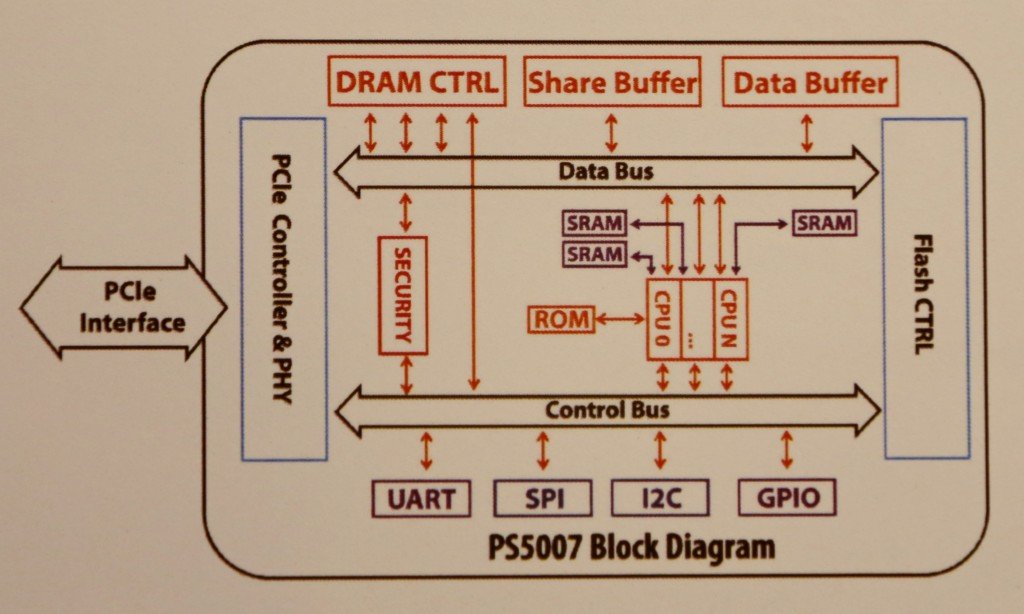

Vor etwa einem Jahr hatte Phison gegenüber der Website The SSD Review erste Angaben zum PS5007-Controller gemacht. Die Rede war von einem „32-Bit multi-core 8 channel PCIe Gen3 x4 controller“, der neben MLC und TLC auch SLC unterstützt. Zudem wurde eine AES-256-Bit-Verschlüsselung und TCG Opal 2.0 als unterstützte Funktionen angeführt. Was sich genau hinter den Funktionen „SmartFlush“ und „GuaranteedFlush“ verbirgt, bleibt weiterhin unklar.

Die Veröffentlichung der Spezifikationen zum PS5007 ist ein weiterer Schritt zur Markteinführung erster SSDs auf dessen Basis. Wann diese den Markt erreichen, ist noch nicht bekannt. Hersteller wie Mushkin und G.Skill hatten im Vorfeld Prototypen mit Phisons neuem Chip ausgestellt.