Quadruple-Level Cell: Toshibas QLC-NAND mit 4 Bit pro Zelle für Archiv-SSDs

Während immer mehr SSDs mit 3 Bit pro Speicherzelle (TLC) auf den Markt kommen, arbeitet die Branche längst an neuen Speicherchips mit 4 Bit pro Zelle (QLC). Diese Quad-Level Cell oder auch Quadruple-Level Cell genannte Speicherform ist auch bei Toshiba ein Thema.

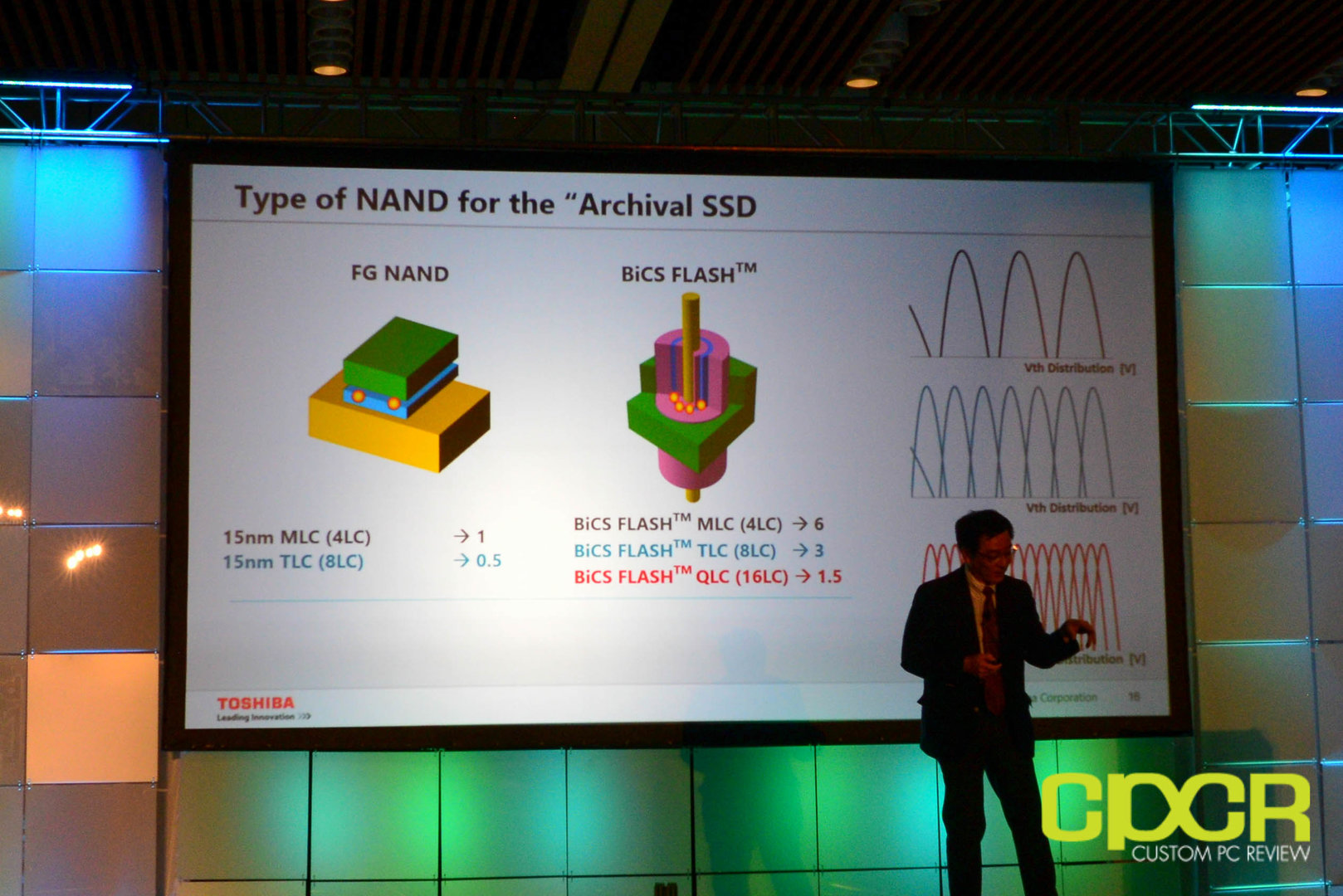

Auf dem Flash Memory Summit ging Toshiba erwartungsgemäß auf den erst jüngst vorgestellten 3D-NAND mit 48 übereinander liegenden Zellschichten (Layer) ein, den das Unternehmen unter der Marke BiCS Flash führt. Der 3D-Speicher bietet in der MLC-Version mit zwei Bit pro Zelle eine Kapazität von 128 Gigabit pro Die. Als TLC-Variante mit drei Bit Pro Zelle werden 256 Gigabit geboten. QLC BiCS – BiCS steht für Bit Cost Scalable – soll mit vier Bit pro Speicherzelle die Kapazität pro Chip weiter anheben. Details zur Umsetzung, zum Beispiel über wie viele Ebenen der QLC-3D-NAND verfügen wird, wurden nicht preisgegeben.

Ein Problem bei der Steigerung der Datenbits pro Speicherzelle ist die wachsende Komplexität. Müssen bei SLC-Flash nur zwei Zustände unterschieden werden, sind es bei 2-Bit-MLC derer vier und bei TLC bereits acht. Mit vier Bit pro Zelle steigt die Zahl auf 16 Zustände. Bereits bei TLC-NAND müssen aufwendigere Maßnahmen zur Fehlerkorrektur eingesetzt werden, um eine annehmbare Haltbarkeit zu gewährleisten. Die Zahl der möglichen Schreibvorgänge nimmt mit der Komplexität der Speichervorgänge ab.

Vor diesem Hintergrund wird klar, warum Toshiba QLC-Speicher daher vorwiegend für den Einsatz zu Archivierungszwecken vorsieht. Bei solchen „Archiv-SSDs“ werden Daten meist nur selten oder gar nur einmalig auf den Flash-Speicher geschrieben und stehen dann vor allem zum Abruf bereit, was nur Lesezugriffe bedeutet. Dennoch soll der QLC-NAND durch die 3D-Struktur mit größeren Zellabständen in puncto Haltbarkeit noch vor Toshibas 15-nm-MLC-NAND mit zweidimensionalem Aufbau liegen, wie eine Grafik veranschaulicht.

3D-NAND mit mehreren übereinander liegenden Zellschichten ermöglicht den Herstellern, mehr Kapazität pro Chip zu erreichen, ohne die Strukturbreiten weiter zu verkleinern. Mit kleineren Strukturbreiten sinkt auch die Haltbarkeit des NAND-Flash, was daran deutlich wird, dass MLC-NAND der früheren Generationen oftmals noch mit rund 10.000 Schreibzyklen (P/E Cycles) angegeben wurde, während heutiger MLC-NAND teils mit weniger als 3.000 Zyklen spezifiziert ist.

Aus diesem Grund sieht nicht nur Toshiba in 3D-NAND auch die Lösung zu mehr Bit pro Zelle. Intels Vice President for Strategic Planning/Marketing for NVM Solutions Bill Leszinske hatte Ende März kurz nach der Ankündigung der ersten 3D-NAND-Generation von Intel/Micron die Forschungen an QLC-Speicher angesprochen. Dass die Branche dieses Ziel seit geraumer Zeit verfolgt, zeigt ein Bericht aus dem Jahr 2007.

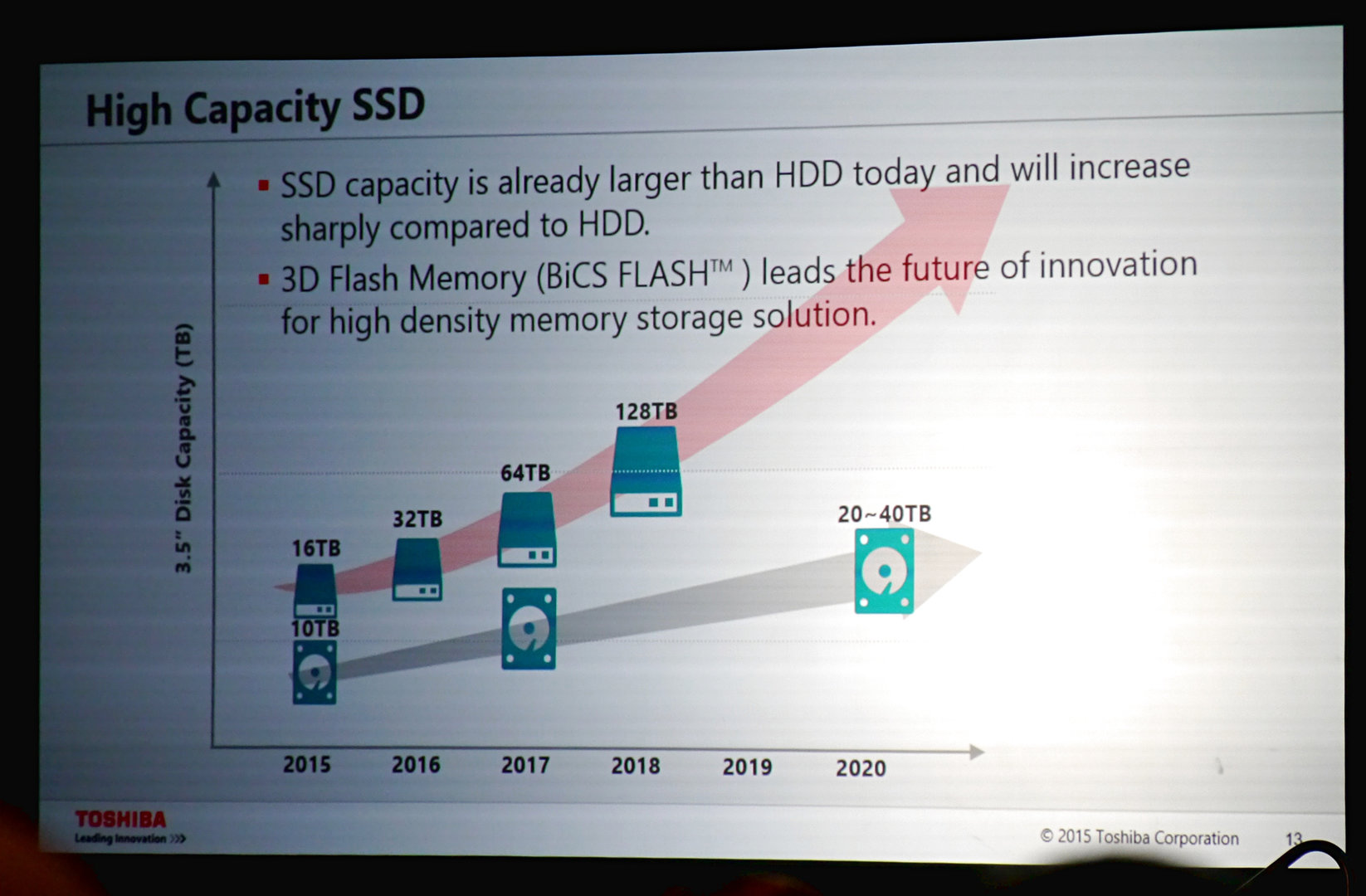

Überdies gibt Toshiba eine Prognose zu der Steigerung der SSD-Kapazitäten in den kommenden Jahren ab. Dass 16 TByte schon jetzt machbar sind, hat Samsung bereits demonstriert. In den kommenden drei Jahren soll sich die Kapazität jeweils verdoppeln, sodass 2018 bereits mit 128-TByte-SSDs zu rechnen sei. Der lange Zeit geltende Kapazitätsvorsprung von herkömmlichen Festplatten (HDDs) kehrt sich laut Toshibas Roadmap um. HDDs sind heute mit bis zu 10 Terabyte erhältlich, bieten aber weiterhin einen erheblichen Preisvorteil bei jedoch geringerer Leistung als SSDs.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!