Speichertechnologie: Toshiba stapelt 16 NAND-Dies mit TSV übereinander

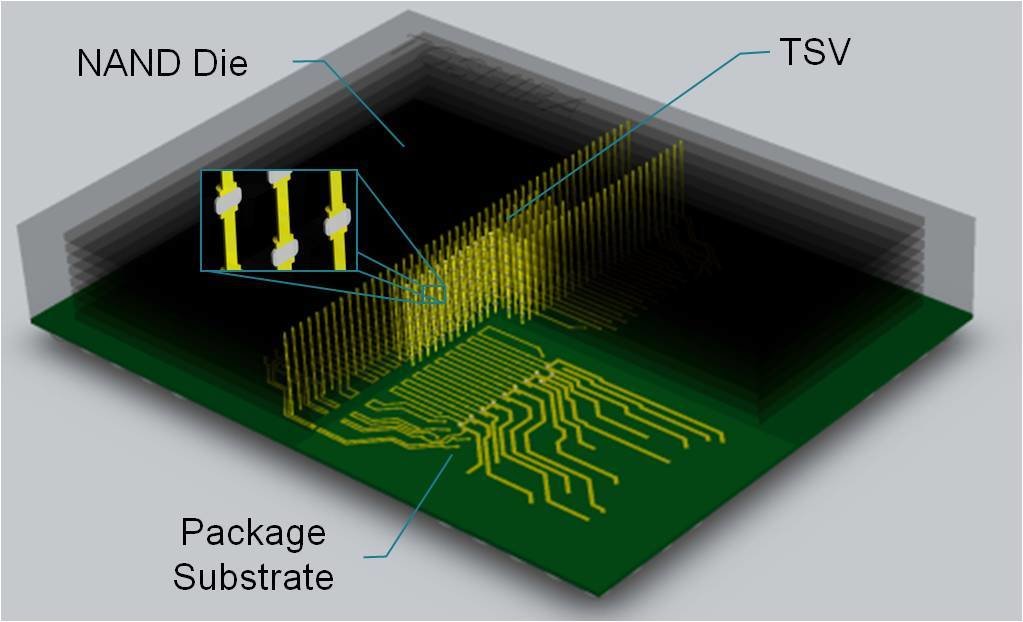

In einem Chip-Gehäuse kommen oftmals mehrere übereinander gestapelte NAND-Chips zum Einsatz. Werden diese bislang in der Regel mit Drähten miteinander verbunden, bietet die vertikale Siliziumdurchkontaktierung (TSV) dem gegenüber Vorteile. Toshiba stellt erste NAND-Flash-Speicher mit 16 Dies und TSV vor.

Zur Verbindung der 16 übereinander gestapelten Dies dienen laut Toshiba „vertikale Elektroden und Vias (Durchkontaktierungen), die durch die Halbleiter-Dies hindurchgehen“. Die Methode ist nicht mit 3D-NAND zu verwechseln, bei dem diverse Zellschichten innerhalb eines Dies übereinander gestapelt werden. Prinzipiell wäre eine Kombination aus 3D-NAND und TSV denkbar. Die TSV-Technik wird seit Jahren auch bei Stacked DRAM eingesetzt.

Die nun beim NAND-Flash genutzte Verbindungstechnik soll für Vorteile bei Leistung und Leistungsaufnahme sorgen. Die Rede ist von einer I/O-Datenrate von „über 1 Gbit/s“, was höher sei als bei „anderen NAND Flash-Speichern“. Zudem soll gleichzeitig die Leistungsaufnahme bei Zugriffen gegenüber Toshibas bisherigen Produkten „um etwa die Hälfte reduziert werden“. Die Versorgungsspannung wird mit 1,8 Volt (core circuits) respektive 1,2 Volt (I/O circuits) angegeben. Als geeignete Anwendungsbereiche sieht der Hersteller unter anderem Enterprise-SSDs des High-End-Bereichs. Ob sich die Herstellung von Flash-Speicher mit TSV-Technik deutlich teurer als mit der herkömmlichen „Verdrahtung“ gestaltet, bleibt zunächst als Frage im Raum.

Toshiba nennt zudem Spezifikationen zum Prototyp mit 16 Dies. Dieser soll insgesamt 256 GB Speicherkapazität aufweisen. Daraus ergibt sich eine Kapazität von 128 Gigabit pro Die – die derzeit gängige Größe bei NAND-Flash. Das gesamte BGA-Package soll eine Höhe von 1,9 Millimeter aufweisen, eine Version mit nur acht Dies bringt es auf 1,35 Millimeter. Die Fläche des Chip-Gehäuses wird bei beiden Varianten mit 14 × 18 Millimetern angegeben. Die NAND-Schnittstelle bildet wie bei Toshiba üblich das Toggle-DDR-Interface. Toshiba räumt ein, dass ein Teil der neuen Technologie auf den Errungenschaften der New Energy and Industrial Technology Development Organisation (NEDO) basiert. Die staatliche Institution fördert in Japan Forschung und Entwicklung von Technologien in diversen Bereichen.

Auf dem in der kommenden Woche startenden Flash Memory Summit soll der Prototyp vorgestellt werden.