High Bandwidth Memory: HBM2 für Nvidia Pascal von Samsung und SK Hynix

Die erste Generation des High Bandwidth Memory (HBM) wird in Grafikkarten mit AMDs Fiji-GPU eingesetzt und exklusiv von SK Hynix produziert. Erst im kommenden Jahr wird auch Samsung HBM-Speicher für Grafikkarten anbieten. Laut einem Bericht aus Korea sollen beide Unternehmen Nvidias kommende Pascal-GPUs mit HBM-Chips versorgen.

Aus Branchenkreisen will Business Korea von diesem Vorhaben erfahren haben. Demnach planen Samsung und SK Hynix den Start der Massenproduktion der zweiten Generation des HBM-Speichers (HBM2) innerhalb des ersten Quartals 2016. Zu den Abnehmern werde dann unter anderem Nvidia mit der für 2016 angekündigten GPU-Architektur Pascal zählen. Auch AMD plant neue GPUs mit „HBM2“.

Dass der Speicher auf Grafikkarten von verschiedenen Herstellern stammt, ist nicht ungewöhnlich, wird GDDR5-Speicher doch sowohl von Samsung und SK Hynix als auch von Micron verbaut. Beim potentiellen Nachfolger HBM war dies durch den Vorsprung von SK Hynix zunächst jedoch anders. Zudem wird der Speicher bisher exklusiv auf AMD-Grafikkarten eingesetzt, Nvidia hat bis heute kein Produkt mit HBM im Programm.

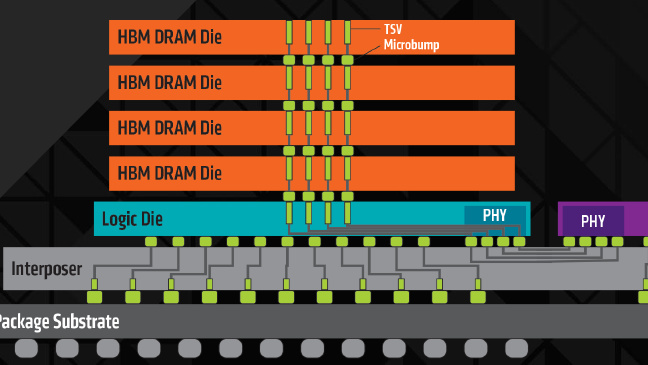

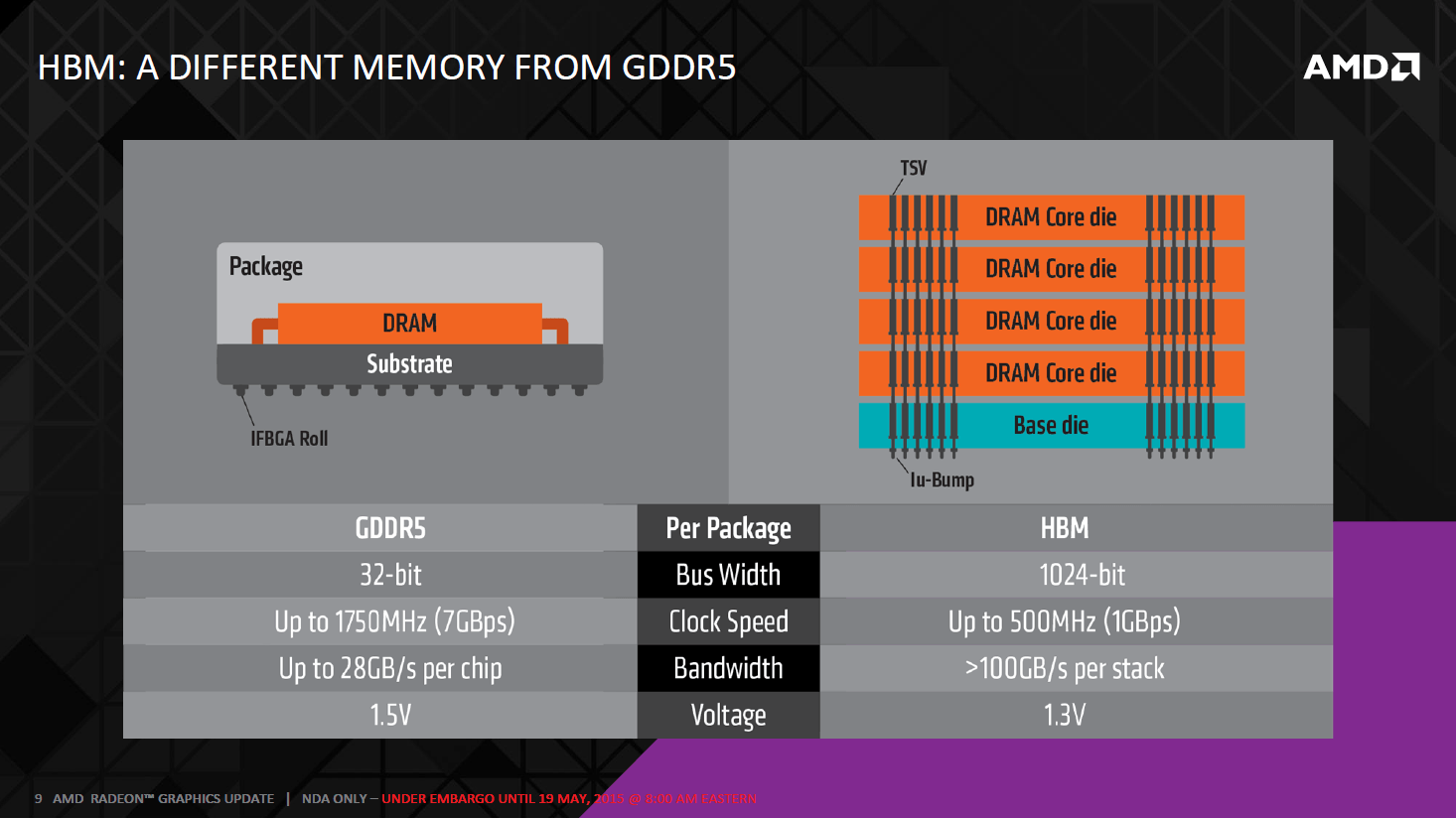

HBM beschreibt eine Speichertechnik, bei der mehrere DRAM-Schichten übereinandergestapelt und mittels TSV miteinander verbunden sind. Die HBM-Technik bietet gegenüber bisherigem Grafikspeicher Vorteile bei Datendurchsatz und Leistungsaufnahme und ermöglicht kompaktere Grafikkarten-Designs. Ein gutes Beispiel ist AMDs 15 Zentimeter kurze Radeon R9 Nano mit einer Leistung der Oberklasse.

Die erste HBM-Generation von SK Hynix bietet eine Kapazität von 1.024 MByte (8 Gbit) pro „Stapel“ (stack) wobei vier DRAM-Dies à 256 MByte (2 Gbit) übereinander gestapelt sind. Ein solcher Stapel kommuniziert mit der GPU über ein insgesamt 1.024 Bit breites Speicherinterface, das hohe Datenraten – die sogenannte Speicherbandbreite – auch bei vergleichsweise niedrigem Speichertakt realisiert. Mit nur 500 MHz Taktfrequenz – aktueller GDDR5-Speicher arbeitet mit über 3.000 MHz – liefert HBM somit eine Speicherbandbreite von 512 GByte pro Sekunde.

Für die zweite HBM-Generation hatte SK Hynix eine Vervierfachung der Kapazität auf 1.024 MByte (8 Gbit) pro DRAM-Ebene angekündigt. Beim bisherigen Design mit vier Ebenen werden dann 4 GByte pro HBM-Stapel erreicht, es soll aber auch eine Variante mit acht Ebenen und damit 8 GByte kommen. Zudem soll die mögliche Datenrate nochmals verdoppelt werden. Die gleichen Merkmale hat auch Samsung in Aussicht gestellt – was wenig wundert, ist HBM doch ein JEDEC-Standard.

Micron hat bisher keine Pläne für HBM geäußert und stattdessen eine Weiterentwicklung des planaren GDDR5-Speichers als GDDR5X angekündigt. Mit verdoppeltem Prefetch soll die Datenrate deutlich gesteigert werden.