AMD Zen: Ein MCM mit 2 × 16 Kernen und 2 × Quad-Channel-DDR4

Die Annahme, dass AMD bei den neuen Zen-Prozessoren bis zu 32 Kerne bieten wird, erhält weitere Unterstützung. Zumindest teilweise wird AMD dabei erneut auf ein Multi-Chip-Module-Design (MCM) zurückgreifen, wie auf einer Präsentation im Rahmen des IT Technical Forum des CERN Data Centre bekannt wurde.

Der CERN-Forscher Liviu Vâlsan sprach bei der Präsentation Technology and Market Trends for the Data Centre auch kurz über AMDs kommende CPU-Architektur Zen. Der gesamte Vortrag ist als Video über den Dokumenten-Service von CERN abrufbar.

Eine Grafik beschreibt, dass Zen über bis zu 32 Kerne verfügen wird. Dass AMD bei der Architektur erstmals Simultaneous Multi-Threading (SMT) nutzt, ist bereits bekannt. Ferner wird DDR4-Unterstützung mit acht Kanälen aufgeführt.

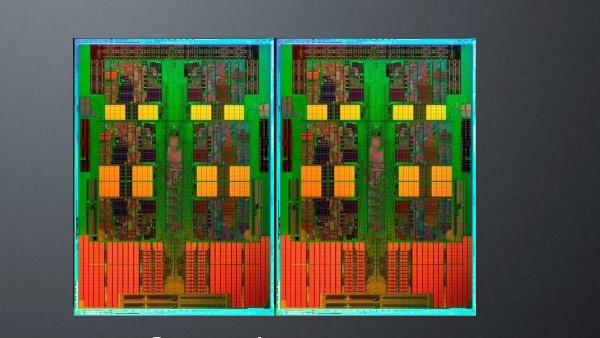

Zwei große CPUs ergeben eine sehr große

Erst die Erläuterungen von Vâlsan verraten, was sich hinter den 32 Kernen und dem vermeintlichen Acht-Kanal-Speicherinterface verbirgt. Demnach nutzt AMD wie schon früher bei Opteron-Prozessoren das MCM-Prinzip und bringt zwei CPUs in einem Chip unter. Im Grunde handelt es sich also um zwei 16-Kern-CPUs mit Vier-Kanal-Speicherinterface: 2 × 16 macht 32 Kerne und 2 × 4 macht acht DDR4-Kanäle. Damit erhält auch der jüngste Hinweis auf das Vorhandensein von CPUs mit bis zu 32 Zen-Kernen mehr Gewicht.

Der Sprecher erklärt, dass AMD zur Verbindung der beiden CPUs den gleichen Interconnect wie bei einem Zwei-Sockel-System nutzt. Früher hieß diese Verbindung HyperTransport-Link. So wurden zum Beispiel bei den Opteron 6200 zwei CPU-Dies der Bulldozer-Architektur zu einem Prozessor mit insgesamt acht Modulen und 16 Integer-Kernen zusammengesetzt, aus dem Dual-Channel-Speicherinterface wurde eines mit vier Kanälen.

Zen dürfte auf einen neuen HyperTransport-Link setzen

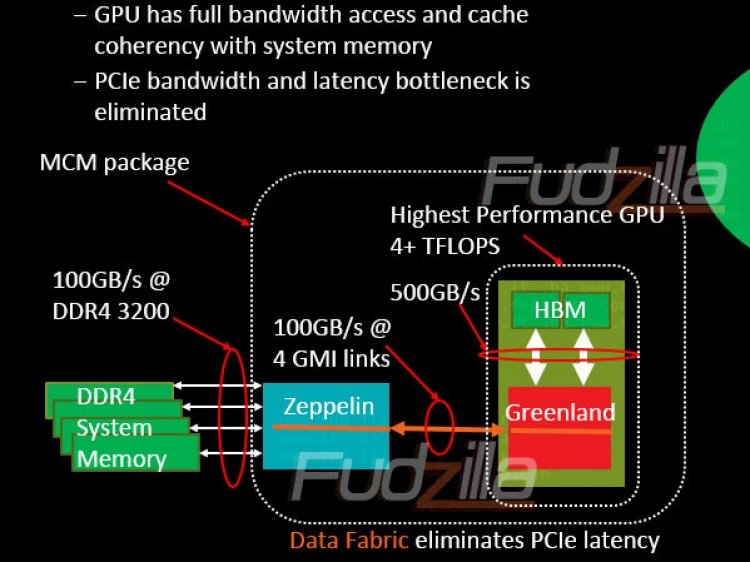

Mit Zen wird allerdings ein Nachfolger des HyperTransport-Links erwartet. Es wird schon lange über eine Interconnect-Technik von AMD spekuliert. Fudzilla veröffentlichte bereits im letzten Jahr eine Grafik von einem Global Memory Interconnect (GMI), das eine Datenübertragungsrate von 100 GB/s über vier Links ermöglicht – vier Links bieten die aktuellen MCM auch, jedoch nur mit jeweils 6,4 GT/s. Dabei war jedoch von einer APU mit Zeppelin-CPU und Greenland-GPU als MCM die Rede. Die GMI-Links sollen demnach sowohl für die Kommunikation zwischen CPU und GPU als auch extern mit dem Speicher genutzt werden.

Eine APU mit 32 Kernen für High Performance Computing (HPC) war auch bereits Thema eines offiziellen AMD-Dokuments.