ISSCC: Microns 768-Gbit-NAND-Flash erreicht 2,77 Tbit/Zoll²

Auf der ISSCC 2016 wurde unter anderem auch über die NAND-Flash-Fertigung und deren Zukunft gesprochen. Bei Microns Präsentation stand ein neuer Meilenstein auf dem Weg zu einer höheren Speicherdichte im Vordergrund: Ein erster Flash-Chip mit 768 Gigabit wurde entwickelt.

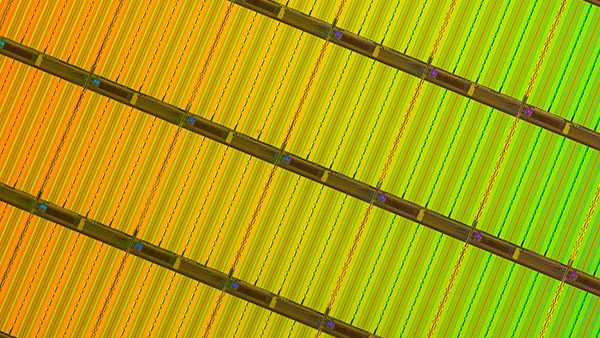

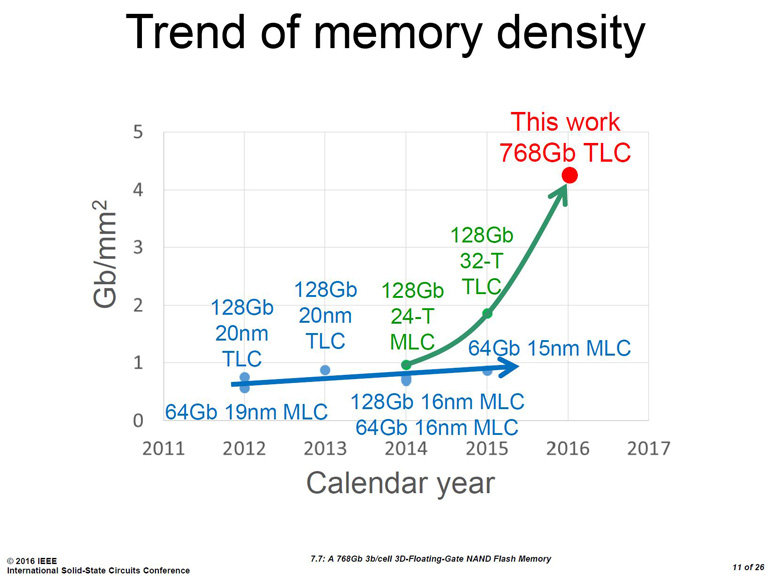

Noch handelt es sich dabei nicht um ein fertiges Produkt, das schon bald auf den Markt kommt. Vielmehr hätten die Verantwortlichen bei Micron noch gar nicht entschieden, ob der Chip in der Form in die Massenfertigung geht. Dennoch soll die Entwicklung zeigen, was mit 3D-NAND in Zukunft alles möglich ist. Mit 768 Gigabit übertrifft der Micron-Chip das derzeit verfügbare Maximum von 256 Gbit Speicherkapazität um das Dreifache. Die Daten werden mit drei Bit pro Zelle gesichert, womit es sich um TLC-NAND handelt.

-

Micron arbeitet an 3D-TLC-NAND mit 768 Gbit (Bild: ZDNet)

Micron arbeitet an 3D-TLC-NAND mit 768 Gbit (Bild: ZDNet)

Samsung als Marktführer hat bereits die dritte Generation des V-NAND genannten 3D-NAND am Markt. Die TLC-Chips speichern auf 48 Zellebenen 256 Gigabit an Daten. Laut ZDNet besitzt ein Chip eine Fläche von 97,6 mm². Umgerechnet in die bei Festplatten gängige Einheit beträgt die Datendichte 1,69 Terabit pro Quadratzoll.

Microns Musterchip ist mit 179,2 mm² in der Fläche gegenüber aktuellen NAND-Chips vergleichsweise riesig, auch wenn es früher noch weitaus größeren Flash gegeben hat. Dennoch fällt dank 768 Gbit die Datendichte mit 2,77 Terabit pro Quadratzoll nochmals deutlich höher aus als bei Samsungs jüngster Generation. Der Vergleich mit Microns weit verbreiteten 128-Gbit-MLC-Chips der 16-nm-Generation, die es auf nur 0,56 Tbit/Zoll² bringen, verdeutlicht den Vorsprung bei der Datendichte.

| Produkt | Fläche | Dichte |

|---|---|---|

| Samsung V-NAND 128 Gbit MLC 24 Layer | 133 mm² | 0,62 Tbit/Zoll² 0,96 Gbit/mm² |

| Samsung V-NAND 128 Gbit TLC 32 Layer | 68,9 mm² | 1,19 Tbit/Zoll² 1,84 Gbit/mm² |

| Samsung V-NAND 256 Gbit TLC 48 Layer | 97,6 mm² | 1,69 Tbit/Zoll² 2,62 Gbit/mm² |

| Micron 2D-NAND 128 Gbit MLC | 147 mm² | 0,56 Tbit/Zoll² 0,87 Gbit/mm² |

| Micron 3D-NAND 768 Gbit TLC (WIP) | 179,2 mm² | 2,77 Tbit/Zoll² 4,29 Gbit/mm² |

EE Times bestätigt in einem Bericht die Angaben zu Fläche und Datendichte und nennt weitere Details. Demnach besitzt Microns 768-Gbit-Chip eine erheblich höhere Geschwindigkeit beim Lesen von Daten: 800 MByte/s sollen 178 MByte/s bei Samsungs aktueller Generation gegenüber stehen. Dafür könnten Daten aber nur mit 44 statt 53 MByte/s geschrieben werden. Eine „Achillesferse“ des neuen Micron-Chips sei, dass zumindest aktuell vergleichsweise große Blöcke von 96 MByte genutzt werden, die sich nicht partiell löschen beziehungsweise beschreiben lassen.

Auch Toshiba und Samsung peilen 768 Gbit und mehr an

Laut EE Times hat auch Toshiba entsprechende Pläne. Der 3D-Speicher, den Toshiba BiCS nennt, stehe als TLC-3D-NAND mit 768 Gbit für 2017 auf der Roadmap. 2018 soll bereits ein Chip mit 1 Terabit Kapazität vorgesehen sein. Wie so oft ist ein solcher Ausblick in die Zukunft mit Vorsicht zu genießen, denn neue Technologien kommen oftmals später als im Zeitplan vorgesehen auf den Markt. Toshibas erste kommerzielle 3D-NAND-Generation lässt zudem weiter auf sich warten.

Samsung ist inzwischen bei 48 Zellschichten angekommen und prognostiziert, dass der V-NAND auch über 100 Lagen erreichen könnte und potentiell ebenfalls zu Flash-Chips mit 1 Terabit oder mehr führen werde.

Floating Gate versus Charge Trap

Intel und Micron, die bei 3D-NAND gemeinsame Wege gehen, setzen auf die altbewährte Floating-Gate-Technik, während Samsung und andere für 3D-NAND die jüngere Technik Charge Trap Flash (CTF) nutzen. Floating Gates werden schon lange für NAND-Flash genutzt und bedeuten gegenüber CTF Kostenvorteile bei der Fertigung. Allerdings ermöglicht CTF durch die spezielle Schicht (Trapping Layer) aus Siliciumnitrid engere Strukturen und damit eine höhere Datendichte pro Chipfläche.

Micron fährt allerdings eine Strategie, um diesem Nachteil entgegen zu wirken: NAND-Flash besteht nicht nur aus dem für Daten nutzbaren Teil, der mit Größen wie 128, 256 oder 768 Gbit angegeben wird, sondern benötigt zusätzliche Schaltungen um ordnungsgemäß zu funktionieren und für Langlebigkeit zu sorgen. Dieser als logic circuitry beschriebene Overhead benötigt ebenfalls Platz und nimmt einen gewissen Teil der Chipfläche ein. Beim 3D-NAND nutzt Micron die dreidimensionale Struktur und bringt diesen Ballast zu einem großen Teil in einer separaten Ebene unter, die sich unter den darüber liegenden Zellschichten befindet. Im Micron-Blog beschreibt Kevin Kilbuck diese Maßnahme mit dem Beitrag CMOS under the Array. Demzufolge ist Micron der einzige Hersteller, der diesen Weg bei 3D-NAND geht.

Ob letztlich Microns Floating-Gate-Ansatz mit eigener Logikebene oder die Charge-Trap-Techniken der Konkurrenz langfristig besser aufgestellt sind, lässt sich momentan noch nicht absehen. Zunächst werden beide existieren.

Intels und Microns 3D-NAND-Debüt soll in diesem Jahr mit 32 Lagen und 256 Gbit (MLC) beziehungsweise 384 Gbit (TLC) den Markt erreichen. Auch Toshiba und SanDisk sowie SK Hynix stehen vor der Markteinführung ihres ersten kommerziellen 3D-NAND. Samsungs dritte Generation mit 256 Gbit wird bereits seit über einem halben Jahr in Serie gefertigt.

| 3D-NAND | Ebenen | Kapazität | Produktion/Verfügbarkeit |

|---|---|---|---|

| SK Hynix 3D NAND | 36 | 128 Gbit (MLC mit 2 Bit/Zelle) | Q4 2015 / 2016 |

| SK Hynix 3D NAND | 48 | 256 Gbit (TLC mit 3 Bit/Zelle) | Q1 2016 / ? |

| Samsung V-NAND Gen 3 | 48 | 256 Gbit (TLC mit 3 Bit/Zelle) | August 2015 / ? |

| Samsung V-NAND Gen 2 | 32 | 86/128 Gbit (MLC mit 2 Bit/Zelle) 128 Gbit (TLC mit 3 Bit/Zelle) |

Mai 2014 / H2 2014 |

| Samsung V-NAND Gen 1 | 24 | 128 Gbit (MLC mit 2 Bit/Zelle) | August 2013 / H2 2013 |

| Toshiba/SanDisk BiCS | 48 | 128 Gbit (MLC mit 2 Bit/Zelle) | H2 2015 / 2016 |

| Toshiba/SanDisk BiCS | 48 | 256 Gbit (TLC mit 3 Bit/Zelle) | H1 2016 / 2016 |

| Intel/Micron 3D NAND | 32 | 256 Gbit (MLC mit 2 Bit/Zelle) 384 Gbit (TLC mit 3 Bit pro Zelle) |

Q4 2015 / 2016 |

| Stand: Oktober 2015 | |||