Moore's Law lebt (noch): Skalierung von sechs Intel-CPU-Generationen im Detail

Moore's Law ist tot – diese Aussage kommt spätestens alle drei Jahre wieder. Doch Moore's Law spricht nicht davon, dass alles stetig rapide schneller wird, sondern von der Technik dahinter und dem Preis dafür. Der Blick darauf zeigt, dass Moore's Law aktuell noch immer Bestand hat. Ein Vergleich von sechs CPU-Generationen.

Im Rahmen eines großen Workshops hatte Intel ComputerBase Anfang März nach Hillsboro, Oregon, geladen. Im Gespräch mit vielen Intel-Mitarbeitern aus dem Server-Bereich aber auch Journalisten aus aller Welt kam immer wieder die Aussage auf, dass die Nehalem-Plattform der Grundstein für das heute extrem erfolgreiche Server-Geschäft ist. Damals hatte Intel unzählige Neuheiten eingeführt, allen voran den Speichercontroller in die CPU integriert, der altbekannte Frontside-Bus und die Northbridge wurde zu Grabe getragen.

Die damalige komplette Neuausrichtung der Architektur war Ende 2008 der Grundstein für alle Prozessoren, die daraufhin bis heute erschienen sind. Jede hat auf den Ursprung noch etwas drauf gesetzt, Moore's Law wurde nahezu so umgesetzt, wie es im Buch steht. Etwas über sieben Jahre später ist nun der fünfte Nachfolger der Nehalem-Architektur als Vollausbau Broadwell-EP und später auch Broadwell-EX marktreif – mit sechs Mal so vielen Kernen und fast zehn Mal so vielen Transistoren (verglichen mit dem EP-Modell, Nehalem-EX erschien erst im März 2010). Moore's Law besagt, dass sich binnen zwei Jahren die Transistorzahl verdoppelt – dies geschieht in der Regel bei einem Sprung in eine neue Fertigung.

Sechs Generationen High-End-CPUs von Intel im Detail

| Modellserie | Fertigungstechnik | Kerne | Die-Fläche | Transistoren |

|---|---|---|---|---|

| Nehalem-EP (Gainestown/Bloomfield) | 45 nm HKMG | 4 | 263 mm² | 731 Mio. |

| Nehalem-EX (Beckton) | 45 nm HKMG | 6 – 8 | 684 mm² | 2,3 Mrd. |

| Westmere-E/EN/EP (Gulftown) | 32 nm HKMG | 4 – 6 | 248 mm² | 1,17 Mrd. |

| Westmere-EX | 32 nm HKMG | 8 – 10 | 513 mm² | 2,6 Mrd. |

| Sandy Bridge-E/EN/EP | 32 nm HKMG | 4 | 295 mm² | 1,27 Mrd. |

| Sandy Bridge-E/EN/EP | 32 nm HKMG | 6 – 8 | 435 mm² | 2,27 Mrd. |

| Ivy Bridge-E/EN/EP | 22 nm FinFET | 4 – 6 | 256,5 mm² | 1,86 Mrd. |

| Ivy Bridge-EN/EP | 22 nm FinFET | 8 – 10 | 341 mm² | 2,89 Mrd. |

| Ivy Bridge-EP/EX | 22 nm FinFET | 12 – 15 | 541 mm² | 4,31 Mrd. |

| Haswell-E/EN/EP | 22 nm FinFET | 4 – 8 | 354 mm² | 2,60 Mrd. |

| Haswell-EN/EP | 22 nm FinFET | 10 – 12 | 492 mm² | 3,84 Mrd. |

| Haswell-EP/EX | 22 nm FinFET | 14 – 18 | 662 mm² | 5,69 Mrd. |

| Broadwell-E/EN/EP | 14 nm FinFET | 4 – 10 | 246 mm² | 3,4 Mrd. |

| Broadwell-EN/EP | 14 nm FinFET | 12 – 15 | 306 mm² | 4,7 Mrd. |

| Broadwell-EP/EX | 14 nm FinFET | 16 – 24 | 456 mm² | 7,2 Mrd. |

Dass das alle Jahre wieder totgesagte Moore's Law in diesem Segment immer noch funktioniert, zeigt der Vergleich zwischen den Serien. Der Vollausbau der Broadwell-EP/EX-Prozessoren bietet Platz für 24 Kerne auf 456 mm² und belegt damit knapp 69 Prozent Platz des Vorgängers, der aber nur Platz für 18 Kerne bot – die theoretische Skalierung von 22 auf 14 nm ist in dem Bereich damit nahezu perfekt umgesetzt. Der erweiterte Blick auf den 12-Kern-Vorgänger auf 492 mm² Fläche zeigt sogar ein noch besseres Verhältnis, in dem Fall hat Intel Lücken in den Dies geschlossen und den Platz optimaler genutzt als zuvor.

Nicht weniger interessant sind die Vergleiche mit noch älteren Modellen: Sandy Bridge-E mit vier Kernen und 10 MByte L3-Cache belegte seinerzeit fast 300 mm² Fläche, heute gibt es da 15 Kerne und 37,5 MByte L3-Cache. Der kleine Sandy Bridge-E war seinerzeit aber auch kein gutes Beispiel für viel Technik auf kleinem Raum, das große EP-Modell war dort deutlich besser. Ein theoretischer Sandy Bridge-EX mit zwölf oder noch mehr Kernen wäre aber in jedem Fall ein Riese mit über 600 mm² Fläche geworden.

Grafiken sprechen mehr als Worte

In einem Balkendiagramm wird das noch deutlicher, da gleichzeitig der prozentuale Abstand inkludiert ist. Rein allein auf die Die-Fläche und die Anzahl der Kerne bezogen hat sich extrem viel getan, insbesondere auch in Bereichen, in denen in Annahme bestand, dort würde schon extrem gutes Material vorliegen. Der Vollausbau von Broadwell-EP mit 24 Kernen geht in dem Diagramm im oberen Mittelfeld unter, flächenmäßig knapp über dem Sandy Bridge-EP mit acht Kernen.

Im Streudiagramm wird deutlich, welche Prozessoren zu welchem Fertigungsschritt gehören, denn diese sammeln sich auf einer Linie. Der markierte 18-Kern-Haswell-EX ist in 22 nm gefertigt, rund um die Linie versammelt sich alle drei Ivy-Bridge-EP-Varianten (IVB) und die weiteren Haswell-EP-Vertreter (HSW) – alle nutzen ebenfalls die 22-nm-Fertigung (grün markierte Elemente). Der Mausklick auf einen Sandy-Bridge-Vertreter (SNB) offenbart das gleiche Spiel bei der 32-nm-Fertigung (blau markiert).

Das Spiel lässt sich aber noch einen Schritt weiter treiben. Das folgende Diagramm zeigt das bereits errechnete Verhältnis der Die-Fläche zu den darauf verbauten Transistoren. Heraus kommt ohne die doppelten Prozesse bei 32 und 22 nm das bekannte Schaubild.

Die Linie ist eine alte bekannte, wenngleich sie von Herstellern immer unter der Bestimmung einer normierten SRAM-Zelle aufgestellt wird und nicht einen komplett funktionstüchtigen großen Prozessor-Die berücksichtigt. Doch dass die Theorie der Praxis sehr nah kommt, lässt sich daraus bereits ableiten. Zu sehen ist aber auch, dass die Linie zu einer leichten Kurve wird, wenngleich immer erst der zweite Prozessor von Intel in der gleichen Fertigungsweise noch etwas besser ist als der vorangegangene, weshalb in den Diagramm mit Haswell und Sandy Bridge bereits die jeweils zweite Generation in gleicher Fertigungsweise berücksichtigt ist.

Moore's Law lebt (noch)

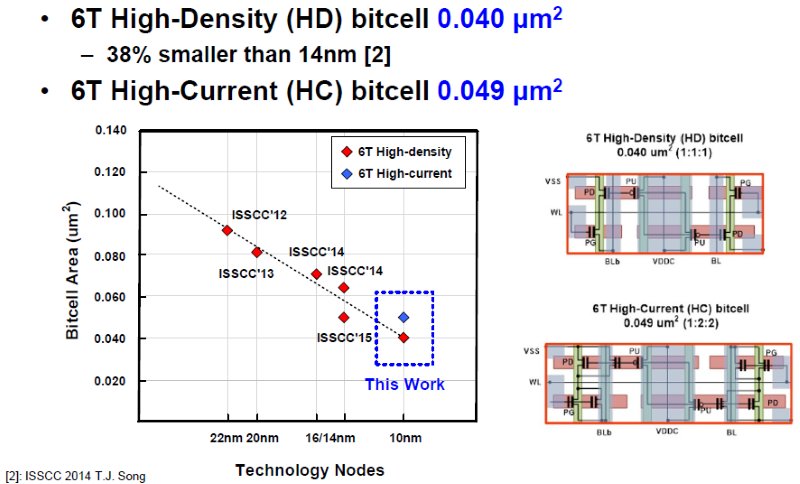

Das primär von den Medien in den letzten Jahren regelmäßig totgesagte „Gesetz“, welches nur die Integrationsdichte der Transistoren in einer begrenzten Fläche bei gleichbleibenden Preisen beschreibt und nicht, dass die Produkte immer schneller werden respektive höher takten, lebt nach wie vor und wird es zumindest auch noch in der nahen Zukunft, wenn es an die 10- und 7-nm-Fertigung geht. Samsung lies bereits vor einigen Wochen einen Blick auf die Skalierung eine SRAM-Zelle in 10-nm-Fertigung zu, die exakt dort liegt, wo sie sein sollte.

Gordon Moore als Urheber dieses Gesetzes selbst sagte bereits 2007 und noch einmal 2015 ein mögliches Ende des Gesetzes in der nächsten Dekade (bis 2025) voraus. Dann ist die Fertigungstechnik bei mindestens 5 nm angelangt, die Strukturen werden bei 2 und 3 nm extrem klein, sodass sich einigen physikalischen Grenzen genähert wird. Die Entwicklung nimmt dementsprechend immer mehr Zeit und Geld in Anspruch, Intel selbst hat die Einführung seines neuen Fertigungsschrittes deshalb verzögert und das eigene Tick-Tock-Modell beerdigt. Gordon Moore's Law würde dem Anschein nach so auf 2,5 Jahre verlängert, doch es wäre nicht die erste Anpassung seines Gesetztes: Ursprünglich sollte die Verdoppelung jedes Jahr eintreten, später wurden oft 18 Monate genannt. Doch das Gesetz ist nicht an Intel gebunden, sondern allgemeingültig geworden. Auf der anderen Seite ziehen beispielsweise TSMC & Co. das Tempo an und forcieren die Entwicklung aktuell massiv in Richtung 7 und auch bereits 5 nm – Moore's Law lebt (noch).