Hot Chips 28: Micron über DRAM, Flash, 3D XPoint und HBM als HMC-Kopie

Sonntagmorgen im Flint Center in Cupertino, die Hot Chips 28 startet mit einer Vormittagsveranstaltung über Speicher. Dabei geht es um alle aktuellen Technologien, von klassischem DRAM und Flash, von HMC bis hin zu GDDR5X und das, was in Zukunft kommen könne: DDR5, 3D XPoint & Co. Und das alles mit extrem viel Ehrlichkeit.

Die erste Präsentation der Veranstaltung dieses Jahres ging an Micron. Der Speicherhersteller ging gleich zu Beginn mit einigen Buzzwords wie IoT und Zahlen ins Gericht, unter anderem auch der von Intel stetig genannten „50 Milliarden vernetzten Geräten im Jahre 2020“ – wenn es 20 Milliarden sein werden, wäre das schon viel, erklärte Micron bei Hot Chips 28. Die erfrischend ehrlichen Worte ging auch an anderer Stelle weiter, selbst bei eigenen Produkten: 3D XPoint. Dort erklärte der Speicherhersteller, dass man (mit dem Fingerzeig auf Intel) viel zu früh mit der Technik an die Öffentlichkeit gegangen ist, die Serienproduktion frühestens Ende dieses Jahres starten werde.

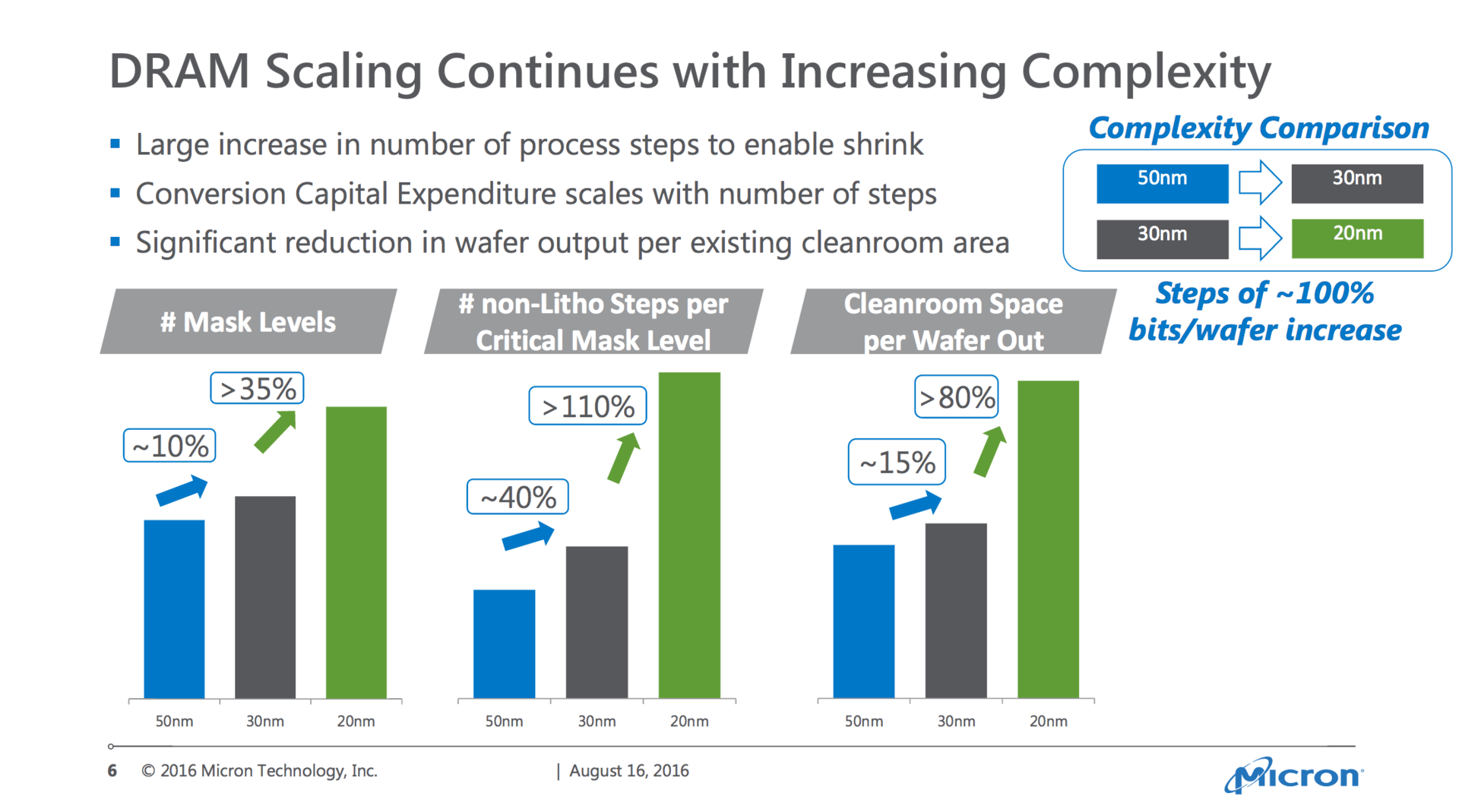

J. Thomas Pawlowski, Fellow & Chief Technologist in Micron’s Architecture Development Group erklärte anhand von einige Beispielen die Herausforderungen von der Weiterentwicklung von DRAM. Mit jedem Schritt wird es nicht nur komplizierter, auch steigt die benötigte Fläche an Reinraum und das Arbeitsmaterial deutlich an, selbst um nur den gleichen Ausstoß an Wafern wie zuvor beizubehalten. Erneut wies auch Micron darauf hin, dass die Bezeichnungen der Fertigungen Schall und Rauch sind. Die 10Y getaufte Fertigung bei Speicher werde beispielsweise nicht einmal ansatzweise 15 nm erreichen; und dies nur auf der Logic-Seite.

Micron: HBM ist eine schlechte Kopie von HMC

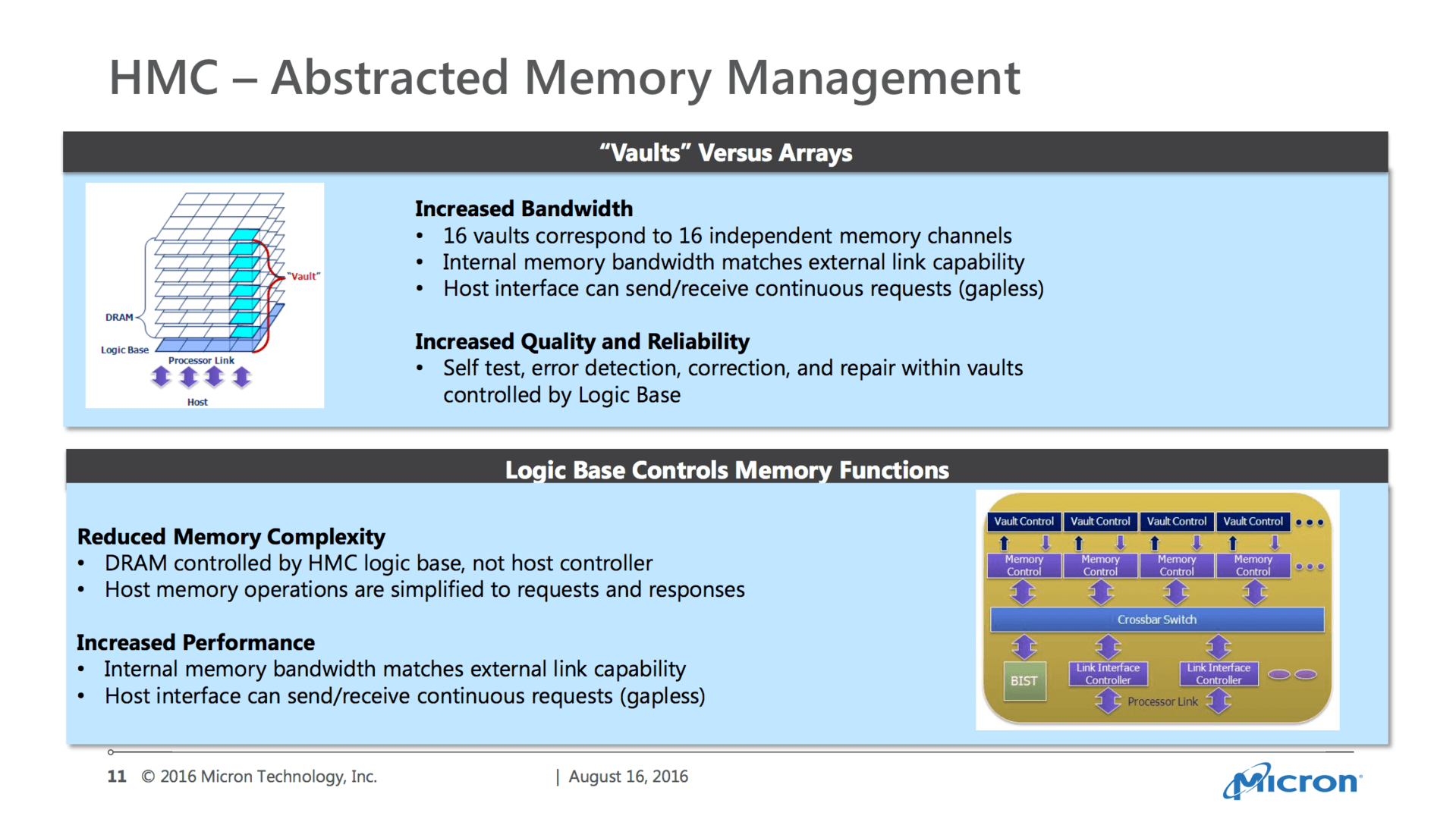

Wenig, respektive gar kein positives Wort verlor Micron über High Bandwidth Memory (HBM). Diese bezeichnete Pawlowski als schlechte Kopie des eigenen Standards HMC, der im Jahre 2011 auf einer Hot-Chips-Veranstaltung enthüllt wurde. Die zweite Generation von Hybrid Memory Cube sei in Produktion, mit vielen Features, die HBM außerhalb von Bandbreite gar nicht bieten kann. Eine Vergleichsfolie von HMC vs. HBM lehnte Micron ab und erklärte dies mit den Worten, „it's like beating up a kid and taking the candy“. Der Konter von der HBM-Fraktion folgte kurze Zeit später.

DDR5: Sampling ab 2018, Produktion frühestens ab 2019

Auch zum kommenden Next-Gen-Speicherstandard verlor Micron einige Worte. Da der Standard der JEDEC unterliegt, sei es vorab nicht erlaubt, Details dazu preiszugeben, wenn dieser noch in der Entwicklung ist. Doch die Ziele sind im Grunde genommen klar: Der Basisstandard dürfte DDR5-3.200 sein, mit Ausbaumöglichkeiten bis DDR5-6.400, die Standardspannung 1,1 Volt betragen. Einige Optimierungen werden natürlich mit im Gepäck sein, unterm Strich soll die Bandbreite des aktuellen DDR4-Standards verdoppelt werden.

Für das Jahr 2018 erwartet Micron das Sampling von DDR5, frühestens 2019 einen angehenden Start der Serienfertigung. Realistischer ist jedoch 2020+, denn wie üblich werde dies nicht über Nacht geschehen, erklärte der Mann der offenen Worte mit den Blick auf die DDR3-Fertigung, die immer noch in High Volume Production ist, obwohl DDR4 nun in jedem Markt präsent ist.