IBM Power9: Prozessor mit 24 Kernen und 8 Mrd. Transistoren im Detail

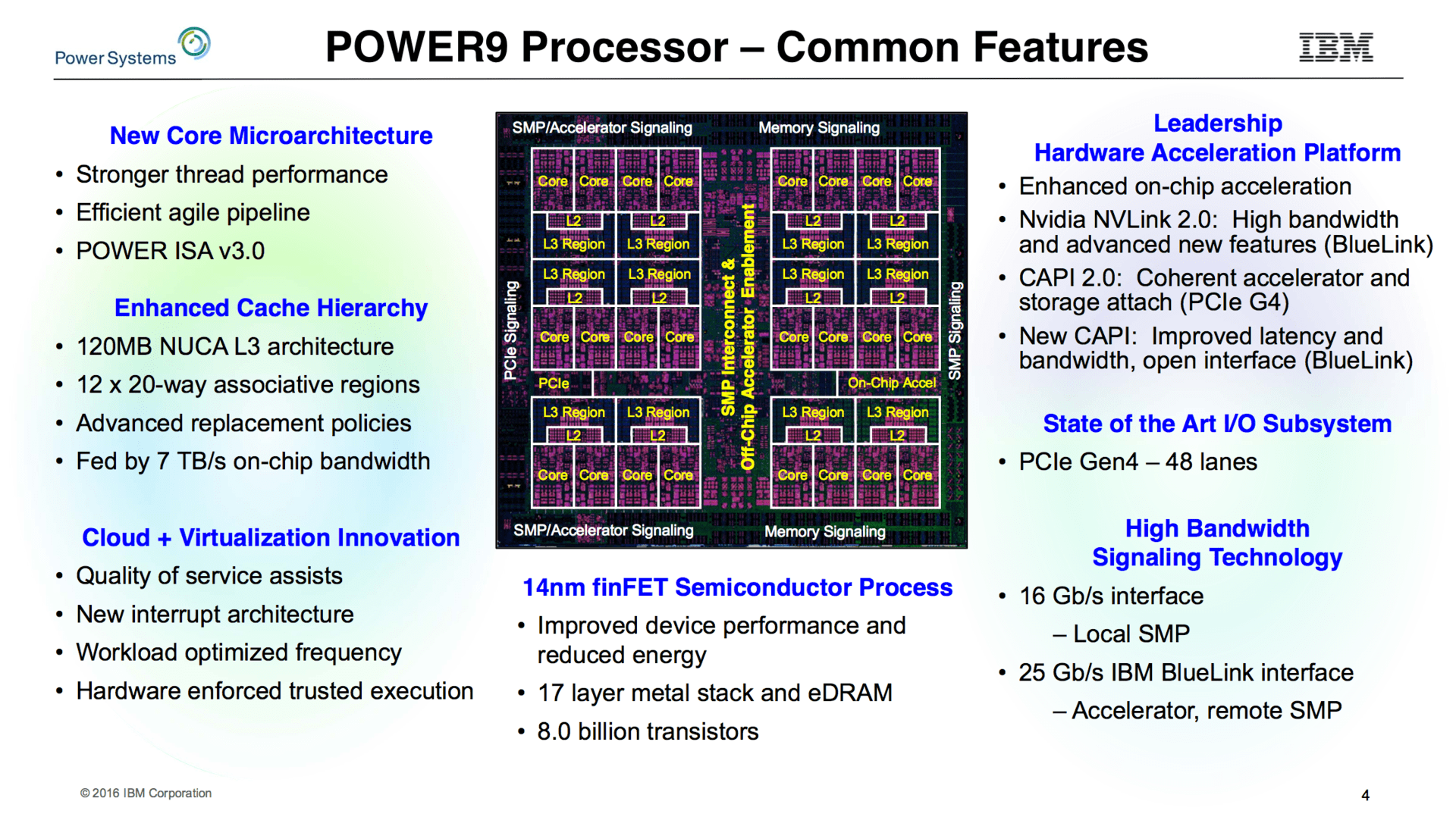

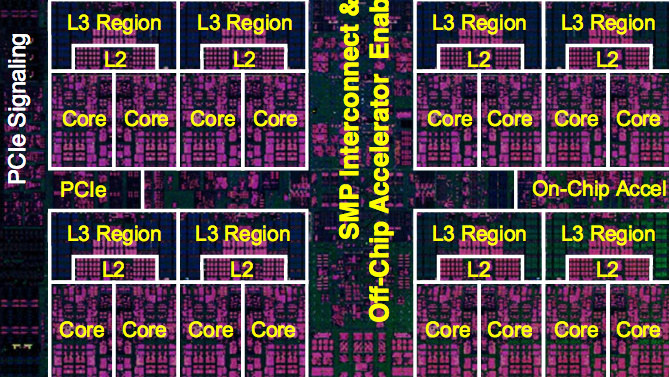

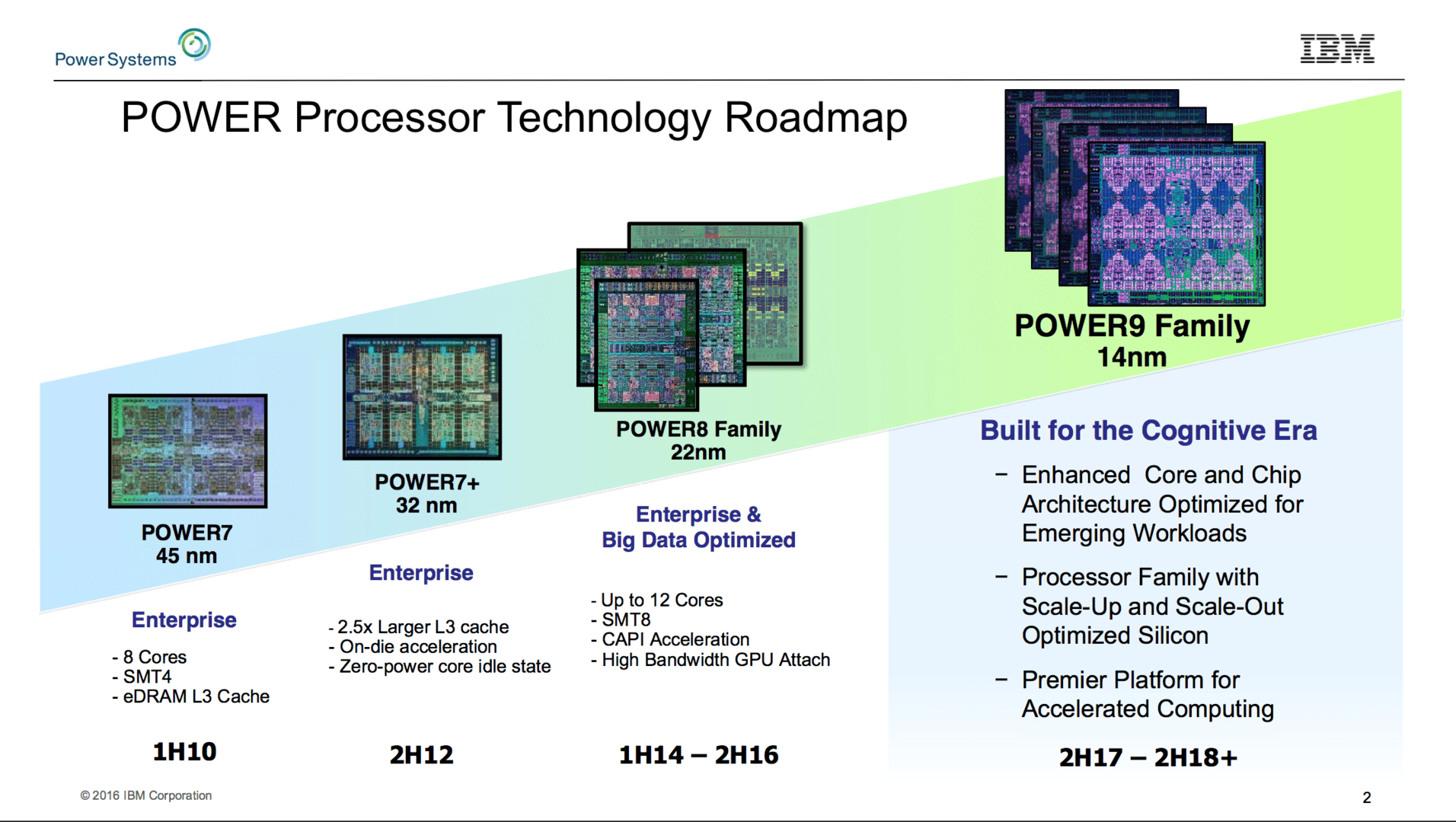

IBM hat zur Hot Chips 28 technische Details zum neuen Power9-Prozessor veröffentlicht. Das 24-Kern-Design mit bis zu achtfacher SMT-Unterstützung wird in einem modernen 14-nm-Prozess gefertigt, bietet bis zu 120 MByte L3-Cache und 48 Lanes nach neuem PCI-Express-4.0-Standard.

Mehr Offenheit im Wettkampf mit Intel Xeon

In der Vergangenheit hielt sich IBM stets sehr bedeckt mit Roadmaps und technischen Informationen zu ihren Produkten. Doch um gegen Intels Xeon-Übermacht in nahezu allen Bereichen des Rechenzentrums zu bestehen, ist nun auch Big Blue ein wenig offener geworden. Denn die Xeon gilt es zu schlagen, Intel hatte zuletzt ohnehin nur noch IBM als letzten verbliebenen Mitbewerber im High-End-Markt als Konkurrenten erkannt und über eigene Benchmarks angegriffen.

Frühestens Mitte/Ende 2017 wird IBMs neues Flaggschiff den Markt erreichen. Dann bringt es aber alles das mit, was zu einem State-of-the-Art-Prozessor für das High-End-Segment gehört. 24 Kerne mit vier- oder achtfachem Simultaneous Multithreading (SMT), große Caches (eDRAM) und PCI Express 4.0, welches im kommenden Jahr als Standard finalisiert werden soll, sind dann bereits mit von der Partie. Eine weitere Besonderheit sind die vielfältigen Anschlussmöglichkeiten unter anderem für Nvidias NVLink 2.0 und CAPI 2.0 (coherent accelerator processor interface); eine Schnittstelle, die auf kurzem und sehr schnellem Wege FPGAs, ASICs und selbst zukünftige technische Neuheiten wie Phase Change Memory (PCM) unterstützen kann.

NVLink 2.0 steht dabei im medialen Fokus, dieses soll bereits 2018 im Supercomputer Summit zum Einsatz kommen. Dort sollen insgesamt rund 3.400 Compute Nodes mit mehreren CPUs pro Node und mehreren Nvidia-Volta-Grafikkarten zum Einsatz kommen und insgesamt über 200 PetaFLOPS liefern.

Wie im Rechenzentrum üblich, wird großen Wert auf Skalierbarkeit gelegt. Power9 wird es deshalb in zwei Varianten für vier Einsatzbereiche geben: für das klassische Dual-Sockel-System oder als Scale-up-Variante für den Einsatz vieler Kerne mit riesigen Speichermengen und dem Bedarf nach hoher Bandbreite. Pro Prozessorsockel werden dann bis zu 8 TByte Speicher unterstützt, die Bandbreite liegt bei sehr hohen 230 GByte/s – das Basismodell bietet noch bis zu 4 TByte DDR4-2666. Die Grundkonfiguration teilt sich in SMT4 und SMT8 auf, das Design ist modular aufgebaut, sodass vieles identisch ist.

Kerne mit neuer Architektur

Die CPU-Kerne basieren auf einer neuen Architektur, die höhere Leistung verspricht. Auch bei IBM fängt dies natürlich bei der Sprungvorhersage an, stolz ist IBM auf die deutlich verkürzte Pipeline im Vergleich zum Power8. Schnelle L1- und L2-Caches gepaart mit dem großen L3-Cache sollen für Bandbreite in allen Bereichen sorgen – eine der Herausforderungen eines jeden Prozessors heutzutage. Dabei hilft auch das Acht-Kanal-Speicherinterface in der Scale-out-Variante und in der Scale-up-Version über einen Buffer eine nochmals fast verdoppelte Speicherbandbreite.

Doch der Prozessor hat es auch in anderer Hinsicht in sich. Acht Milliarden Transistoren schwer ist das Design, 17 Metal Layer sind in der aufwendigen 14-nm-Fertigung (14nm HP) nötig. Damit stellt IBM die eigene Fertigung, die seit kurzer Zeit bei Globalfoundries läuft, vor anspruchsvolle Aufgaben, die der neue Auftragsfertiger auch an anderer Stelle meistern muss: Naples, AMDs 32-Kern-Prozessor, soll sprichwörtlich gleich nebenan gefertigt werden.

IBM schielt explizit auch nach China

Die Zielgruppe sind dabei nicht nur westliche Unternehmen, sondern insbesondere auch jene in China, unter anderem als Teil des Open Compute Project (OCP), was von IBM vor drei Jahren mit ins Leben gerufen wurde. In diesem können die lokalen Lizenznehmer die Power9-Architektur modifizieren, beispielsweise bei den Sicherheits-Features. Dort können die „amerikanischen“ gegen eigene Lösung ausgetauscht werden.