Micron: 3D-NAND mit UFS 2.1 und LPDDR4x für Smartphones

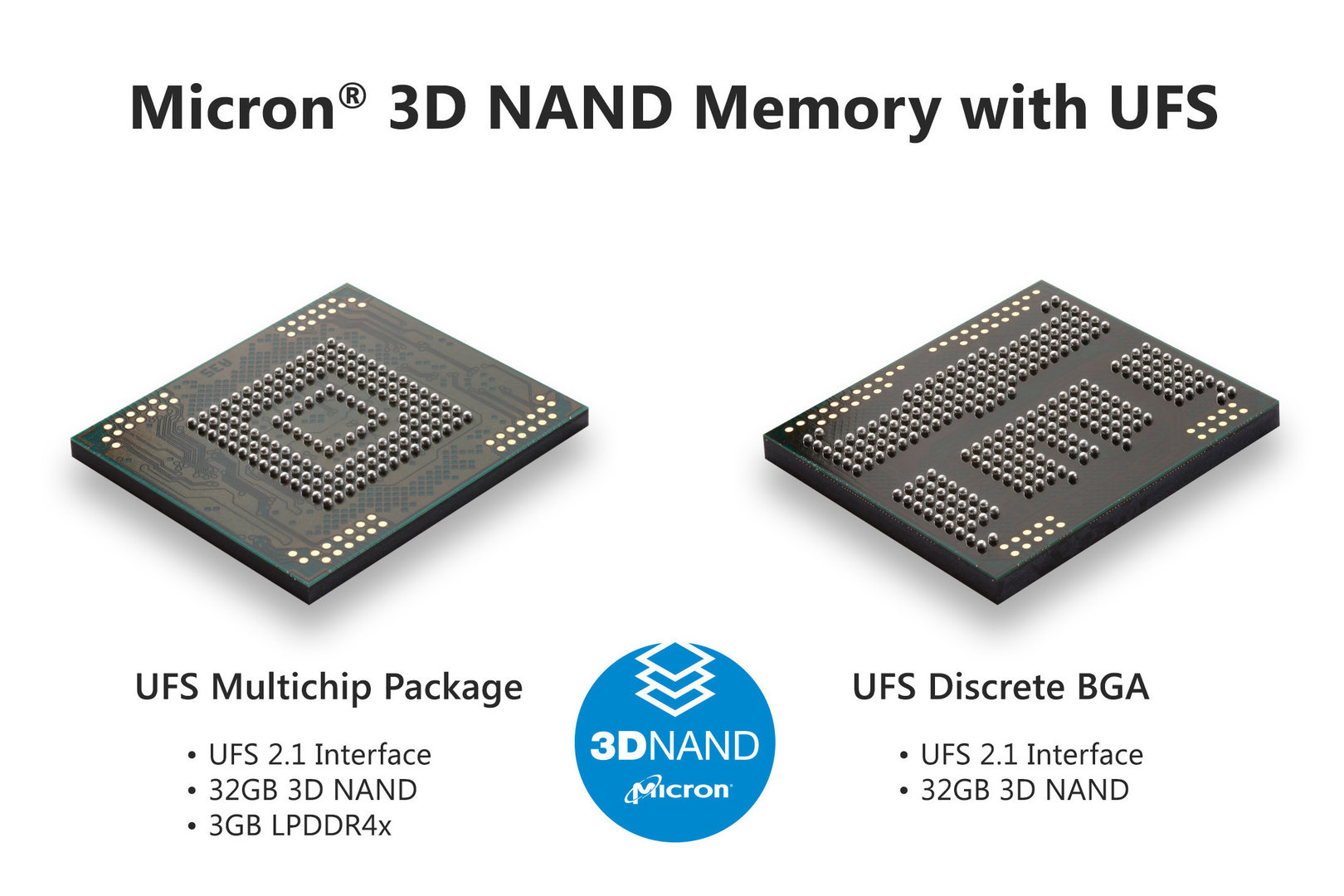

Micron hat auf dem Flash Memory Summit erstmals einen 3D-NAND-Baustein für Smartphones vorgestellt, der zudem – ebenfalls eine Premiere – auf das erst Anfang April vorgestellte UFS-2.1-Format (Universal Flash Storage) setzt. Neben einer BGA-Variante wird es auch ein Multi Chip Package (MCP) mit integriertem LPDDR4x-DRAM geben.

32 GByte für den Anfang

Die ersten Varianten der neuen Speicherbausteine mit Microns 3D-NAND, die aktuell als Muster an Kunden geliefert werden und Ende des Jahres in Stückzahlen verfügbar sein sollen, werden 32 GByte Speicherplatz bieten. Dabei kommt die MLC-Variante der ersten Entwicklungsstufe von Microns 3D-NAND mit 32 Lagen zum Einsatz, wenngleich nicht in der Größe, die in Microns SSDs eingesetzt wird.

Einzelne Dies sind nur rund 60 mm2 groß

Bei den SSDs setzt Micron auf 3D-NAND-Dies mit einer Größe von 168,2 mm2, die in der MLC-Variante jeweils eine Speicherkapazität von 256 Gbit respektive 32 GByte pro Die aufweisen. Da im Mobilsegment die Größe der Komponenten eine sehr viel größere Rolle spielt, kommen bei den neuen Mobilchips aber sehr viel kleinere Dies mit einer Fläche von 60,217 mm2 zum Einsatz, die jeweils eine Kapazität von 64 Gbit beziehungsweise 8 GByte bieten und Micron zufolge aktuell herstellerübergreifend die kleinsten 3D-NAND-Dies sind. Um auf 32 GByte zu kommen, sind folglich in jedem Speicherchip vier dieser 3D-NAND-Dies übereinander gestapelt.

Reiner Flash-Speicher oder MCP mit LPDDR4x

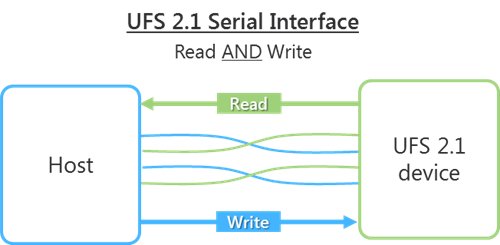

Die kompakten 3D-NAND-Bausteine werden für die Hersteller in insgesamt vier Varianten erhältlich sein. Zum einen ist dabei nach der Spezifikation zu unterscheiden: Neben der moderneren Variante gemäß der leistungsfähigeren UFS-2.1-Spezifikation (ein oder zwei Datenleitungen mit bis zu 600 MB/s pro Leitung) wird Micron auch Bausteine anbieten, die der älteren eMMC-5.1-Spezifikation folgen. Die UFS-Variante soll eine 33 Prozent höhere Bandbreite bieten und bei wahlfreien Zugriffen von der seriellen Natur der Schnittstelle profitieren, die im Gegensatz zur parallel ausgelegten eMMC-Schnittstelle Lese- und Schreibbefehle gleichzeitig verarbeitet.

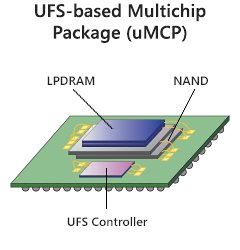

Die eMMC-Variante bietet Micron aktuell ausschließlich als Multi Chip Packages (MCP) an, in denen über dem Flash-Speicher auch noch 3 GByte sparsames LPDDR4x-DRAM oder LPDDR4-DRAM gestapelt sind. Die UFS-Varianten gibt es als MCP ausschließlich mit LPDDR4x sowie auch als klassischen BGA-Chip ohne DRAM.

Die MCP-Bauform ist mit Seitenmaßen von 8,5 × 11 Millimeter minimal größer als die 9 × 9 Millimeter messende BGA-Variante, nimmt aber deutlich weniger Platz in Anspruch als eine Kombination aus BGA-Chip und separatem DRAM-Baustein.

| Produkt | Schnittstelle | 3D-NAND | LPDRAM |

|---|---|---|---|

| eMCP4 | e.MMC 5.1 | 32 GB | 3 GB LPDDR4 |

| eMCP4X | e.MMC 5.1 | 32 GB | 3 GB LPDDR4X |

| uMCP4X | UFS 2.1 G31L | 32 GB | 3 GB LPDDR4X |

| Discrete UFS | UFS 2.1 G31L | 32 GB | – |

Der Einsatz von LPDDR4x soll im Vergleich zu LPDDR4 eine weitere Verringerung der Leistungsaufnahme der neuen MCPs ermöglichen. Durch eine Senkung der Spannung von 1,1 auf 0,6 Volt soll die Energieeffizienz des DRAMs um bis zu 20 Prozent gesteigert werden.

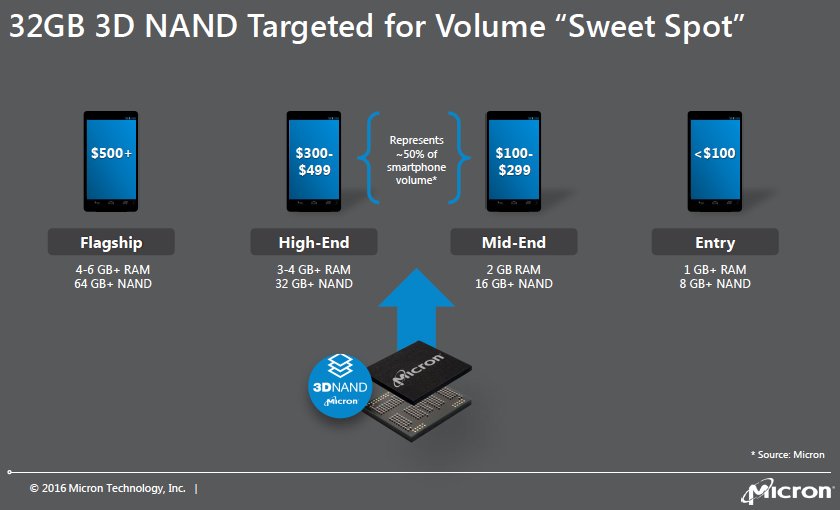

Vorerst nicht für Flaggschiff-Modelle vorgesehen

Zum Einsatz kommen sollen die neuen Bausteine insbesondere bei Smartphones aus der Mittelklasse und dem High-End-Segment, die Micron zufolge rund 50 Prozent des Marktes ausmachen. Für „Flaggschiff-Smartphones“, die nach Microns Darstellung mindestens 64 GByte Flash-Speicher und mindestens vier bis sechs GByte Arbeitsspeicher bieten, sind die neuen 3D-NAND-Bausteine dagegen nicht vorgesehen. Passende UFS-2.0- und UFS-2.1-Bausteine mit Kapazitäten von bis zu 256 GByte haben unter anderem Samsung und SK Hynix vorgestellt, verzichten dabei aber auf MCP-Lösungen mit integriertem DRAM.