Fertigungstechnologie: TSMC und IBM-Allianz geben Einblick in 7-nm-Fertigung

Nachdem Samsung sich zu 10 nm geäußert hat legen TSMC sowie die IBM-Fertigungsallianz im Rahmen des International Electron Devices Meeting 2016 (IEDM) bei 7 nm nach. Demnach will TSMC die risk production im April 2017 beginnen, während IBM und Co. noch auf Forschung und stark auf EUV setzt.

TSMC setzt bei 7 nm auf klassische Fertigungsverfahren

TSMC beschreibt in den Ausführungen (DOCX, Direktdownload) eine 256 Gbit 6T-SRAM-Speicherzelle, die mit einer Spannung von minimal 0,5 Volt arbeitet und mit einer Fläche von 0,027 µm² die kleinste jemals gefertigte sein soll. Zum Einsatz kommt dafür die 7-nm-Fertigung, allerdings weiterhin mit klassischer Immersionslithografie und der 193-nm-Lichtquelle. Gegenüber der aktuellen 16-nm-FinFET-Fertigung aus gleichem Hause soll der Zuwachs in der Leistung bei 35 bis 40 Prozent, die gesenkte Leistungsaufnahme gar bei 65 Prozent liegen.

Wie die EE Times berichtet, sollen die Yield-Raten mit den Testchips bereits bei 50 Prozent liegen, sodass eine Massenfertigung in gut einem Jahr und damit Ende 2017 angepeilt werden kann. Damit würde der Hersteller im Zeitplan liegen, den das Unternehmen seit einigen Quartalen nennt.

Die IBM-Fertigungsallianz setzt auf EUV

Bereits seit zehn oder mehr Jahren im Gespräch nimmt der Zug der EUV-Lithografie nun deutlich an Fahrt auf. IBM als stetige Bank in der Forschung in diesem Bereich zeigt (DOCX, Direktdownload) einen 7-nm-Testchip, bei dem die EUV-Belichtung in bestimmten kritischen Teilbereichen der Waferherstellung – in der middle and back end of the line (BEOL) – zum Einsatz kommt.

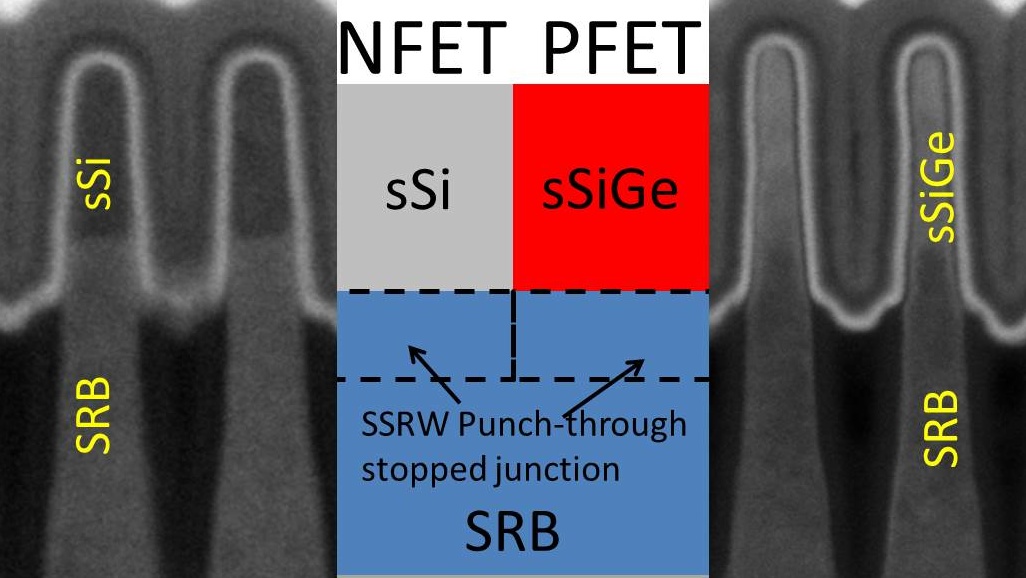

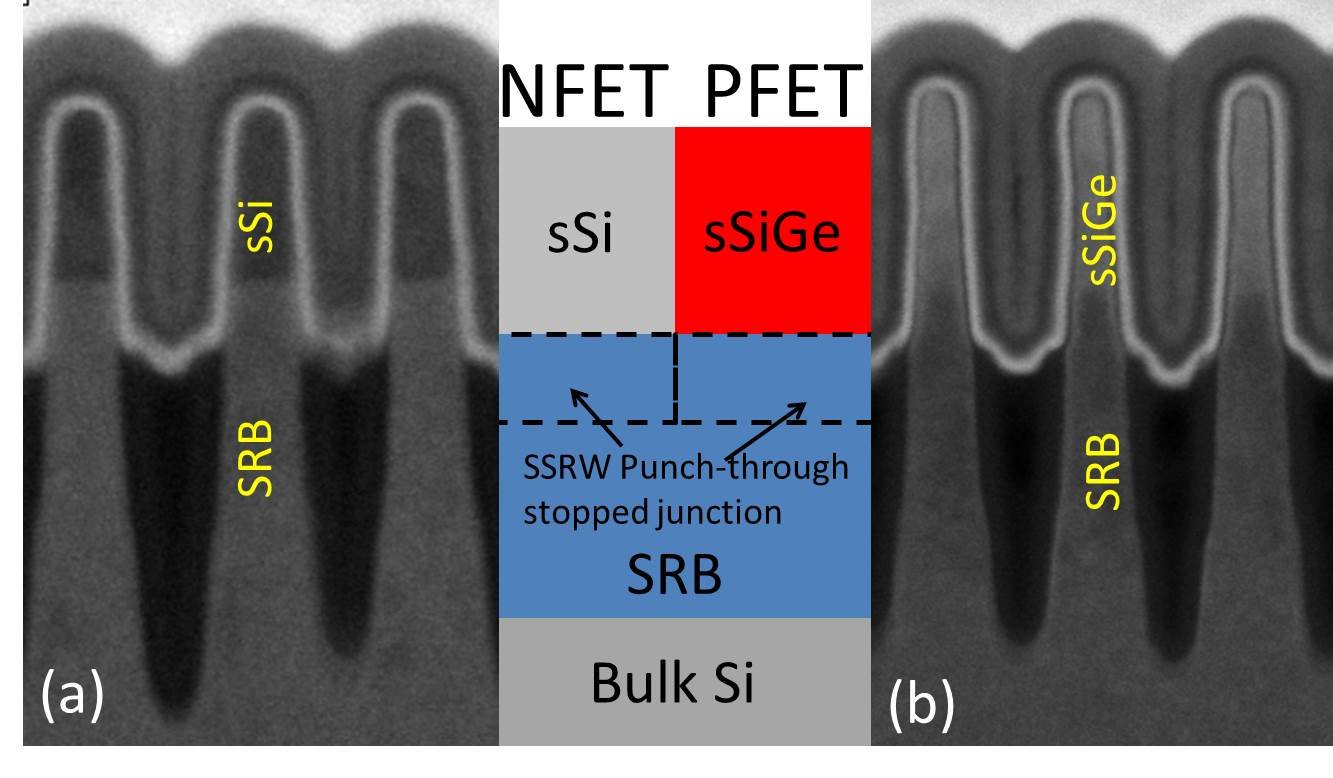

Mit angepasstem neuen Material, einer Mischung aus Silizium und Silizium mit Germanium wurden die niedrigsten Werte beim Gate Pitch (44/48 nm) und Metal Pitch (36 nm) ermittelt, die es bisher für FinFETs gibt. Bisher kommen diese von Intel und deren 10-nm-Fertigung ohne EUV, die bei Gate Pitch, je nach Quelle, bei 53 bis 56 nm liegen und in der Klasse nach bisherigem Wissensstand das bis dahin fortschrittlichste Produkt liefern könnten. IBM nutzt dafür aber nicht nur die neue EUV-Lithografie sondern auch kostspieliges quad patterning – in der Serienfertigung ist heute maximal double patterning an der Tagesordnung. Im Bereich der Forschung ist die Auslotung der Möglichkeiten mit teuren Verfahren aber normal, um sie weiter zu entwickeln und später kostengünstiger in Serie anbieten zu können.

EUV ab 7 und 5 nm im Einsatz

Wann es mit EUV aber wirklich soweit ist, steht in den Sternen. Auch auf der Konferenz wollte keine beteiligte Partei einen Starttermin bekannt geben. IBM hofft auf die 7-nm-Fertigung, wenngleich Globalfoundries als ein Partner der Fertigungsallianz bereits erklärte, 10 nm auszulassen und direkt auf 7 nm ohne EUV gehen zu wollen – diese sollen ab 2018 verfügbar sein. Samsung als zweite große Kraft in dem Verbund setzt erst einmal auf 10 nm und dann 7 nm ohne EUV, plant dann mit 7 nm in zweiter Generation den langsamen Übergang zu EUV.

TSMC als Konkurrent will erst bei 5 nm zu EUV wechseln, da der Hersteller glaubt, dass ASML bis dahin noch nicht weit genug ist, um die Technik wirtschaftlich umzusetzen. Da alle Foundrys auf die Belichtungsmaschinen der Niederländer setzen, dürfte der anvisierte Zeitpunkt von 2018 nach wie vor ein sehr optimistischer sein. Wenn die Vergangenheit gerade auch bei EUV eines gelernt hat, dann, dass die Einführung solcher Verfahren weit mehr Zeit benötigt als ursprünglich veranschlagt.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!