3D-NAND BiCS3: Toshiba legt vor und liefert erste 512-Gb-Chips aus

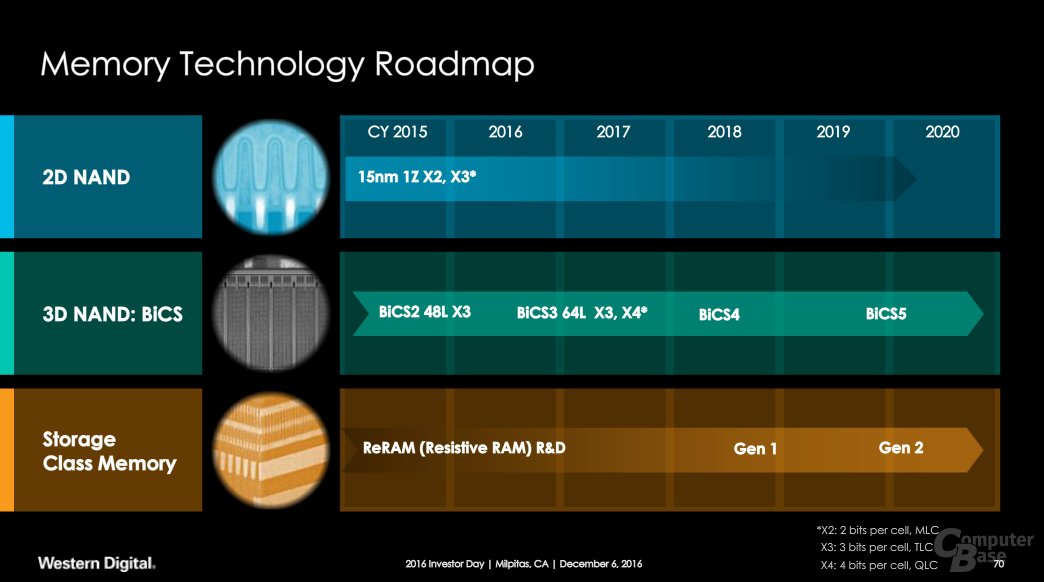

Auf den Start der Pilotfertigung folgt die Auslieferung der ersten Chips: Toshibas 3D-NAND mit 512 Gigabit auf 64 Layern (BiCS3) steht zur Bemusterung bereit. Die Auslieferung von Samples habe in diesem Monat begonnen. Die Massenfertigung wird weiterhin für das zweite Halbjahr angepeilt.

Toshiba legt vor

Damit ist Toshiba, in Kooperation mit Partner Western Digital, der erste Hersteller, der die Verfügbarkeit von 512-Gigabit-Samples angekündigt hat. Der Marktführer Samsung hatte zwar bereits im August den Start der Serienfertigung seines vergleichbaren V-NAND V4 für das vierte Quartal 2016 angekündigt, doch seitdem folgte keine weitere Meldung. Eine Verzögerung liegt somit nahe. Die kleinere Variante von BiCS3 in Form der 256-Gigabit-Chips mit 64 Layern produziert Toshiba bereits in Serie.

512 Gigabit als neue Kapazitätsstufe

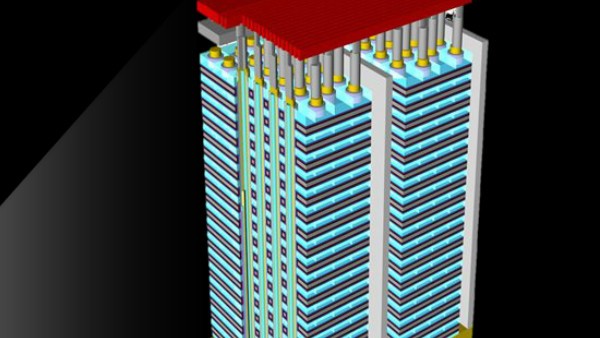

512 Gigabit respektive 64 GByte pro Die bilden aktuell die höchste Speicherkapazität für NAND-Flash. Micron hatte zwar bereits 768-Gigabit-Chips in Aussicht gestellt, doch sind diese noch Zukunftsmusik. Toshibas BiCS3 sichert drei Bit pro Speicherzelle und gehört somit dem Typ TLC an. Die Zellen sind wie bei Samsungs kommender Generation in 64 Ebenen übereinander geschichtet.

Auch der von Micron und Intel (IMFT) entwickelte 3D-NAND in der zweiten Generation verfügt über 64 Layer. Micron hatte kürzlich ebenfalls die Verfügbarkeit von Musterchips verkündet, doch war bisher nur von 256-Gigabit-Chips die Rede, die dafür die kleinsten der Branche sein sollen und entsprechend Kostenvorteile bieten. SK Hynix nutzt bei der kommenden Generation hingegen 72 Layer und will damit im vierten Quartal 2017 ebenfalls 512 Gigabit anbieten.

16 Dies bieten 1 TByte pro Package

Toshiba will bis zu 16 der 512-Gigabit-Dies in einem Chip-Gehäuse (Package) unterbringen. Daraus ergeben sich Speicherbausteine mit rund einem TeraByte Speichervolumen. Muster dieses Hexadeca-Packages sollen ab April 2017 bereitstehen. Toshibas BiCS3 soll in vielen Produktsegmenten eingesetzt werden, darunter auch SSDs.

Kostenvorteile durch mehr Bit pro Wafer

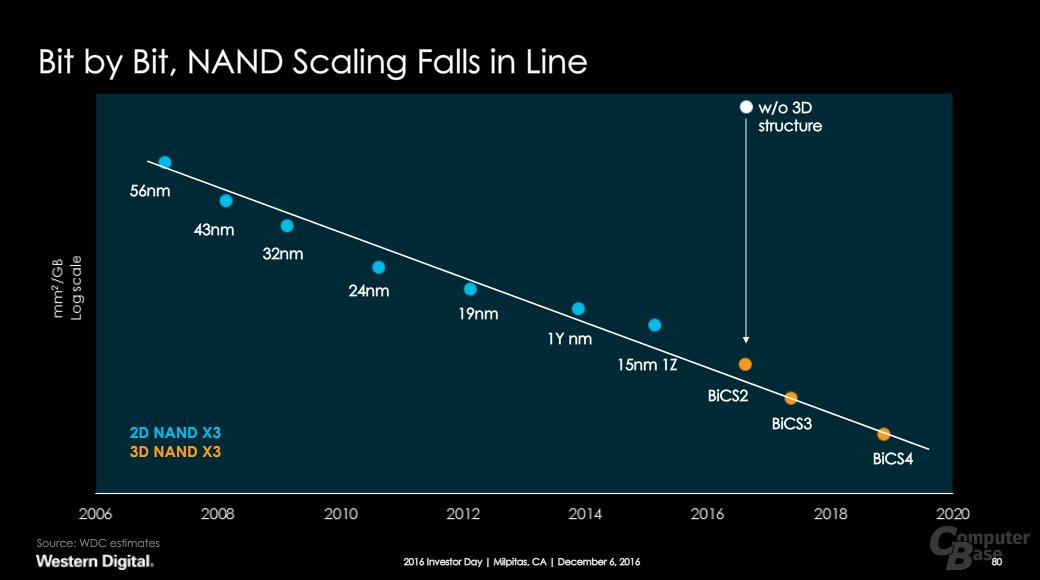

Gegenüber der vorherigen Generation (BiCS2 mit 48 Layern und 256 Gigabit) sei die Kapazität pro Chipfläche um 65 Prozent gesteigert worden, erklärt Toshiba. Folglich fallen die Chips bei doppelter Kapazität lange nicht doppelt so groß aus. Damit bedeutet die neue Generation signifikant mehr Speicherkapazität pro Wafer, was im Gegenzug die Herstellungskosten („cost per bit“) verringert. Gemeinsam hatten Toshiba und Western Digital erläutert, dass der 64-Layer-NAND die „erste echte kostengünstige Technologie“ im Bereich 3D-NAND sein wird.

Speichersparte steht zum Verkauf

Bekanntlich ist die Wirtschaftslage des Gesamtkonzerns Toshiba schlecht. Milliardenabschreibungen durch Verluste im Geschäft mit Atomkraftwerken sollen durch den Verkauf eines Teils der lukrativen Speichersparte kompensiert werden. Inzwischen hat Toshiba eingeräumt, nicht mehr nur den Verkauf eines kleinen Anteils in Erwägung zu ziehen. Jüngste Berichte sprechen von einem anvisierten Verkaufspreis von umgerechnet mindestens 8,8 Milliarden US-Dollar. Laut Reuters wolle Toshiba ein Drittel der Anteile halten, um noch Einfluss auf Entscheidungen nehmen zu können.