Samsung Foundry: 4-nm-Fertigung nutzt EUV und Gate all Around

Samsung hat erste Details zu anstehenden Fertigungsschritten preisgegeben. Auf dem Plan stehen Herstellungsverfahren für 8 nm, 7 nm, 6 nm, 5 nm und 4 nm, die Samsung in den kommenden Jahren anbieten wird. Dabei kommen auch bisher nicht genutzte Gate-all-Around-Technologien zum Einsatz.

Auf dem Samsung Foundry Forum hat der koreanische Elektronikriese Details zu den zukünftigen Fertigungsschritten offenbart und offensive Schritte angekündigt. Dabei überrascht in erster Linie, dass fast jede Ziffer von 10 nm abwärts Verwendung findet, obwohl bisher geplant war, den 7-nm- und 5-nm-Prozess als wichtigste Lösungen für die Zukunft zu adressieren. Doch hinter den Zwischenschritten steckt im Kern oft das gleiche, jedoch mit entsprechenden Optimierungen. Als Kern-Prozesse werden den neuen Plänen nach 7 und 4 nm stehen.

8 nm noch ohne, 7 nm mit EUV

Hinter 8LPP (8nm Low Power Plus) steckt demnach der 10-nm-Prozess (10LPP), in den einige Optimierungen einfließen und so die Packdichte und auch Leistung gegenüber 10LPP leicht ansteigen. Es wird laut Samsung der letzte Schritt bevor die EUV-Lithografie zum Einsatz kommt.

Besagte EUV-Lithografie soll bei 7 nm (7LPP) genutzt werden und so einen Meilenstein für die Zukunft markieren. Es wird jedoch wie bei allen anderen Halbleiterherstellern erwartet, dass zu Beginn lediglich einige Teilschritte unter EUV belichtet werden, während in anderen Segmenten weiterhin klassische Lithografie zum Einsatz kommt – TSMC macht dies bei 7 nm beispielsweise ebenfalls so. Denn Samsung spricht von der Verwendung einer 250 Watt starken EUV-Lichtquelle von ASML, doch diese ist noch nicht einmal fertig entwickelt geschweige denn serienreif. Aktuelle Systeme arbeiten mit 80 bis 125 Watt, ASML fokussiert aber die Forschung und Entwicklung der stärkeren Lichtquellen.

Zwischenschritte mit 6 und 5 nm bei Samsung

Entgegen bisherigen Angaben wird 5 nm (5LPP) kein wirklich neuer Prozess, sondern eine Zwischenlösung – genau wie 6LPP. Bei 6 nm spricht Samsung von Optimierungen bei Leistung und Leistungsaufnahme des 7-nm-Prozesses, für 5LPP spricht Samsung von ganz ähnlichen Verbesserungen, jedoch unter Hinzunahme der neuen Technologien, die bei 4LPP zum Serieneinsatz kommen.

4LPP nutzt erstmals Gate All Around FET

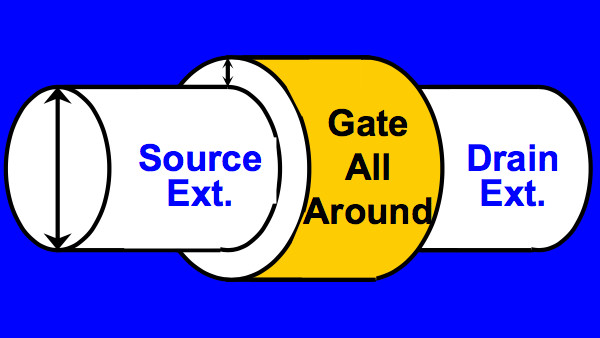

Die nächste Generation in der Fertigungstechnologie nach FinFETs stellt alle Halbleiterfertiger vor Herausforderungen. Die Nutzung von „Gate all Around“ ist dabei eine der Lösungen, die bereits seit vielen Jahren erforscht und in Betracht gezogen wird und scheint sich nun tatsächlich als feste Lösung für die nahe Zukunft zu etablieren.

Die Basis ist dabei der von FinFET sehr ähnlich, aber anstatt „nur“ von drei Seiten, soll – wie der Name schon vermuten lässt – Gate all Around die Nanowires komplett umschließen und so den „perfekten Transistor“ ermöglichen. Samsung nennt einen Teil der Technik auch MBCFETTM (Multi Bridge Channel FET), was die Unterschiede, die genauen Vorteile und Eigenschaften sind, werden die kommenden Jahre zeigen. Frühestens im Jahr 2020 soll laut chinesischen Medien die risk production beginnen, vor 2021 ist kaum mit einer Serienfertigung zu rechnen.

Auch FD-SOI in 18 nm im Programm

Auch gegen Globalfoundries eigenes FD-SOI-Programm hat Samsung ein Pendant in Planung. Doch während Globalfoundries auf 22 und 12 nm setzt – diese zumindest in der Marketing-Sprache so nennt – wird Samsung nur einen 18-nm-FD-SOI-Prozess anbieten. Wie genau es um dessen Eigenschaften bestellt ist, wurde nicht preisgegeben, auch hier wird frühestens 2021 die Serienfertigung verfügbar sein.