Forschung & Entwicklung: IBM zeigt 5-nm-Chip mit EUV und Gate all Around

IBMs Forschungsallianz mit Globalfoundries und Samsung hat im Rahmen eines Symposiums Einblicke in den Fortschritt der 5-nm-Fertigungstechnik gegeben. Samsung hatte kürzlich bereits Ähnliches offenbart, was auch IBM nun sagt: Gate all Around wird die Technik der Zukunft in der Chipfertigung.

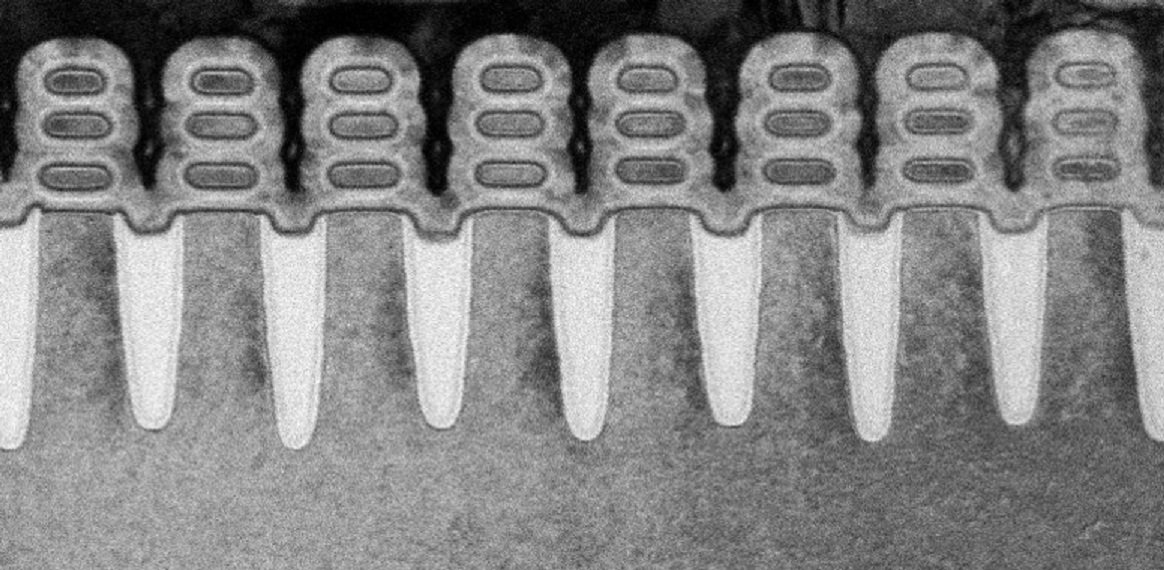

„Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling Beyond FinFET“ heißt der Vortrag von IBMs Forschern, der auf dem VLSI in Kyoto, Japan, präsentiert wird. Dieser beschreibt einige Details der zugrunde liegenden Technik der neuen sehr dünnen, gestapelten Nanoblätter: Der Feldeffekttransistor (FET) wird komplett vom Gate umgeben sein (Gate all Around) – deshalb auch wie bereits kürzlich von Samsung GAA-FET genannt. Die Basis ist dabei der von FinFET sehr ähnlich, aber anstatt „nur“ von drei Seiten, soll – wie der Name schon vermuten lässt – Gate all Around die Nanowires komplett umschließen.

Laut Industrie würde dies nach aktuellem Stand den „perfekten Transistor“ ermöglichen. Die elektrischen Eigenschaften der Nanosheets mit GAA seien dabei FinFET bereits jetzt überlegen, berichten die Forscher vorab. Denn der stromführende Fin in der dritten Dimension (Höhe) ist nicht nur in seiner physischen Skalierbarkeit begrenzt, sondern auch in den elektrischen Eigenschaften. Dies lässt zwar eine Verkleinerung bis maximal 5 nm zu, allerdings primär nur unter Verringerung des Abstands zwischen den Finen, nicht aber mit einer Möglichkeit auf eine gesteigerte Leistung – dafür musste demnach zwingend eine Neuheit her.

Die Vorteile des neuen 5-nm-Transistors mit Nanoblättchen und Gate all Around sind bereits gegenüber 10 nm in den bisher fortschrittlichsten FinFET-Strukturen, das noch nicht einmal im großflächigen Serieneinsatz ist, riesig: Bei gleicher Leistungsaufnahme soll einerseits die Leistung um 40 Prozent ansteigen können, alternativ bei gleicher Leistung die Leistungsaufnahme um 75 Prozent reduziert werden. Im Größenvergleich, den IBM angibt, wird das Vorhaben noch deutlicher: Bei der 7-nm-Fertigung passen rund 20 Milliarden Transistoren auf die Größe eines Fingernagels (rund 50 Quadratmilimeter), bei 5 nm sollen es bereits 30 Milliarden sein.

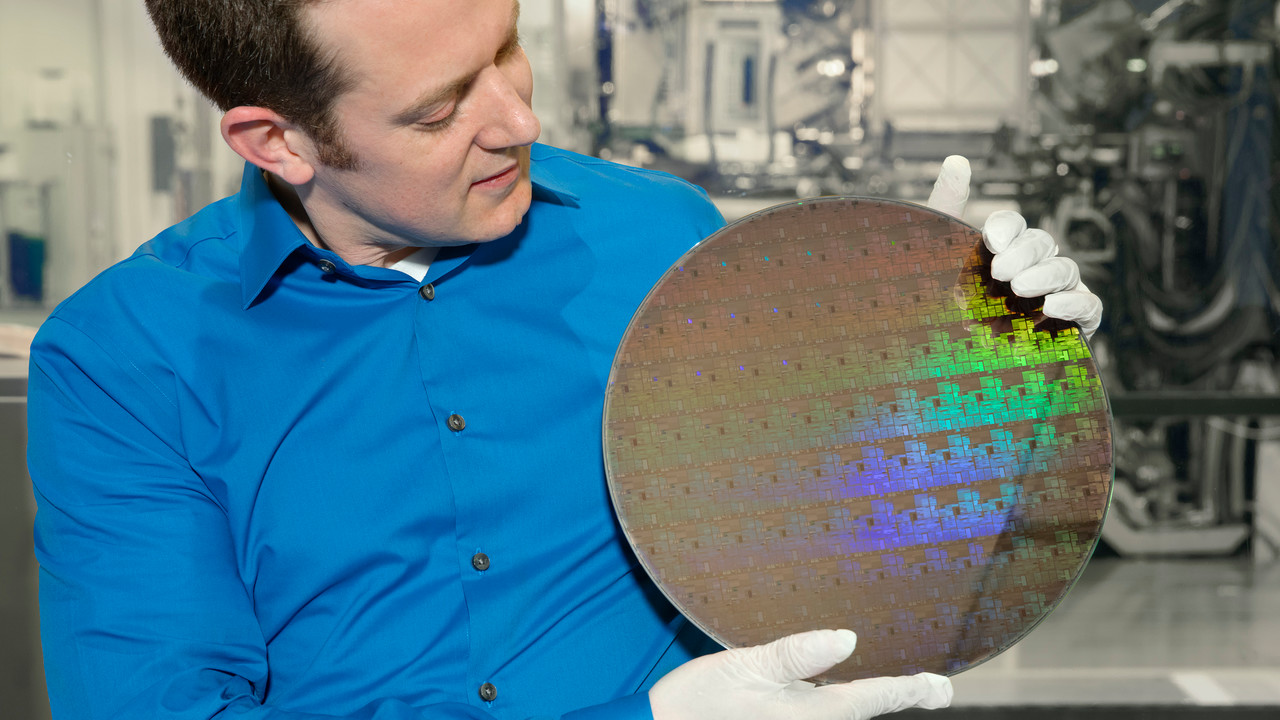

Möglich wird dies zum Teil auch erst durch den Einsatz von EUV-Lithografie von ASML. IBM forscht zusammen mit dem SUNY Polytechnic Institute bereits seit Jahren daran und nutzt die entsprechenden Systeme des niederländischen Fabrikausrüsters. Damit konnten unter anderem erste 7-nm-Chips gefertigt werden, die die gleichen technischen Eigenschaften des neuen GAA-FET-Chips aufweisen. Später wurde dieses Vorgehen dann auf die nächst kleinere Fertigungsstufe angepasst, schreiben die beiden Unternehmen.

Globalfoundries in der Nähe zum IBM-Forschungsstandort in Albany will natürlich als erstes von den Entwicklungen profitieren. 7 nm werden deshalb dort aggressiv als nächste Produktionsstufe ausgebaut und 10 nm direkt übersprungen, 2018 sollen Chips damit in Serie vom Band laufen. 5 nm stehen danach als nächste Schritt auf dem Plan, doch wann dies soweit ist, steht noch in den Sternen. Samsungs erste Chips mit GAA-FET sollten nach bisherigen Berichten 2021 verfügbar sein – mit risk production im Jahr 2020 –, als Teil der IBM-Allianz dürfte dieser grobe Zeitrahmen auch für die anderen Hersteller gelten.