ISSCC 2018: QLC-NAND von Samsung, 96-Layer-NAND von WD/Toshiba

Auf der ISSCC 2018, die am 11. Februar in Kalifornien startet, werden technische Neuheiten aus dem Bereich 3D-NAND präsentiert. Samsung wird über seinen QLC-3D-NAND mit vier Bit pro Speicherzelle und 1 Terabit pro Chip sprechen. Bei Toshiba und Western Digital steht 3D-NAND mit 96-Layer-Architektur auf dem Programm.

Samsungs QLC-3D-NAND mit 1 Terabit pro Die

Samsung hatte bereits auf dem diesjährigen Flash Memory Summit über den QLC-Speicher mit einem Terabit gesprochen und auf dessen Basis SSDs mit 128 TByte in Aussicht gestellt. Bei dem 3D-NAND handelt es sich um Samsungs inzwischen fünfte Generation V-NAND (V5). Auch Toshiba und Western Digital haben bereits QLC-3D-NAND für die Generation BiCS3 mit 768 Gigabit und die nachfolgende Generation BiCS4 mit 1.024 Gigabit angekündigt.

Ferner wird Samsung auch den Z-NAND als Speicher der Z-SSD erneut zum Thema machen. Nach bisherigem Kenntnisstand handelt es sich dabei um SLC-NAND-Flash, der in Kombination mit einem speziellen Controller sehr niedrige Latenzen von nur 15 µs erreicht und damit Intels Optane-SSDs mit 3D XPoint (< 10 µs) nahe kommen soll.

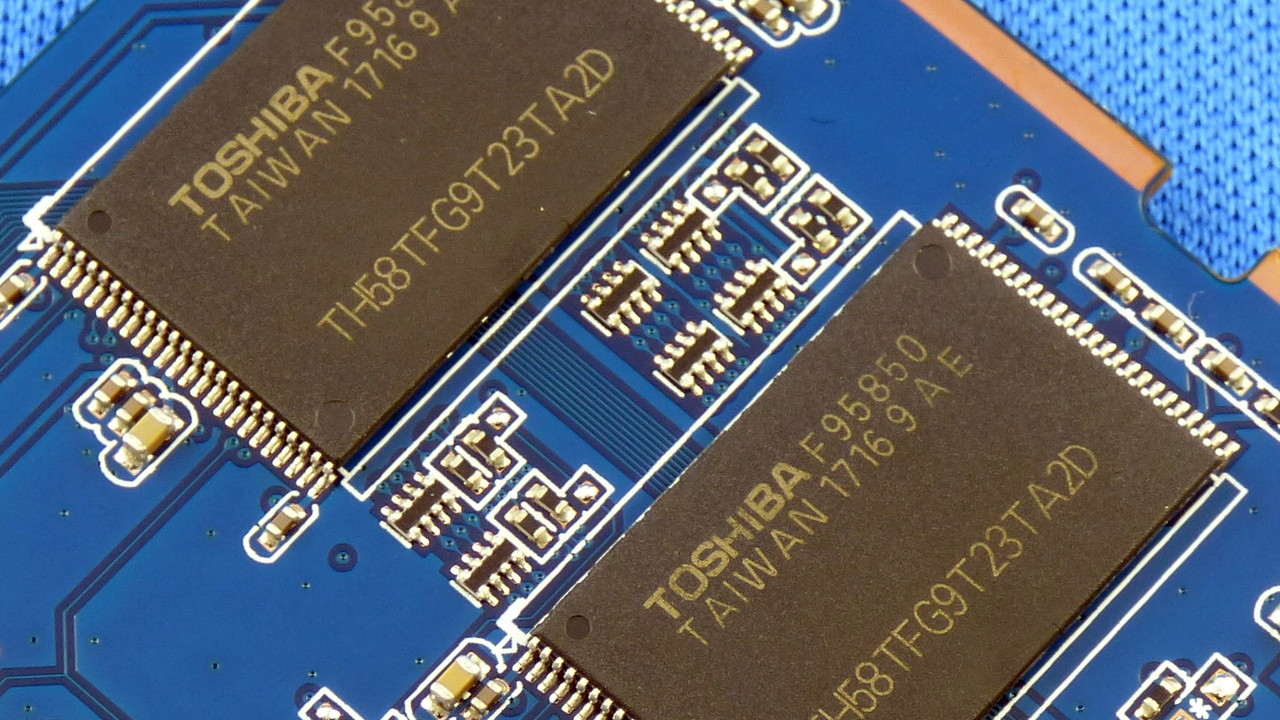

Bei Toshiba und WD geht es hoch auf 96 Layer

Bei Toshiba und Western Digital steht die vierte Generation 3D-NAND (BiCS4) auf dem ISSCC-Programm. Diese bietet erstmals 96 Zellschichten (Layer) – 50 Prozent mehr als BiCS3 mit 64 Layer (Titelbild). Geplant sind zunächst 256-Gigabit-Chips, später sollen auch 768 Gigabit und 1 Terabit mit QLC-Technik folgen. Laut EE-Times soll Samsungs QLC-Flash mit 1 Terabit dagegen weiterhin auf 64 Layer setzen, der ISSCC wird zeigen, ob diese Information zutrifft.

Diese und weitere Neuerungen aus diversen Bereichen sind zum ISSCC 2018 zu erwarten. Die jährliche International Solid-State Circuits Conference findet seit 1954 statt und thematisiert vorwiegend Integrierte Schaltkreise (IC) und SoCs.