Open-Source-Architektur: Western Digital will auf RISC-V umsteigen

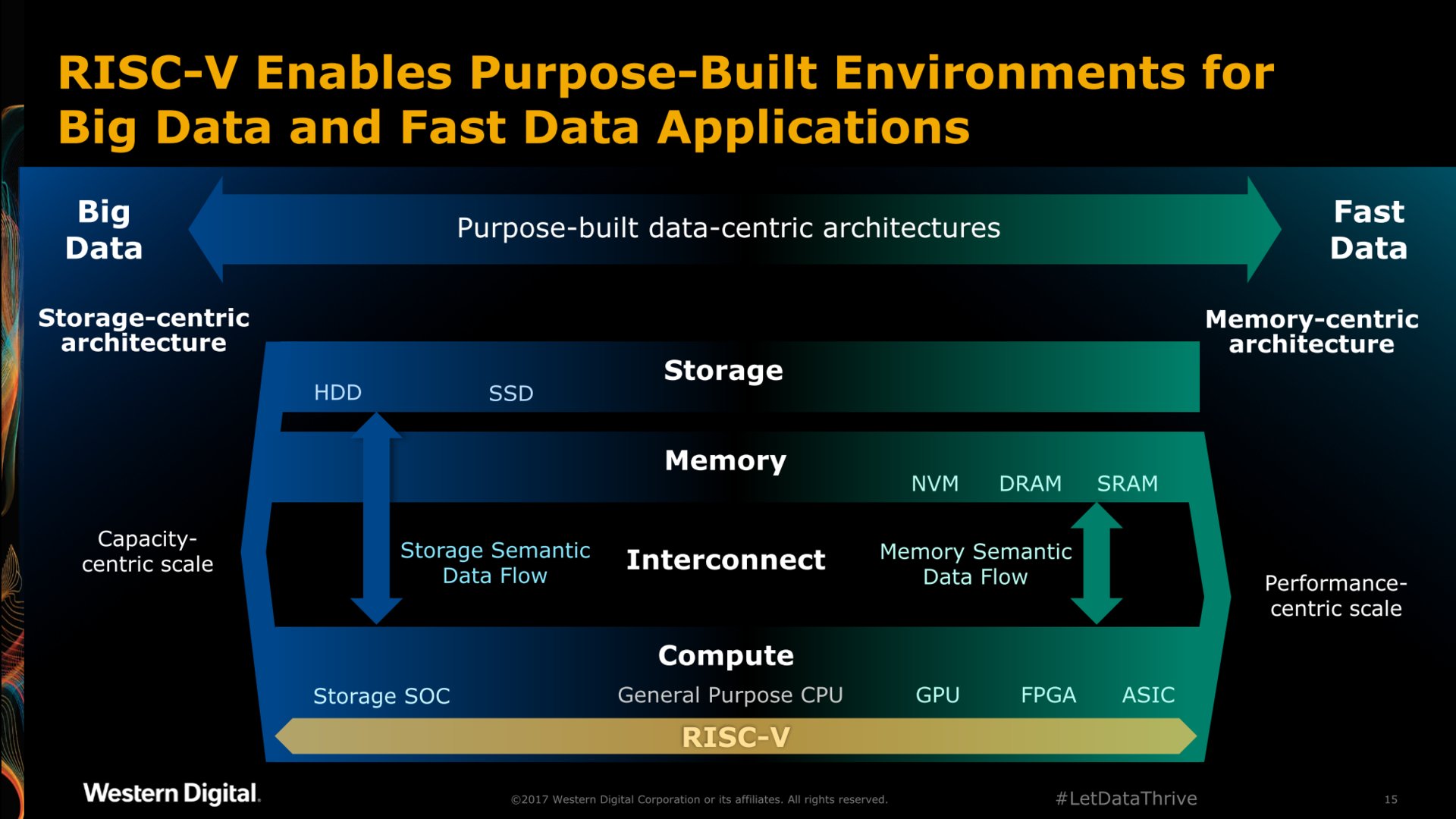

Purpose-Built statt General Purpose. Western Digital möchte weg von den universell ausgelegten Plattformen und Prozessoren. Stattdessen soll ein Wechsel zu mehr auf den Einsatzzweck spezialisierten Komponenten erfolgen. Hierfür hat der Storage-Hersteller die offene Befehlssatzarchitektur RISC-V auserkoren.

Western Digital verschreibt sich RISC-V

Die Ankündigung, die Western Digitals CTO Martin Fink auf dem siebten RISC-V Workshop, machte, hat für die in der RISC-V Foundation organisierte freie ISA großen Stellenwert. Denn der führende Hersteller von Storage-Lösungen inklusive HDDs und SSDs möchte künftig auf jährlicher Basis mehr als eine Milliarde RISC-V-Prozessorkerne in den eigenen Produkten einsetzen und diese Menge später verdoppeln. RISC-V soll dabei sowohl auf Makro-Ebene in großen Storage-Systemen (zum Beispiel ActiveScale) als auch auf Mikro-Ebene direkt in Massenspeicherlaufwerken wie HDDs und SSDs Einzug halten. Eines der Ziele lautet „Moving Compute Closer to Data“ – die Berechnungen sollen näher an den Daten erfolgen.

This concept of bringing compute

to data, rather than data to

compute, creates more intelligent

infrastructures and alleviates

the need for costly increases in

interconnect bandwidth as data

repositories grow beyond the

petabyte-scale level.

Western Digital

Spezialisierung mit offener Architektur

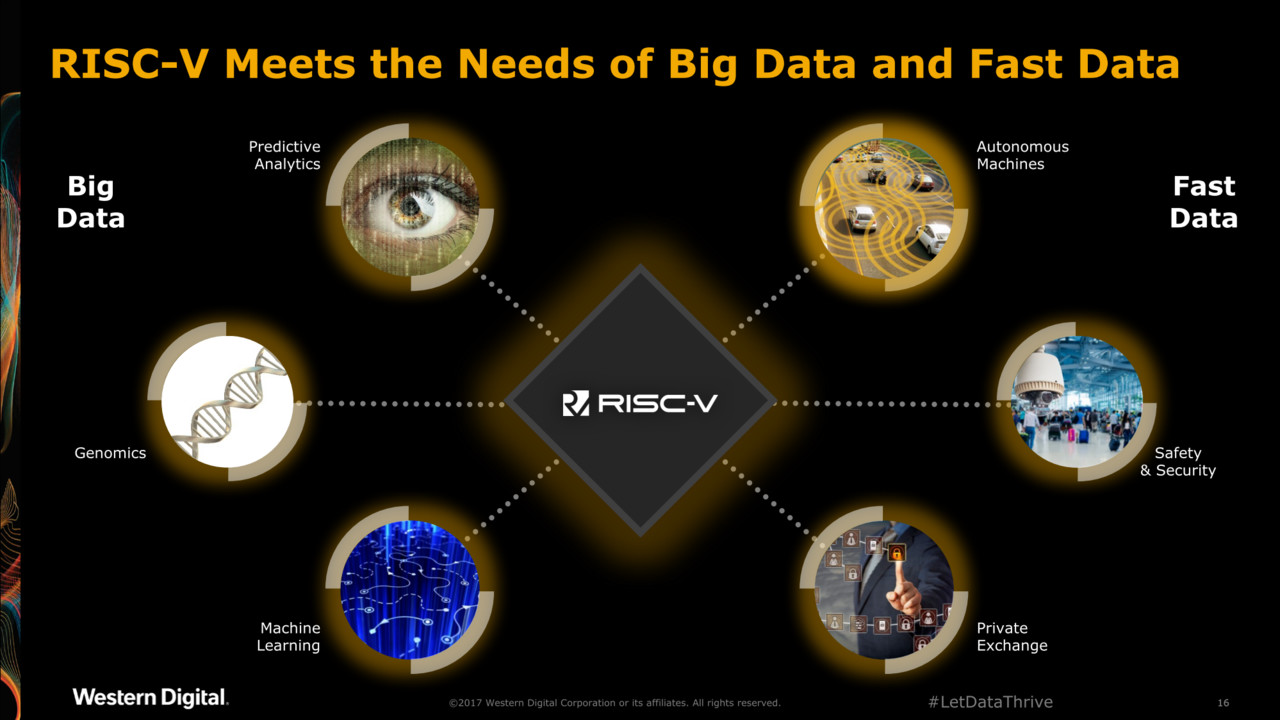

Ein wesentlicher Beweggrund für den Wechsel zu RISC-V ist Spezialisierung. Die ursprünglich von der University of California in Berkeley geschaffene ISA ist offen und kann ohne Lizenzkosten für individuelle Zwecke und dabei völlig herstellerunabhängig eingesetzt werden. Dies stellt aus Sicht von Western Digital die ideale Basis für die Schaffung von „data-centric compute architectures“ dar – also speziellen Computer-Architekturen für den Umgang mit Daten. Die Architektur wird dem Zweck nach gestaltet (purpose-built), anstatt wie bisher für allgemeine Zwecke (general purpose) entworfen zu sein. Ultimativ soll der neue Ansatz zu effizienteren und kompakteren Systemen ohne „proprietäre Barrieren“ zu niedrigeren Kosten führen.

HDD- und SSD-Controller mit RISC-V statt ARM?

Konkrete Produktankündigungen macht Western Digital noch nicht. Doch deutet sich an, dass damit zum Beispiel bei Controllern für HDDs und SSDs eine Abkehr von der proprietären ARM-Architektur bevorsteht. Statt den bei diesen Steuerungsprozessoren meist eingesetzten ARM-Cortex-Kernen würden somit künftig spezialisierte RISC-V-Kerne zum Einsatz kommen.

Western Digital kooperiert mit Esperanto

Western Digital hat jüngst in Esperanto Technologies investiert. Das Unternehmen entwickelt Lösungen auf Basis von RISC-V und hat sich dem Bereich AI respektive Machine Learning verschrieben. Esperanto hat in diesen Tagen Designs für 7-nm-SoCs mit 64 Bit und RISC-V angekündigt. Der ET-Maxion soll 16 High-Performance-Cores bieten, der ET-Minion hingegen sogar 4.096 kleinere und sparsamere Kerne aufweisen. Die Chips sind noch in Planung, ein Termin für den Marktstart steht nicht fest.

Auch SiFive bietet RISC-V-SoCs

Das Startup SiFive hat in den letzten Monaten mit seinen RISC-V-Chips der Serie U54-MC Coreplex große Aufmerksamkeit erlangt. Die SoCs für Embedded-Systeme bringen vier Rechenkerne sowie einen zusätzlichen „Monitor Core“ mit sich, können mit 64 Bit umgehen und unterstützen Linux, Unix und FreeBSD.

Gerade erst hat SiFive neue respektive erweiterte Partnerschaften mit Microsemi und Globalfoundries verkündet. Öffentliche Hinweise auf eine Kooperation mit Western Digital gibt es bisher nicht.

RISC-V Foundation hat namhafte Mitglieder

Auf der Halbleiterkonferenz Hot Chips 29 war RISC-V ebenfalls ein Thema. Auch Nvidia gibt der Open-Source-Architektur eine Chance und plant mit RISC-V-Micro-Controllern in Grafikchips.

Der RISC-V Foundation gehören neben Western Digital, SiFive und Nvidia auch Branchengrößen wie AMD, Google, Huawei, IBM, Qualcomm oder Samsung an – mehr Teilnehmer liefert die öffentliche Mitgliederliste.