Stratix 10 MX: Erster Intel-FPGA mit ARM-Kernen, HBM2 und EMIB

Intels milliardenschwere Altera-Akquisition trägt erste Früchte. Mit dem Stratix 10 MX verbindet Intel alte Altera-Tugenden aus dem FPGA-Geschäft rund um ARM-Cortex-A53-Kerne, kombiniert diese mit schnellem HBM2 und lässt diese über die neue Technologie EMIB miteinander kommunizieren.

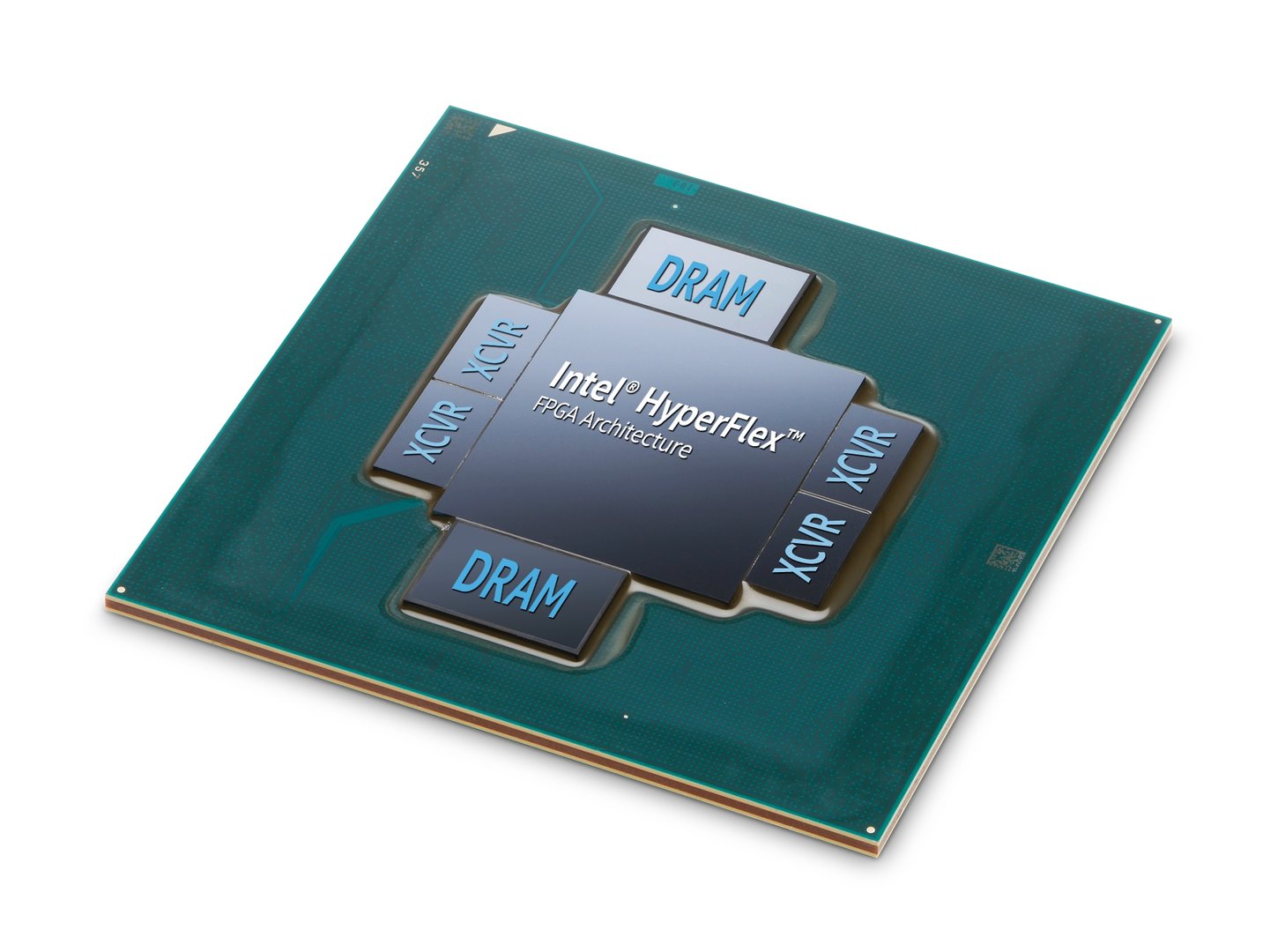

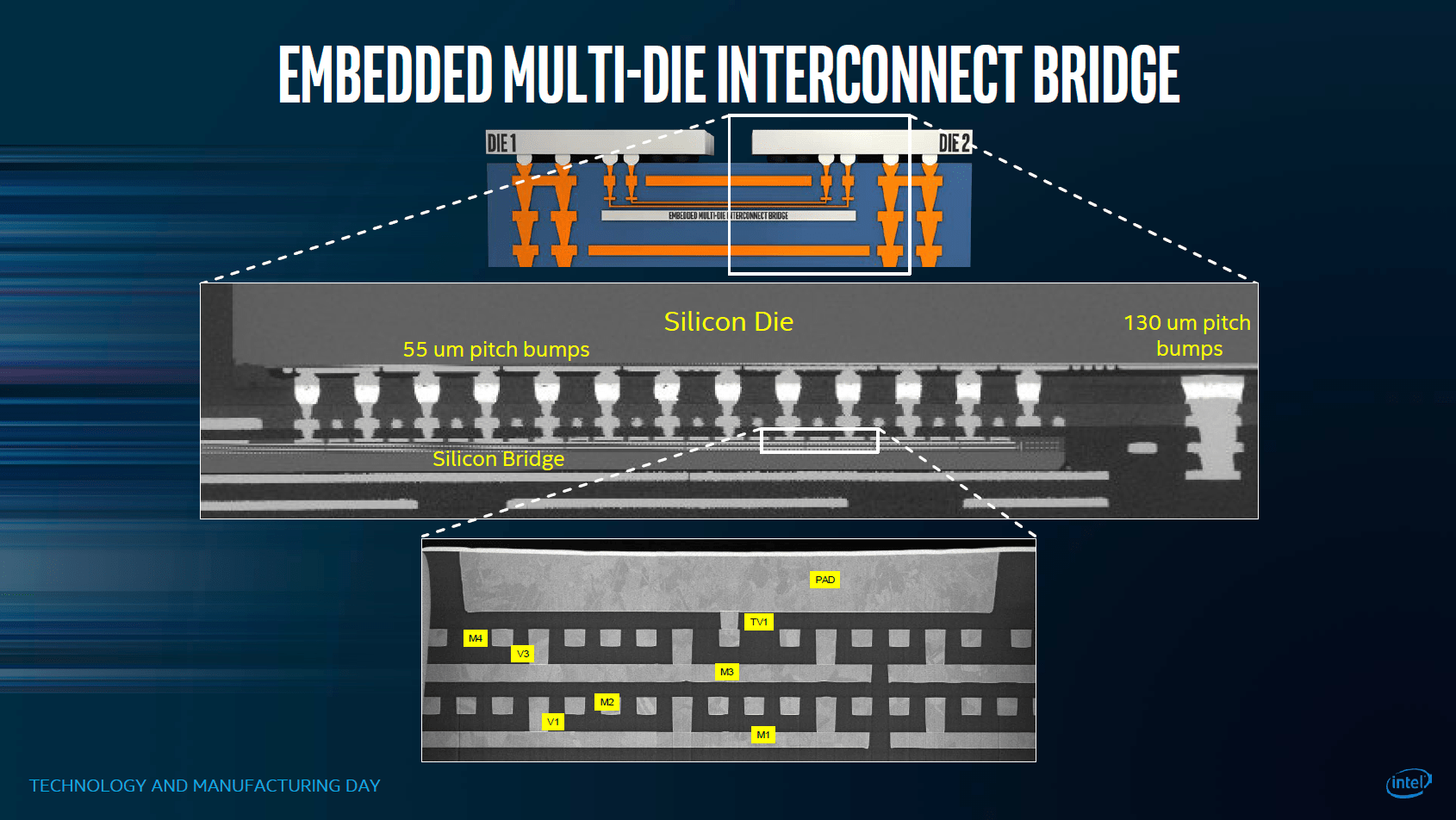

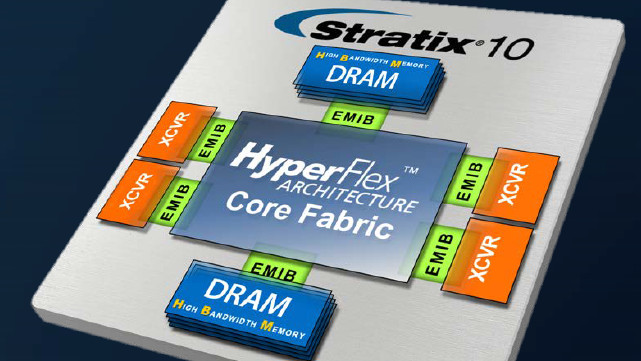

Auf dem Papier sind die acht Modelle (PDF), die Intel mit der Stratix-10-MX-Familie auflegt, zwar nicht die ersten mit HBM2, dieser Preis geht an den Virtex UltraScale+ von Xilinx. Doch die Kombination aus angepasster und auf Leistung optimierter ARM-Architektur mit vier Kernen und bis zu 1,5 GHz Takt, schnellem Embedded-SRAM als Caching-Lösung und HBM2 in einer Größe von bis zu acht Gigabyte und maximal 512 GByte pro Sekunde Speicherbandbreite, die allesamt auf einem Package untergebracht sind und über Intels Embedded Multi-Die Interconnect Bridge (EMIB) kommunizieren, ist bisher einzigartig.

Die Produkte sind für den Einsatz in HPCs und in der High Performance Data Analytics (HPDA) gedacht, sollen sie doch in Echtzeit vielfältige Berechnungen von der CPU übernehmen können, hardwarebeschleunigte Verschlüsselungs- und Authentifizierungsfunktionalität nach AES-256/SHA-256 inklusive. Weiterhin gibt es Ableger mit verschiedenen Transceivern (Stratix 10 SX/GX/TX) oder auch speziell für den Einsatz als DSP mit bis zu 10 TFLOPS an Leistung. Im Idealfall soll eine sehr hohe Effizienz von 80 GFLOPS pro Watt geboten werden, erklärt Intel.

Die „Memory Bandwidth Challenge“ angehen

Die neuen FPGAs von Intel aber auch anderer Hersteller sollen helfen, einige der Probleme der kommenden Generationen zu lösen, die alle großen IT-Hersteller ausgemacht haben: die Memory Bandwidth Challenge, der Speicher als Limitierung vieler zukünftiger Aufgaben. Demnach wird sich der Datenverkehr allein in Datacentern bis 2019 verdreifachen, was vor allem Probleme mit der Bandbreite mit bringt. Gleichzeitig muss aber die Leistungsaufnahme im Auge behalten werden, zudem dürfen die Kosten nicht aus dem Ruder laufen, das Ganze soll zudem in einem möglichst kleinen Package geliefert werden. Wo klassischer DRAM am Limit ist, sollen neue Speichertechnologien wie HBM, 3D XPoint und FPGAs die Brücke schlagen. Weiterhin helfen neue Fertigungstechniken, Xilinx vertraut auf TSMCs 16-nm-Fertigung, Intels Stratix 10 MX nutzt die eigene 14-nm-Fertigung – bisherige FPGAs sind in der Regel noch in 28 nm gefertigt. Bereits durch diesen Schritt sind die deutlichen Effizienzgewinne zum Teil erklärt.