Skylake-Technik: Intel erklärt Stromversorgung einer möglichen GPU

Intel hat auf einer Konferenz die Stromversorgung einer theoretischen GPU auf Basis der 14-nm-Fertigung beschrieben. Die Basis dafür ist die vier Jahre alte Gen9(-LP)-Grafik, die seit Sommer 2015 in den Skylake-U/Y und allen späteren Generationen zum Einsatz kommt – und somit kein erstes Produkt unter Ex-AMDler Raja Koduri ist.

Dass die Forschungen an diskreten Grafikchips und dem Drumherum bei Intel hinter den Kulissen seit Jahren weitergehen, zeigt die jetzige Enthüllung. Denn bei der beschriebenen GPU kommen Techniken zum Einsatz, die es bei Intel im Bereich der CPU seit fast vier Jahren gibt. Seitdem hat sich bei Intel zumindest öffentlich nichts mehr getan, noch heute ist Gen9(-LP) der Standard.

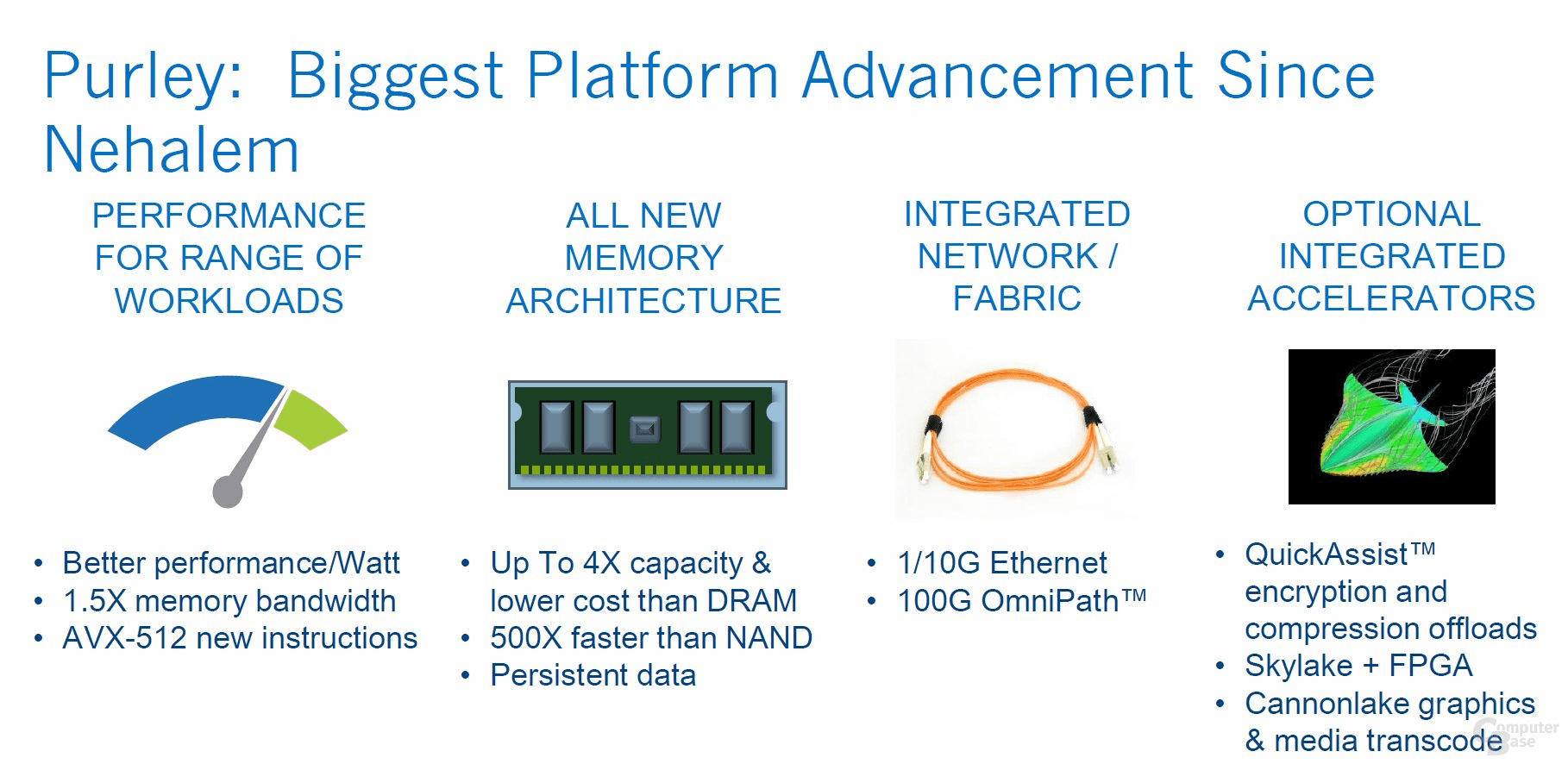

Dass Intel aber seit längerer Zeit auch mit möglichen GPU-Beschleunigerlösungen plant, hatte eine Roadmap aus dem Jahr 2015 für die nun aktuelle Purley-Server-Plattform offenbart. Auf dieser war neben FPGA-Lösungen auch von „Cannon Lake Graphics & Media Transcode“ die Rede. Die reinen Server-CPUs hätten diese entsprechend über PCIe, EMIB oder ähnliches ansprechen müssen, weshalb sie einer diskreten Lösung oder zumindest einem eigenständigen Grafikchip bereits sehr nah gekommen wären. Solch einen möglichen Ansatz zeigte Intel nun.

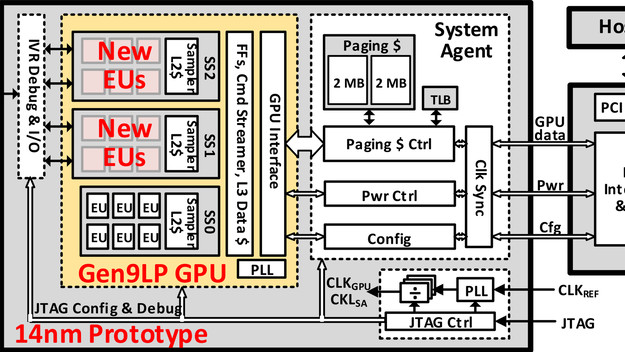

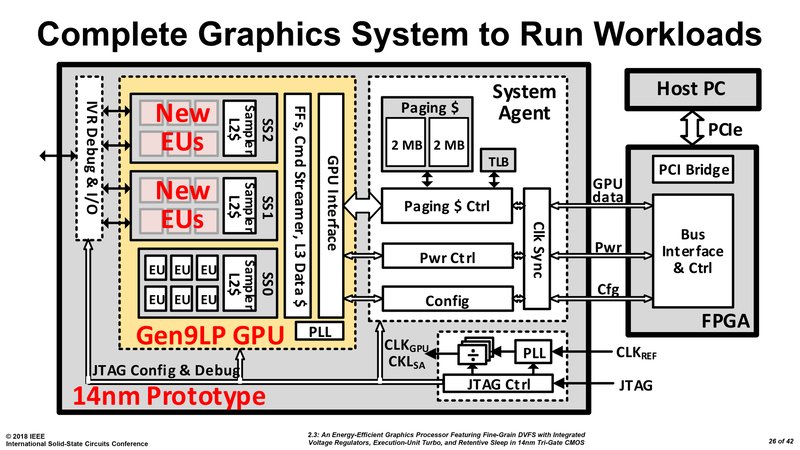

Laut dem Bericht von PCWatch ging es im Rahmen der Präsentation primär um die Mechanismen einer geteilten und möglichst effizienten Stromversorgung einer möglichen GPU, es ist kein Prototyp oder ähnliches, wie Intel auf Nachfrage noch einmal klargestellt hat. Die GPU selbst ist bei Intel in Execution Units (EU) aufgeteilt, das Power Management sollte bei dem Testmuster so intelligent ausfallen, dass beispielsweise jede EU selbstständig takten kann – ein Turbo-Modus zur Taktverdoppelung inklusive, während nicht benötigte EUs schlafen. Die Parallelen zu Möglichkeiten des Power-Gatings bei Intels CPUs sind unverkennbar.

Der 64 mm² große Testchip für diese Forschung enthält mit seinen 1,5 Milliarden Transistoren aber noch viele weitere Bauteile. Neben den zwei angepassten EU-Slices mit jeweils sechs EUs dient ein klassischer Block für den Vergleich, ein System Agent beherbergt zudem 4 MByte SRAM als schnellen Zwischenspeicher direkt vor Ort (Cache). Angesteuert wird der Prototyp zudem über einen externen FPGA, der dann via PCIe mit einem PC verbunden ist. In Zukunft könnte so etwas über EMIB alles auf einem Package untergebracht sein, die Technologie kommt unter anderem bereits bei dem AMD-Intel-Chip Kaby Lake-G zum Einsatz.

-

Grafikchip von Intel (Bild: PC Watch)

Grafikchip von Intel (Bild: PC Watch)

Was Intel davon in Zukunft nutzt, bleibt abzuwarten. Da der Hersteller mit dieser Art von Informationen in den letzten Jahren zeitnah tendenziell nicht an die Öffentlichkeit geht, sollten die Entwicklungen bereits deutlich weiter fortgeschritten sein als bei diesem Prototyp auf Basis vier Jahre alter Technologien. Ohnehin wird nicht erwartet, dass Intel erst mit der Einstellung von AMDs Ex-Grafikchef mit der Arbeit an einer neuen diskreten High-End-Grafiklösung begonnen hat.

Intel hat noch einmal ausdrücklich darauf hingewiesen, dass es sich nicht um einen echten Prototypen einer diskreten GPU handelt. Es geht um Forschungen im Bereich der Stromversorgung. Die Meldung wurde an zwei Stellen präzisiert und die Überschrift angepasst.

Last week at ISSCC, Intel Labs presented a research paper exploring new circuit techniques optimized for power management. The team used an existing Intel integrated GPU architecture (Gen 9 GPU) as a proof of concept for these circuit techniques. This is a test vehicle only, not a future product. While we intend to compete in graphics products in the future, this research paper is unrelated. Our goal with this research is to explore possible, future circuit techniques that may improve the power and performance of Intel products

Intel