Forschung: Erster 3-nm-Testchip feiert sein Tape Out

Die Forscher von IMEC haben zusammen mit den Spezialisten für modernste Halbleitersysteme Cadence erfolgreich einen ersten 64-Bit-Prozessor in 3 nm entwickelt. Dabei kam sowohl die neue EUV-Lithografie zum Einsatz als auch das klassische Immersionsverfahren mit 193-nm-Lichtquelle.

IMEC und Cadence, Partner nahezu aller großen Halbleiterhersteller inklusive GlobalFoundries, Huawei, Intel, Micron, Qualcomm, Samsung, SK Hynix, Sony Semiconductor Solutions und TSMC, machen Fortschritte für die nächsten Generationen an Chips. Die Forschung und Entwicklung an 7 nm ist abgeschlossen, selbst für 5 nm haben die Unternehmen schon entsprechende Programme aufgelegt, der Tape Out eines Testchips in 5 nm erfolgte bereits 2015. Bei 3 nm ist nun der entsprechende Durchbruch mit einem Tape Out vermeldet worden, der viel auf das Know-How zurückgreift, was in Kürze salonfähig werden soll.

Mischbetrieb von EUV- mit Immersionslithografie wird die Regel

Dass die Mischung aus klassischer Lithografie gepaart mit EUV für die nähere Zukunft relevant ist, wird bereits seit vielen Jahren immer deutlicher. Denn ein kompletter Bruch mit der bisherigen Immersionslithografie direkt hin zu EUV ist nahezu unmöglich. Dazu stehen bisher weder ausreichend Scanner bereit, auch ist die Leistungsfähigkeit noch nicht hoch genug, um mit den aktuellen Belichtungsmaschinen mithalten zu können. Deshalb steht bei den großen Foundrys ab der 7-nm-Technologie ein Mischbetrieb auf dem Programm: Die Grundlage ist noch immer die Immersionslithografie, aber einzelne der 11, 12, 14 oder gar 17 Metallschichten moderner CPUs sollen mittels EUV belichtet werden.

Mit fortschreitender Verbesserung der Systeme werden mehr und mehr Lagen mit EUV belichtet, je nach Produkt könnten ab 5 nm die ersten „reinen“ EUV-Chips wirtschaftlich gefertigt werden. Auch daran arbeiten die Forscher derzeit und stellen unter anderem 20 Prozent Kostenersparnis bei der Fertigung von 5-nm-Chips mit EUV pro Wafer in Aussicht.

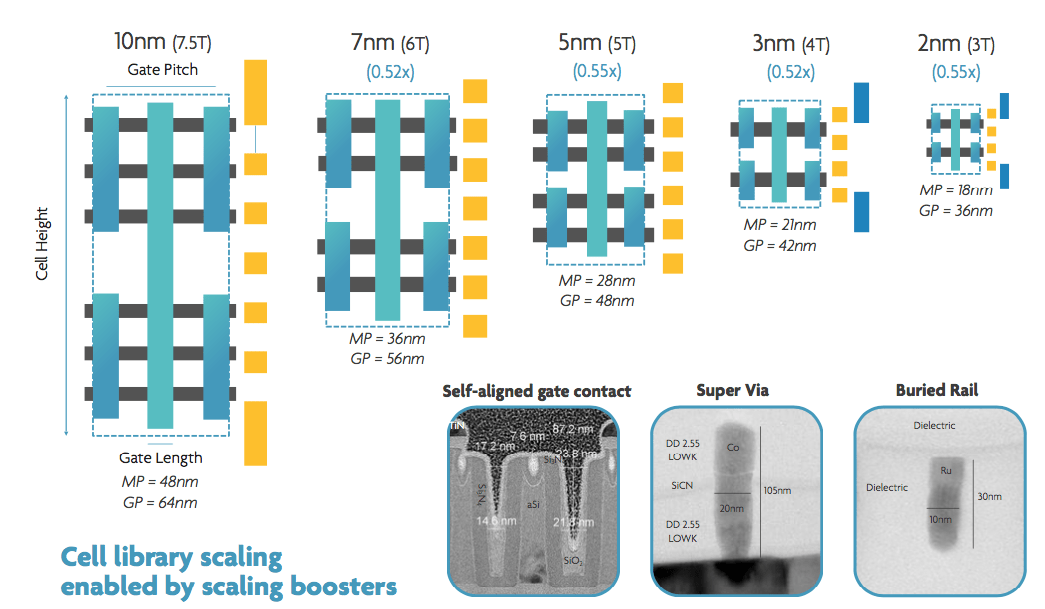

Der 3-nm-Testchip kam im Metal Layer auf einen Pitch von 21 nm (Abstand der Schichten). Aktuell gängige 14-nm-Chips von TSMC/Samsung liegen bei rund 64 nm Pitch, bei der 7-nm-Fertigung sollen sie jeweils bei etwa 40 nm angelangt sein (Intels 10-nm-Fertigung hat bereits minimal 36 nm). Die Skalierung würde demnach ungefähr beibehalten. Doch bis diese Chips dann auch in Großserie produziert werden, dürften noch einige Jahre vergehen. Vor 2021/2022 ist nicht mit deren Eintreffen zu rechnen. Unter anderem TSMC baut gerade eine Fabrik dafür, die dann langsam in Betrieb gehen soll.