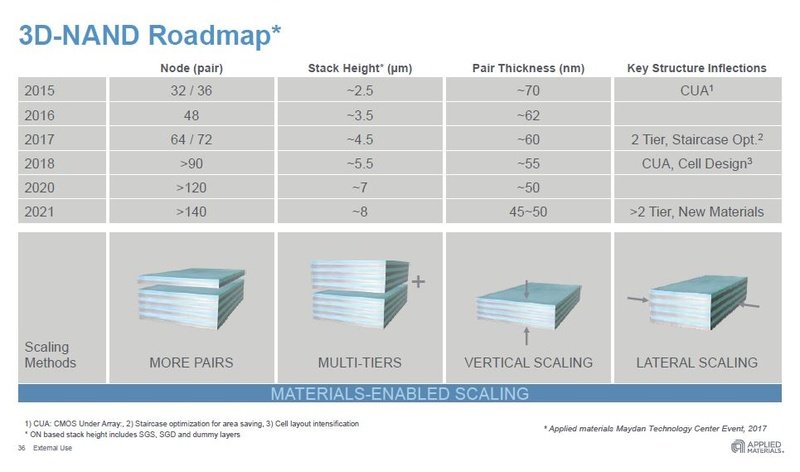

Roadmap: 3D-NAND soll 2021 bereits über 140 Layer besitzen

Auf dem International Memory Workshop (IMW) in Japan hat Sean Kang von Applied Materials über die kommenden Generationen von 3D-NAND-Flash gesprochen. Eine Roadmap verdeutlicht: Die Zahl der Zellschichten (Layer) soll auf über 140 steigen. Gleichzeitig sollen diese dünner ausfallen.

Bei 3D-NAND liegen im Gegensatz zu 2D-NAND die Speicherzellen nicht in nur einer Ebene, sondern in mehreren Schichten übereinander. Auf diesem Weg lässt sich die Speicherkapazität pro Chip (Die) deutlich steigern, ohne dass die Chip-Fläche vergrößert oder die Zellen geschrumpft werden müssen. Bei 3D-NAND sind sogar größere Strukturen und Zellabstände möglich, was der Haltbarkeit zugute kommt.

3D-NAND soll 2021 über 140 Layer erreichen

Vor fast fünf Jahren erschien der erste 3D-NAND überhaupt; Samsungs V-NAND der ersten Generation besaß 24 Layer. Bei der nachfolgenden Generation wurden 32 Layer eingesetzt, danach 48 Layer. Aktuell sind die meisten Hersteller bei 64 Layer angekommen, SK Hynix tanzt mit 72 Schichten aus der Reihe.

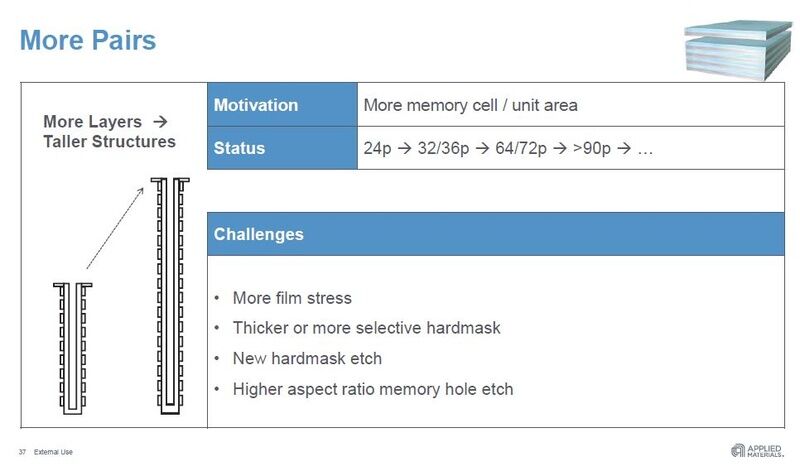

In diesem Jahr wird die nächste Generation eingeläutet. Die Roadmap spricht von mehr als 90 Layern, was über 40 Prozent mehr als zuvor bedeutet. Dabei soll die Höhe eines Speicherstapels (Stack) von etwa 4,5 µm auf rund 5,5 µm und damit nur um circa 20 Prozent ansteigen. Dies liegt daran, dass zugleich die Dicke eines Layers von rund 60 nm auf etwa 55 nm reduziert werde. Anpassungen am Design der Speicherzellen sowie die von Micron schon 2015 eingesetzte Technik CMOS Under Array (CUA) sieht Kang als Schlüsselmerkmale dieser Generation.

Toshiba und Western Digital wollen die neuen BiCS4-Speicherchips im 96-Layer-Design in diesem Jahr in Serie fertigen und haben nach eigenen Angaben bereits Ende 2017 erste Chips ausgeliefert.

-

3D-NAND-Roadmap bis 2021 (Bild: Applied Materials via PC Watch)

3D-NAND-Roadmap bis 2021 (Bild: Applied Materials via PC Watch)  Mehr Zellschichten (Layer, hier Pairs) (Bild: Applied Materials via PC Watch)

Mehr Zellschichten (Layer, hier Pairs) (Bild: Applied Materials via PC Watch)

Kangs Roadmap sieht den nächsten Schritt für 3D-NAND bei mehr als 120 Layern, was etwa im Jahr 2020 erreicht werde. Dass die Flash-Hersteller mit 128 Layern planen, ist kein Geheimnis. Bei erneuter Reduzierung der Layer-Dicke sollen die Stacks auf 7 µm anwachsen. Für 2021 werden dann über 140 Layer und eine Stack-Höhe von 8 µm prognostiziert. Bei dieser Generation sollen neue Materialien bei der Herstellung Verwendung finden.

Die Roadmap geht nicht auf die Speicherkapazitäten ein. Aktuell sind die Hersteller bei 512 Gigabit pro Die mit 64-Layer-Technik angekommen. Mit 96 Layern sollen zunächst 768 Gigabit und mit 128 Layern schließlich 1.024 Gigabit also rund ein Terabit möglich werden. Der Einsatz der QLC-Technik mit vier Bit pro Speicherzelle kann Terabit-Chips auch bereits mit 96-Layer-Struktur ermöglichen. Samsung will dies mit der fünften Generation des V-NAND (V5) erreichen und auf dessen Basis in diesem Jahr die erste 128-TB-SSD vorstellen.