Wafer on Wafer von TSMC: Neue Stacking-Technologie verbindet direkt zwei Wafer

Auf dem TSMC Technology Symposium stellte der größte Auftragsfertiger der Welt eine neue Technologie vor, um Chips miteinander zu verbinden. Doch statt den Weg über einen Interposer oder modernere Lösungen wie Intels EMIB zu gehen, werden zwei Wafer direkt miteinander verbunden.

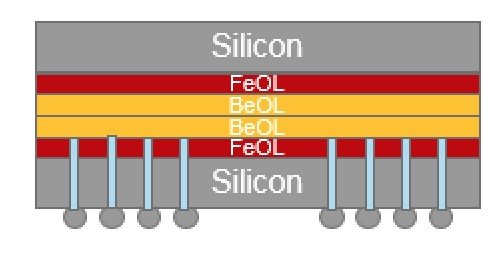

Die 3D-Stacking-Technologie wird „Wafer on Wafer“ (kurz: WoW) genannt und stapelt zwei Wafer aufeinander. Hierbei werden die ersten Unterschiede sichtbar: Beide Wafer müssen gespiegelt aufgebaut sein, damit dies funktioniert, was beim Silizium-Level außen beginnt und über den Front end of Line (FeOL) und Back End (BeOL) fortgesetzt wird.

Die Besonderheit liegt im unteren Wafer, der mit TSVs („thru silicon vias“) durchbohrt wird. Diese unter 10 μm feinen Stränge sollen letztlich Kontakt zum zweiten Wafer herstellen. Die TSV-Stacking-Technologie ist weit erprobt, bei DRAM kommt sie bereits seit Jahren zum Einsatz und fasst nun auch in anderen Gebieten Fuß. Bei TSMC wird sie zunächst bei „System on integrated Chips“ (SoIC) eingesetzt. Weitere Details dazu wird der Hersteller aber erst in Zukunft preisgeben.

Ein hoher Yield ist Voraussetzung

Bei dem Verfahren gibt es jedoch noch Probleme mit der Ausbeute an zusammengeschweißten Chips von diesen speziellen Wafern. Selbst wenn ein Wafer viele gute oder schlechte Chips aufweist, wird er immer mit dem zweiten Wafer kombiniert. Ein funktionierender Die kann auf einem defekten landen und umgekehrt, wodurch das gesamte Konstrukt letztlich unbrauchbar wäre. Folglich kann die Technik nur dort eingesetzt werden, wo die Yield-Raten sehr hoch sind. Daher wird zum Start voraussichtlich eine ältere Chip-Generation genutzt, bei der die Ausbeute deutlich über 90 Prozent liegt.

Die Besonderheit des Wafer-Stackings liegt auch noch an anderer Stelle. Da diese direkt auf Wafer-Ebene passiert, kann solch ein Dual-Die nach wie vor auf einem Interposer oder EMIB platziert werden, was ein Dual-Dual-Die oder noch größere Ausbaustufen ermöglichen würde. Am Ende wird es zweifelsohne eine kostspielige und schwierige Lösung. Da TSMC aber auch neue High-End-Lösungen für das HPC-Geschäft liefern will, steht eine weitere Möglichkeit für Foundry-Partner zur Verfügung.