Micron: 96-Layer-NAND und 1Ynm-DRAM im 2. Halbjahr in Serie

Bei Micron läuft es derzeit rund: Der weltweite Bedarf an Speicher ist immer noch enorm und die hohen Preise sorgen für Rekordeinnahmen bei den Herstellern. Auch für die Zukunft sieht sich Micron gut aufgestellt, denn die neuen Generationen von 3D-NAND und DRAM sind schon unterwegs.

Neue Speichergeneration im 2. Halbjahr in Serie

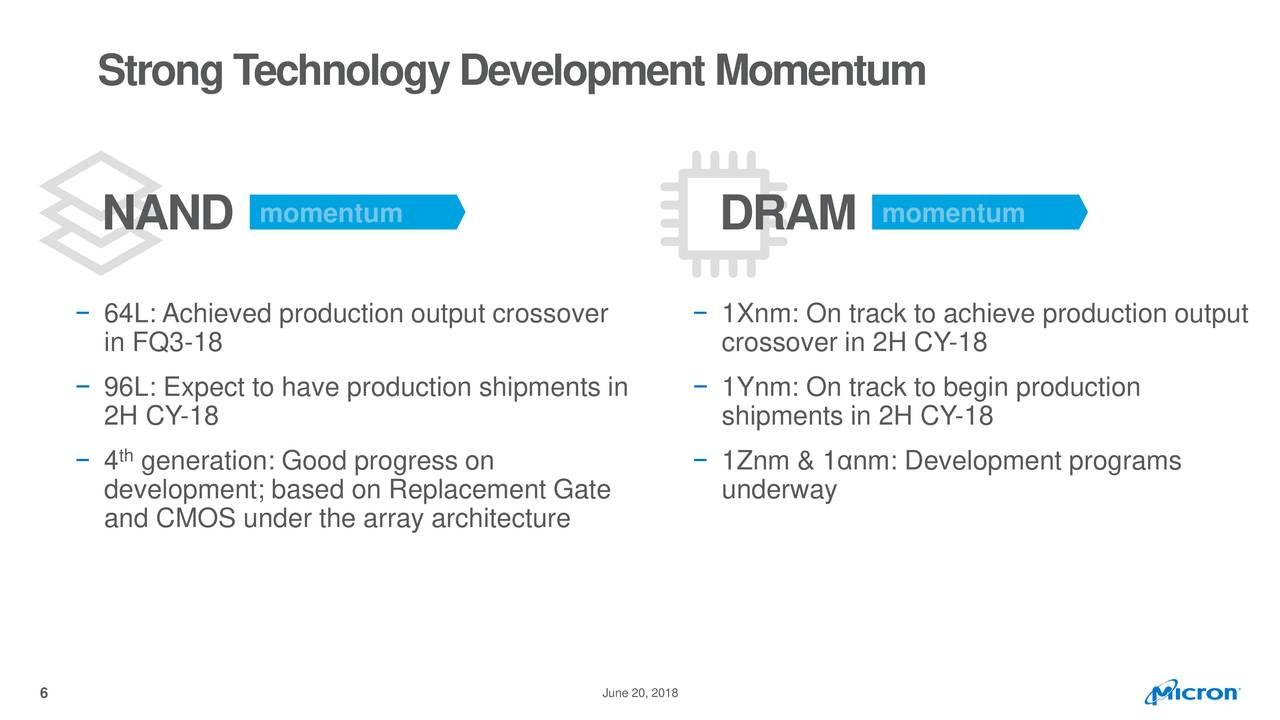

Wie Micron am Mittwoch im Earnings Call verkündet hat, sollen erste Chips aus der Serienfertigung sowohl beim neuen 3D-NAND mit 96-Layer-Architektur als auch dem neuen DRAM im 1Ynm-Herstellungsverfahren im zweiten Halbjahr 2018 ausgeliefert werden. Durch den nur groben Zeitrahmen bleibt allerdings die Möglichkeit, dass dies erst gegen Ende des Jahres der Fall sein wird. Mit der neuen Speichergeneration sollen die Kosten pro Bit weiter gesenkt werden.

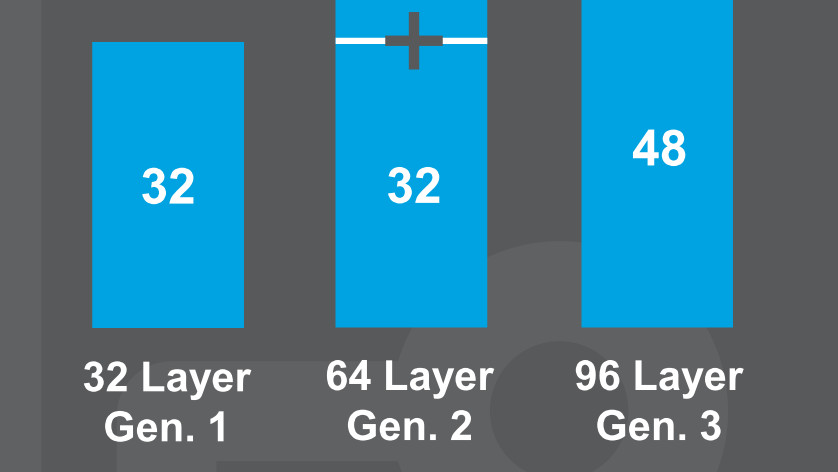

In puncto Datendichte von NAND-Flash gilt Micron gemeinsam mit Partner Intel derzeit als führend. So bieten beide die derzeit kleinsten 256-Gbit- und 512-Gbit-Dies der Branche an, was vor allem durch das „CMOS Under Array“-Design erreicht wurde, bei dem die Logik-Schaltungen nicht neben den Speicherzellen liegen, sondern in einer weiteren Ebene untergebracht sind, womit Chipfläche eingespart wird. Micron und Intel sind auch die ersten Hersteller, die 64-Layer-3D-NAND des Typs QLC mit 4 Bit pro Speicherzelle und bis zu 1 Terabit pro Die anbieten.

Die Fertigung der aktuellen 64-Layer-Generation von Micron läuft zudem sehr gut: Schon im dritten Fiskalquartal 2018, das am 31. Mai endete, soll die Menge der 64-Layer-Chips jene der vorherigen 32-Layer-Generation überschritten haben – das sogenannte „production crossover“ wurde erreicht. Beim DRAM der aktuellen 1Xnm-Generation sei das Crossover erst im zweiten Halbjahr des laufenden Kalenderjahres zu erwarten.

DRAM: Berichte über technische Probleme und mögliche Preisabsprachen

Generell erscheinen die Hürden beim Umstieg auf neue DRAM-Prozesse derzeit schwieriger zu bewältigen zu sein als beim NAND-Flash. DigiTimes hatte vor kurzem über technische Probleme bei der neuen 18nm-DRAM-Produktion von Samsung und SK Hynix geschrieben; die Chip-Ausbeute (Yield) sei instabil.

Dass durch solche Probleme bei der Umstellung der Fertigung Versorgungsengpässe entstehen, ist eine Erklärung der Hersteller für die stark gestiegenen und anhaltend hohen DRAM-Preise. China als weltweit größter Abnehmer von DRAM vermutet allerdings Preisabsprachen unter den DRAM-Herstellern und hat inzwischen allen großen Herstellern Wettbewerbshüter zu Gesprächen ins Haus geschickt. Sollten Untersuchungen folgen, die die Hersteller der Preisabsprache überführen, drohen Strafen in geschätzter Höhe von 800 Millionen bis 8 Milliarden US-Dollar, so DigiTimes.