YMTC: Der kommende 3D‑NAND aus China im Detail

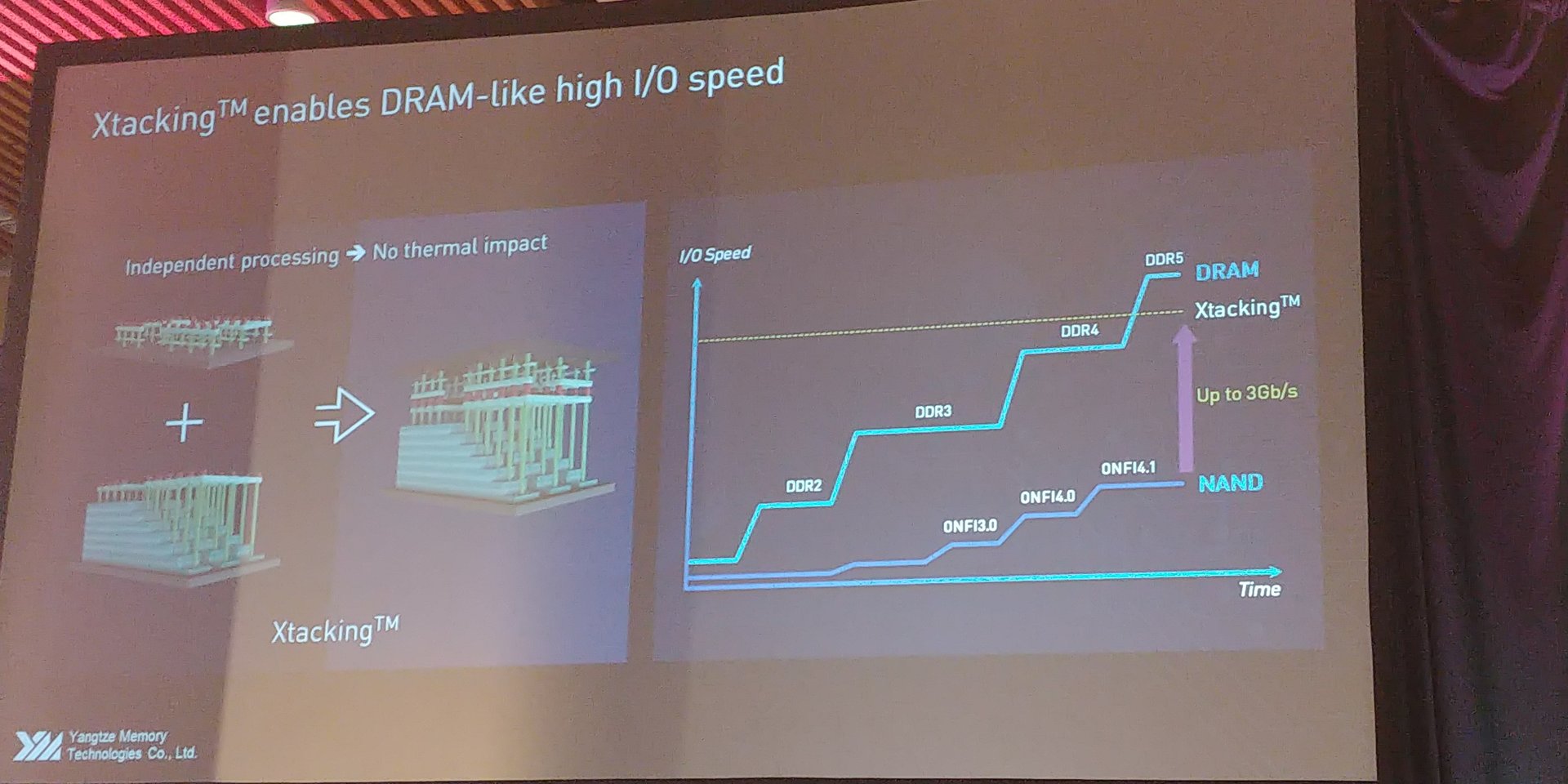

YMTC hat weitere Details zum neuen 3D-NAND aus China veröffentlicht. Im Fokus steht die Xtacking-Architektur, bei der Chip-Logik und Speicher auf separaten Wafern hergestellt und erst anschließend miteinander verbunden werden. Mit dem Design verspricht YMTC nicht nur Vorteile bei der Datendichte, sondern auch beim Durchsatz.

Die erste Generation des 3D-NAND aus China wird schon seit Herbst 2017 gefertigt. Dabei handelt es sich um ein herkömmliches 32-Layer-Design, bei dem die Chip-Logik neben den Speicherzellen auf dem Wafer liegt. Doch dieses ist nur eine Art Testballon, denn erst mit den kommenden Generationen will YMTC den Markt bedienen. Zum Flash Memory Summit hat der Hersteller daher auf die zweite Generation mit neuer Architektur und 64 Speicherschichten verwiesen.

Xtacking-Architektur mit Logik und Speicher auf eigenem Wafer

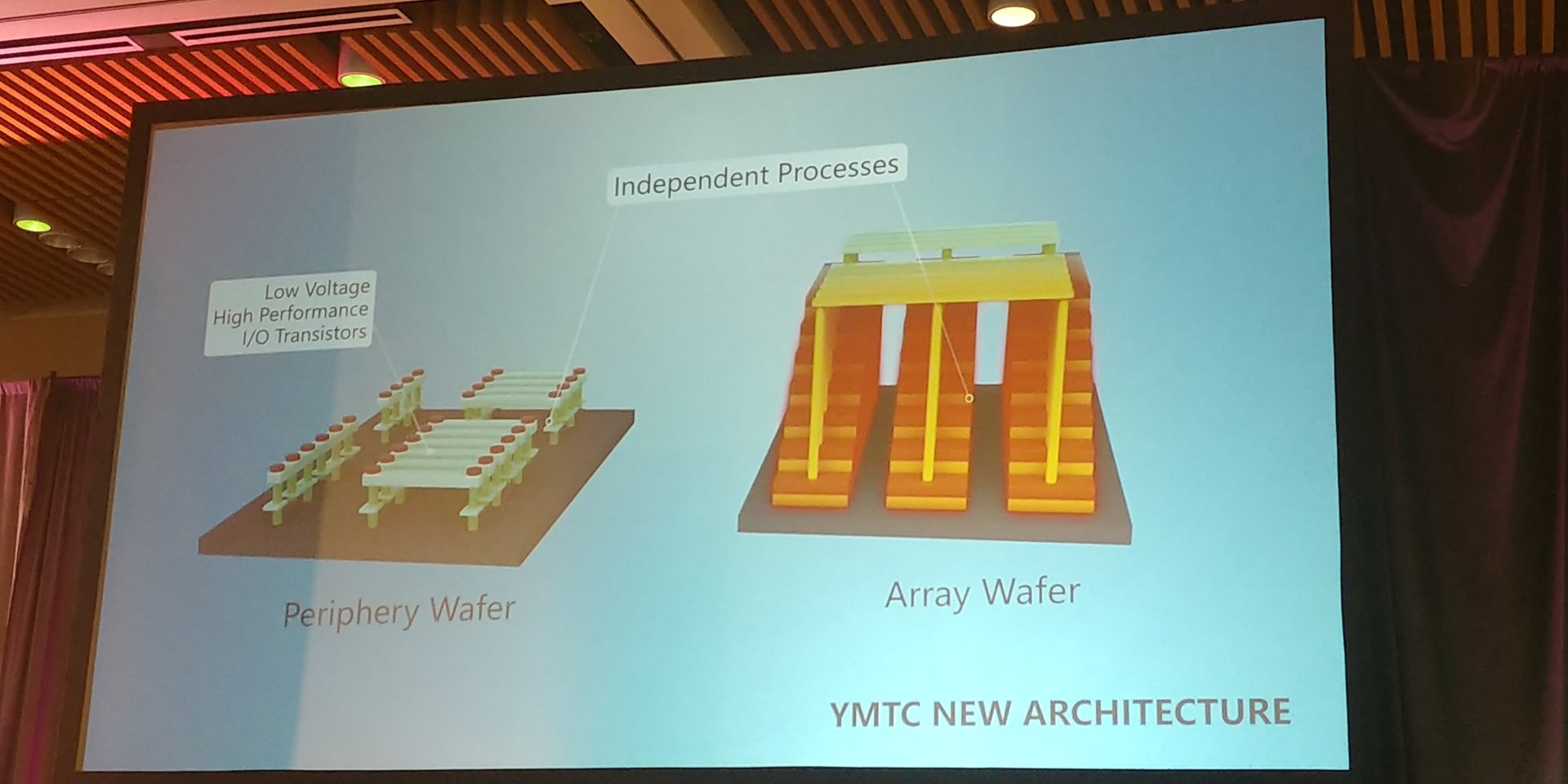

Mit der sogenannten Xtacking-Architektur verfolgt YMTC einen ähnlichen Ansatz wie Intel und Micron mit CMOS Under Array: Die Logikschaltkreise werden nicht wie sonst üblich neben dem Speicherbereich (Flash Array) sondern unter respektive über diesem in einer separaten Ebene platziert. Dadurch lässt sich die Fläche pro Chip reduzieren beziehungsweise besser für den eigentlichen Speicher ausnutzen. Die Chip-Fläche ist ein wesentlicher Faktor für die Kosten, denn je mehr Chips auf einen Wafer passen, umso besser.

-

Xtacking: I/O und Flash Array auf separaten Wafern (Bild: AnandTech)

Xtacking: I/O und Flash Array auf separaten Wafern (Bild: AnandTech)

Der neue Ansatz von YMTC ist, dass Chip-Logik (I/O) und Speicherbereich zunächst getrennt voneinander auf separaten Wafern gefertigt und erst später zu einem Speicherchip vereint werden. Obwohl somit zwei Wafer benötigt werden, sollen die Kosten insgesamt nicht steigen, da sich auf diesem Weg die Speicherdichte so weit optimieren lasse, dass sich der zusätzliche Wafer rentiert. Für den I/O-Chip verwende YMTC ein 180-nm-Verfahren, der Prozess für den 3D-NAND wurde nicht näher beschrieben. Die beiden Wafer sollen anschließend über Millionen von Metal VIAs (Vertical Interconnect Accesses) in einem einzelnen Produktionsschritt elektrisch verbunden werden.

Bis zu 3 Gbit/s I/O-Datenrate

Durch den modularen Ansatz verspricht sich YMTC auch eine um „mindestens drei Monate“ beschleunigte Produktentwicklung. Außerdem soll das Design hohe I/O-Datenraten von bis zu 3 Gbit/s ermöglichen. Dies wäre mehr als doppelt so schnell wie Samsungs fünfte 3D-NAND-Generation (V-NAND v5), die 1,4 Gbit/s erreicht, andere Hersteller sind bei etwa 1 Gbit/s angelangt. Allerdings ist nicht gesagt, dass bereits die 64-Layer-Generation von YMTC diese Geschwindigkeiten bieten wird. Diese soll als TLC-3D-NAND mit drei Bit pro Speicherzelle und 256 Gbit pro Chip im kommenden Jahr in die Massenproduktion gehen. Die Konkurrenz ist dann bereits bei 96-Layer-Chips mit bis zu 1,33 Terabit angelangt.

Die Firma Yangtze Memory Technologies Co. (YMTC) ist erst im Sommer 2016 unter Federführung der chinesischen Regierung entstanden, nachdem die Tsinghua Unigroup eine Mehrheit am Auftragshersteller XMC erworben hatte, der schon zuvor die Errichtung der Mega-Fab angekündigt hatte. Das Know-How für die 3D-NAND-Produktion stammt aus einer Kooperation von XMC und Spansion. Der CEO Simon Yang hat früher unter anderem für Intel und XMC gearbeitet.

In die Fertigungsanlage in Wuhan sollen rund 24 Milliarden US-Dollar geflossen sein – nur ein Teil der rund 100 Milliarden US-Dollar umfassenden Speicheroffensive Chinas.