Prozessorgerüchte: AMD Epyc 2 „Rome“ wird angeblich ein 9-Die-Chip

Seit Monaten ranken sich Gerüchte um den Aufbau der neuen Prozessorgeneration von AMD für das Serversegment, Codename Rome. Diese wird nicht auf größere CCX setzen, sondern den Multi-Chip-Modul-Ansatz noch weiter ausbauen. Dafür sind nicht nur mehr Dies mit CPU-Kernen erforderlich, vor allem das Fabric wird immer wichtiger.

Der Multi-Chip-Ansatz wird vorangetrieben

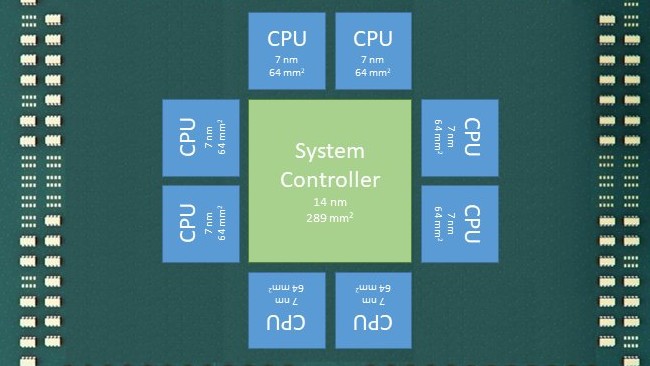

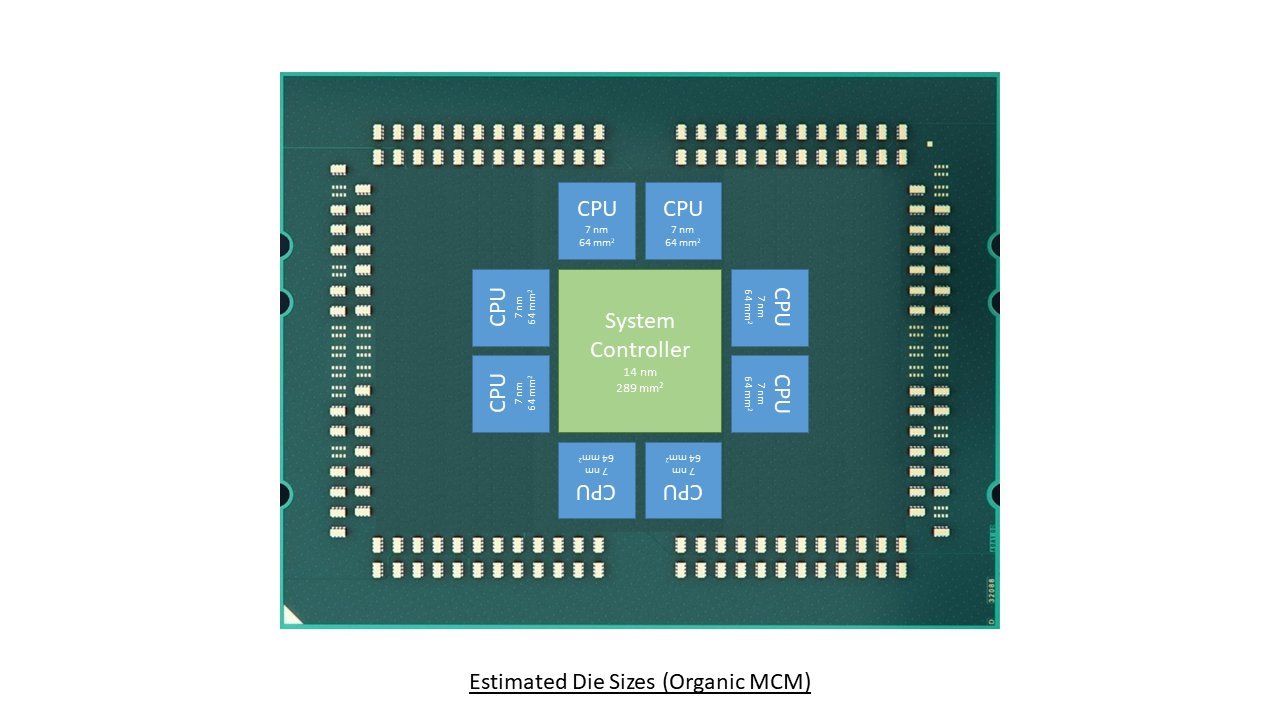

Bereits seit dem Frühjahr und vermehrt seit Sommer 2018 kristallisiert sich heraus, dass AMDs bisheriger Ansatz mit einem CPU Core Complex (CCX), bestehend aus vier Kernen und den notwendigen Caches, der je nach Einsatzgebiet mit weiteren CCX verbunden wird, auch in Zukunft so fortgesetzt wird. Bei den Server-Prozessoren wurden bisher acht CCX in vier Dies verbaut, in Zukunft sollen es acht Dies sein, zuzüglich einem Controller-Chip. Die neue 7-nm-Fertigung ermöglicht kleinere Chips als die bisher zu 213 mm² großen Lösungen führende 14-nm-Fertigung, sodass diese auf dem SP3-Package mit seinem 4.096 Kontaktflächen problemlos Platz finden.

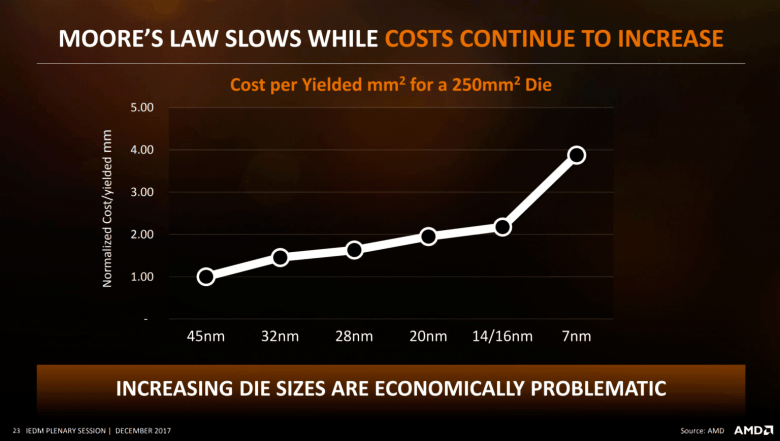

Ein Vorgehen mit kleineren Chips hatte AMD vor einem Jahr bereits einmal selbst angedeutet. Denn Chips werden mit der 7-nm-Fertigung deutlich teurer. Je größer die Chips sind, desto höher steigt der Preis, zudem sinkt die Ausbeute und die Fehleranfälligkeit erhöht sich. Kleinere Chips nutzen jedoch den Platz eines 300-mm-Wafers besser aus, das hilft am Ende dabei, den Preis wieder etwas zu senken. AMDs bisher verfolgter Multi-Chip-Ansatz spielt dem Unternehmen also weiterhin in die Karten.

Unter anderem streut SemiAccurate seit einiger Zeit Berichte (hinter einer Paywall), die den Ansatz von AMD mit insgesamt 8+1 Dies untermauern. Die Seite beruft sich dabei auf multiple Quellen, passend dazu gibt es auf Twitter Enthusiasten, die sich der Gerüchte annehmen und daraus Blockdiagramme und Schaubilder erstellen. Diese haben keinen Anspruch auf Vollständigkeit oder der Wahrheit, doch geben sie einen Ausblick darauf, wie AMD einen schlagkräftigen Server-Prozessor mit 64 Kernen aufstellen könnte.

Demnach kommt dem neuen Controller-Chip als Weiterentwicklung respektive Evolution von Infinity Fabric eine extrem wichtige Aufgabe zu, indem das gesamte Management der CCX übernommen wird. Denn die Kommunikation der Kerne untereinander sowie die Ansteuerung der Caches und Speichercontroller in akzeptabler Latenz ist bei einem derartigen Ansatz eine große Herausforderung. Ein zentrales Steuerelement könnte dafür genau die Lösung sein, so sind die Wege in alle Richtungen gleich lang und die Latenzen entsprechend gering.

A few pictures to brighten your day, I hope.$AMD pic.twitter.com/PmnNErPr1v

— RetiredEngineer® (@chiakokhua) October 25, 2018

Erste offizielle Details in Kürze erwartet

In der kommenden Woche wird AMD auf einem Event in San Francisco über den Stand der Dinge berichten und einen Ausblick auf die Zukunft geben. Im Fokus steht dabei der Geschätsbereich Datacenter und die 7-nm-Fertigung, an erster Stelle rund um die Produkte Rome und Vega. ComputerBase wird vor Ort von der Veranstaltung berichten, zumindest das, was das NDA zulässt. Weitere Informationen werden in den Tagen und Wochen darauf folgen.