Halbleiterfertigung: TSMC feiert tape-out des ersten EUV-Chips

Auf dem OIP Ecosystem Forum hat TSMC das erste tape-out eines Testchips in 7 nm unter Nutzung von EUV-Lithografie (N7+) vermeldet. Im Frühjahr 2019 soll bereits mit 5 nm (N5) die sogenannte risk production beginnen, um rund ein Jahr später die Serienfertigung aufnehmen zu können. Es ist ein Meilenstein, vor allem für EUV.

EUV-Lithografie endlich am Ziel

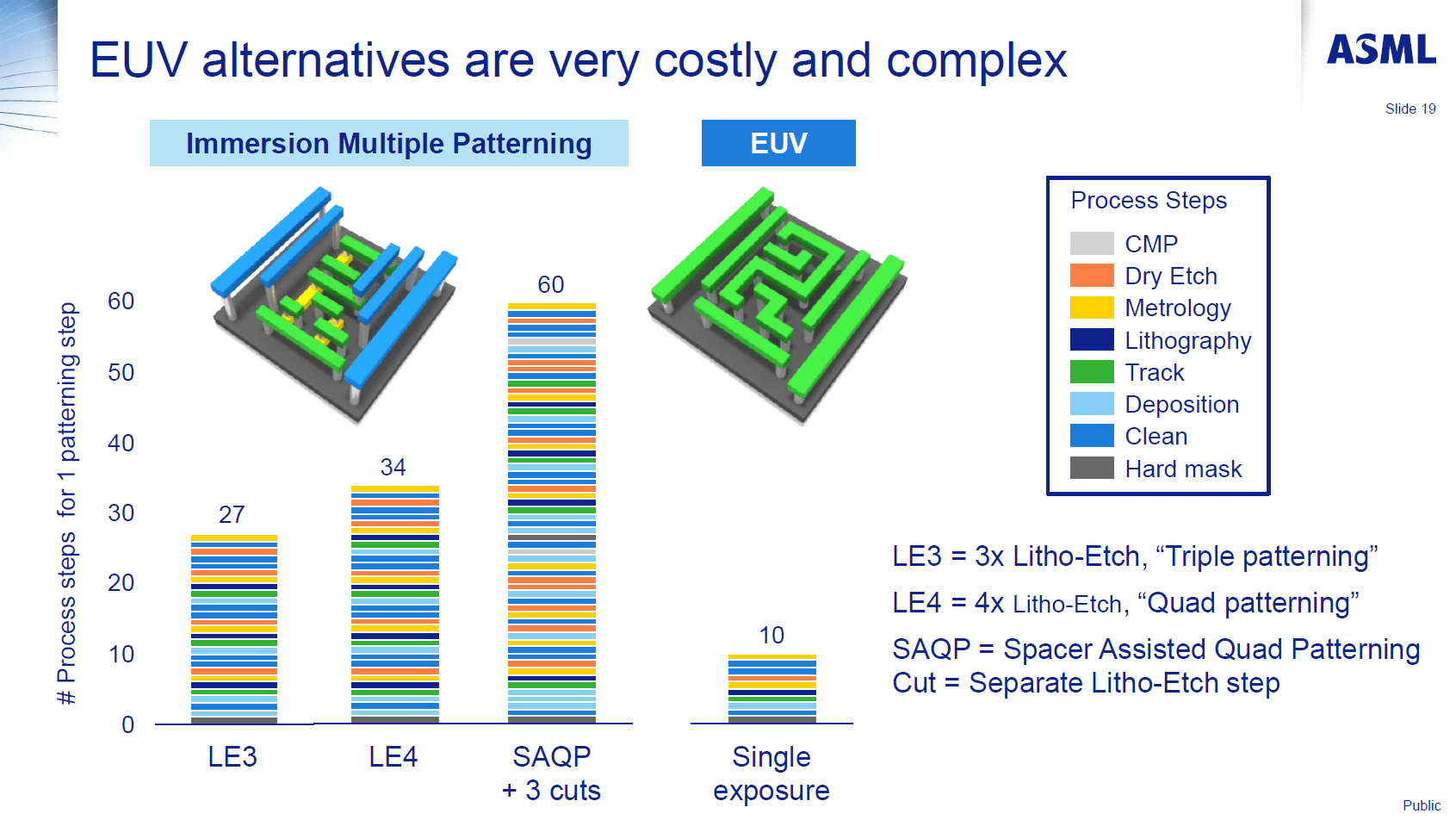

Nach jahrzehntelanger Forschung und Entwicklung mit unzähligen Rückschlägen und Verzögerungen ist die „extrem“ ultraviolette Lichtquelle (EUV) mit einer Wellenlänge von 13,5 nm bereit für den industriellen Einsatz in Belichtungsmaschinen. Und die Zeit könnte passender kaum sein, denn die Kosten beim Einsatz der klassischen Immersionslithografie mit 193-nm-Lichtquelle explodieren für High-End-Chips ab der 10- und 7-nm-Produktion. Denn die Chips können nur noch mit unzähligen Belichtungsschritten und zusätzlichen Eingriffen gefertigt werden, jeder Zwischenschritt ist dabei wieder anfällig für kleinste Fehler, sodass am Ende die Ausbeute darunter leiden kann. Exakt dieses Desaster erlebt Intel mit der 10-nm-Fertigung auf Basis von erweitertem Quad Patterning (SAQP) aktuell, die im Beispielbild von AMSL ziemlich exakt im Bereich der letzten Stufe regulärer Scanner arbeiten.

Der nun angestrebte Serieneinsatz kommt mit jahrelanger, sogar jahrzehntelanger Verzögerung. Mitte der frühen 2000er-Jahre war die ursprüngliche Einführung von EUV bereits spät dran, bei Intel wurde seinerzeit beispielsweise die 32-nm-Fertigung ab 2009 angestrebt – die erfolgreiche CPU-Familie Sandy Bridge hätte demnach bereits mit EUV belichtet werden sollen.

EUV bei TSMC bereits ab N7+

TSMC wird in der 2019 anstehenden 5-nm-Fertigung EUV für den Einsatz von bis zu 14 Layern nutzen. Um auf dem Weg dahin aber noch einige Erfahrungswerte mit dem Umgang mit der neuen Technologie zu sammeln, wird TSMC wie auch Samsung eine verbesserte 7-nm-Fertigung anbieten, bei denen einige der Lagen mit EUV belichtet werden, die weiteren dann mit klassischem Verfahren. TSMC beschreibt das Maximum bei der N7+ getauften Fertigungsstufe mit vier EUV-Layern. Während N7+ gegenüber N7 kaum Leistungsvorteile bieten wird und lediglich die Fertigung anpasst und optimiert, wird N5 einen größeren Sprung ermöglichen.

In den vergangenen Tagen hatten bereits große Zulieferer für TSMC, die die Ausrüstung und Tools für den neuen Prozess bereitstellen, die Zusammenarbeit mit den Taiwanern bei den nächsten großen Fertigungsschritten vermeldet. Cadence und Mentor heben dabei explizit auch die Zusammenarbeit bis zu 5 nm und EUV hervor. Einige der genutzten Bibliotheken sind aber noch nicht im finalen Zustand, beschreibt EE Times, sie werden je nach Modul zwischen November und auch erst Mitte des kommenden Jahres erwartet. Letzteres soll unter anderem PCI Express 4.0 und USB 3.1 betreffen, deren sogenannte „IP-Blöcke“ erst noch für die EUV-Produktionsprozesse angepasst werden müssen.