Huawei HiSilicon Hi1620: ARM-Server-Prozessor mit 64 Kernen in 7 nm

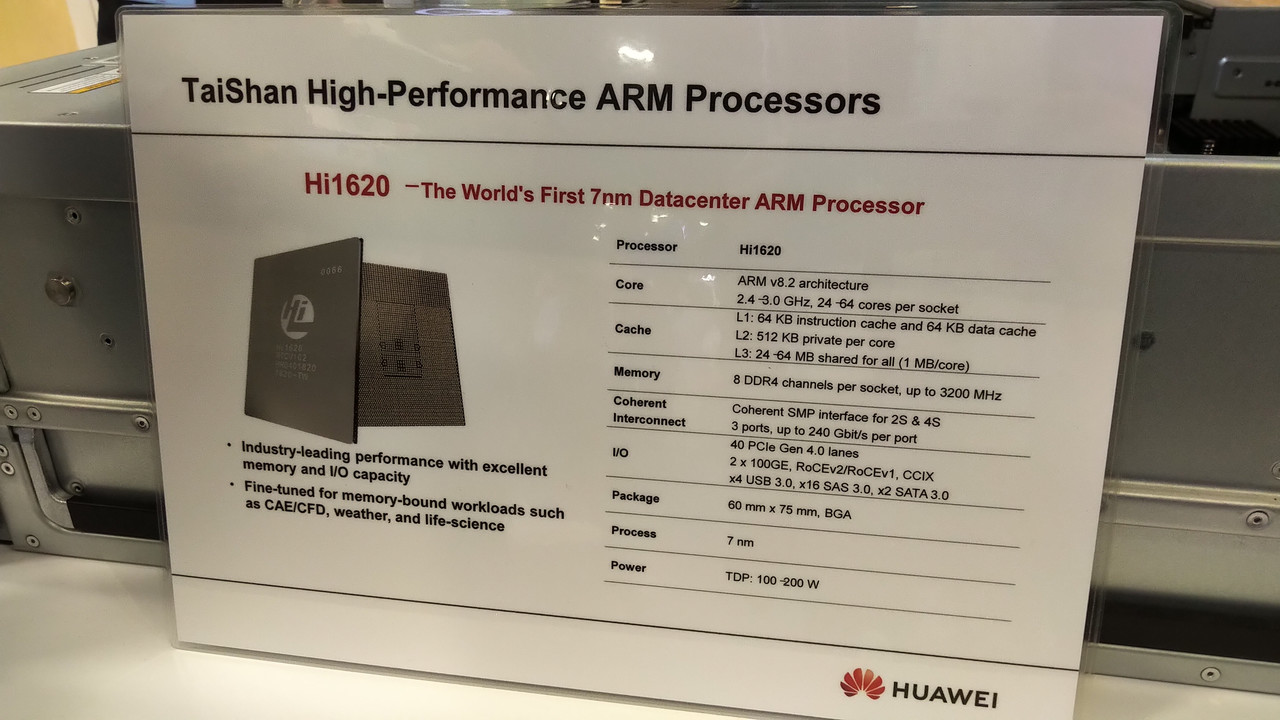

Die beiden x86-Giganten AMD und Intel sind nicht die einzigen Hersteller, die Prozessoren mit sehr vielen Kernen für Server anpeilen. Mit HiSilicon will auch Huawei die Produktpalette im Serverbereich weiter ausbauen, geplant ist ein 7-nm-Prozessor auf Basis der ARM-Architektur mit 24 bis 64 Kernen.

Neue Designs im Jahresrhythmus

Huawei legt eine beeindruckende Entwicklung an den Tag, die Frequenz neuer Chip-Design für Server ist ähnlich hoch wie in der mobilen Sparte. Im Jahr 2015 hat Huawei mit dem HiSilicon Hi1610 den ersten 16-Kern-ARM-Prozessor auf Basis von Cortex-A57-Kernen vorgestellt, der im Jahr darauf leicht überarbeitet wurde. 2017 folgte der Wechsel zu Cortex-A72, einhergehend mit einer Verdoppelung der Kerne sowie einer kompletten Überarbeitung.

Mit dem Hi1620 wird erneut ein Architekturwechsel angestrebt, Ares heißt die Neuauflage von ARM, über die bisher jedoch kaum Details bekannt sind. Es scheint sich aber um einen High-Performance-Ableger der Cortex-A76 zu handeln, die ARM bereits für das mobile Segment enthüllt hat. Passenderweise enthüllt Huawei einige der technischen Details, die sich mit dem Cortex-A76 decken. TSMC wird in beiden Fällen die Fertigung in 7 nm übernehmen.

Die Überarbeitungen der Architektur fangen bereits beim L1-Cache an, der gegenüber dem Vorgänger stetig aufgebohrt wird. 64 KByte jeweils für L1I und L1D entsprechen noch einmal 50 respektive 100 Prozent mehr als zuvor. Der 512 KByte große L2-Cache wird fortan jedem Kern exklusiv zur Verfügung stehen, bisher wurden diese Ressource jeweils über vier Kerne geteilt. Der L3-Cache wird als letzte Ausbaustufe weiterhin ein Shared-Cache sein, er ist abhängig von der Anzahl der CPU-Kerne und wird aktuell mit 1 MByte pro Kern beziffert.

Aufgewertet wird auch das Speicherinterface. Acht Speicherkanäle sollen mit DDR4-3200 umgehen können, für Konnektivität stehen 40 PCI-Express-4.0-Lanes, Dual-100-Gigabit-Ethernet sowie diverse Anschlüsse für Massenspeicher zur Verfügung. Die neuen Prozessoren sollen in Systemen mit bis zu vier Sockeln zusammengeschaltet werden können, ein noch unbekannter Interconnect soll 240 GB/s Bandbreite pro Anschluss bieten. Verpackt wird der Chip in einem BGA-Package mit einer TDP von 100 Watt bis 200 Watt, bis zu 3 GHz Takt sollen möglich sein. Finale Details sind im kommenden Jahr zu erwarten.