Foveros: Intel will unterschiedliche Chips in Zukunft stapeln

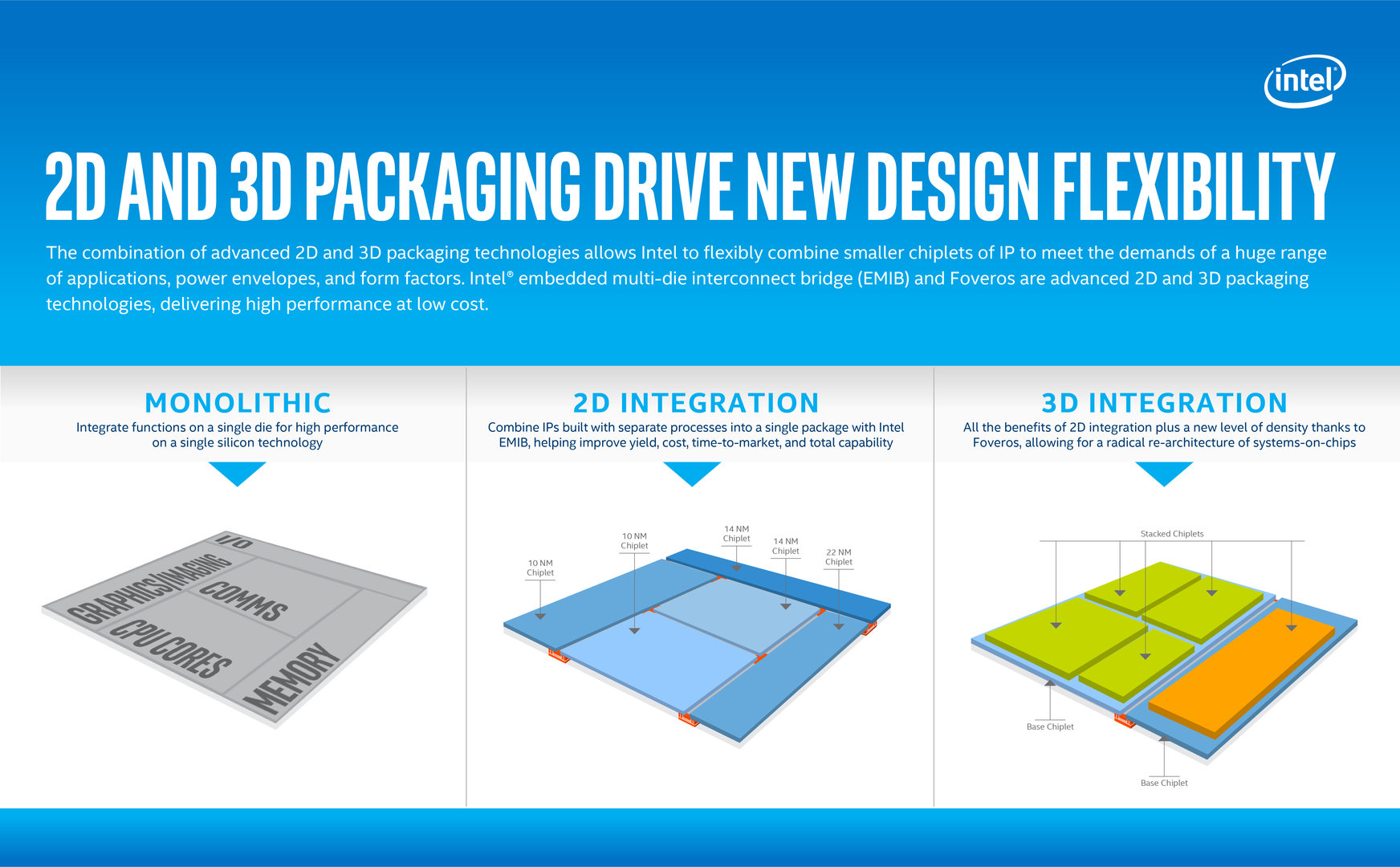

Intels EMIB-Ansatz für multiple Chips auf einem Package wird ab 2019 stärker verfolgt und sogar noch ausgebaut. Zusammen mit übereinander gestapelten Chips (3D Stacking) mit verschiedenen Funktionen sollen so völlig neue Produkte ermöglicht werden.

Foveros steht für das Stapeln von Chips unterschiedlicher Art

Stapelbare Chips gibt es bereits seit längerer Zeit, im Flash- und DRAM-Geschäft sind sie derzeit vornehmlich anzutreffen (zum Beispiel 3D-NAND). Doch Logik-Chips übereinander zu stapeln wäre neu. Intel will nach jahrelanger Forschung jetzt aber einen Weg gefunden haben.

Bereits in den frühen 2000er Jahren versuchte sich Intel an mehreren Methoden, verschiedene Bausteine eines Systems durch Stapeln zu vereinen. Aber erst die jüngeren Erfolge wie das 2,5D-Stacking inklusive Interposer, wie sie von mehreren Firmen verfolgt werden, oder Intels eigenen EMIB-Ansatz gaben nun die finale Richtung vor.

Denn kombiniert mit der Embedded Multi-die Interconnect Bridge (EMIB), die bisher ein Zusammenspiel von mehreren Chips in der zweiten Dimension ermöglichte und mit Kaby Lake-G ein Vorzeigeprodukt im Markt präsentiert hat, sollen durch den Ausbau in die dritte Dimension ganz neue Produkte möglich werden. Foveros nennt Intel diesen Ansatz, der die Kombinationsmöglichkeiten kaum noch einschränken soll. Intel veranschaulicht das anhand erster möglicher Lösungen für den Client-Markt, aber auch anhand von FPGAs, die für hochspezialisierte Anwendungsfälle entworfen werden.

Foveros startet mit einer 22-nm-Bodenplatte

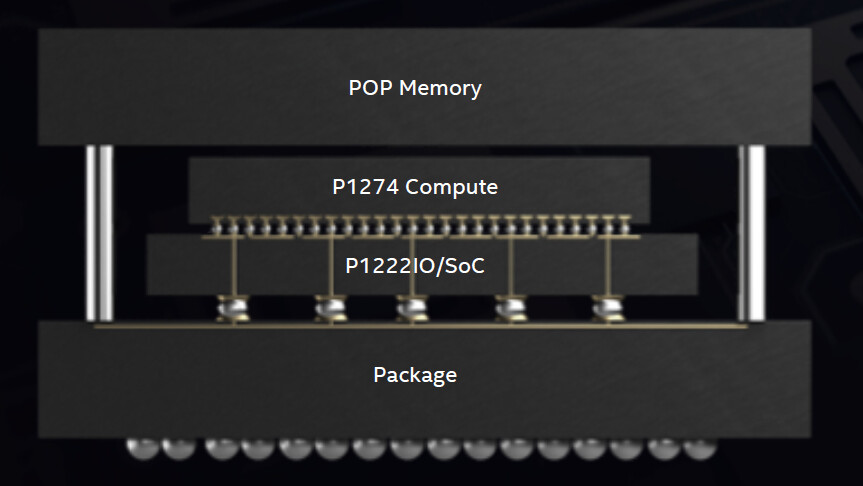

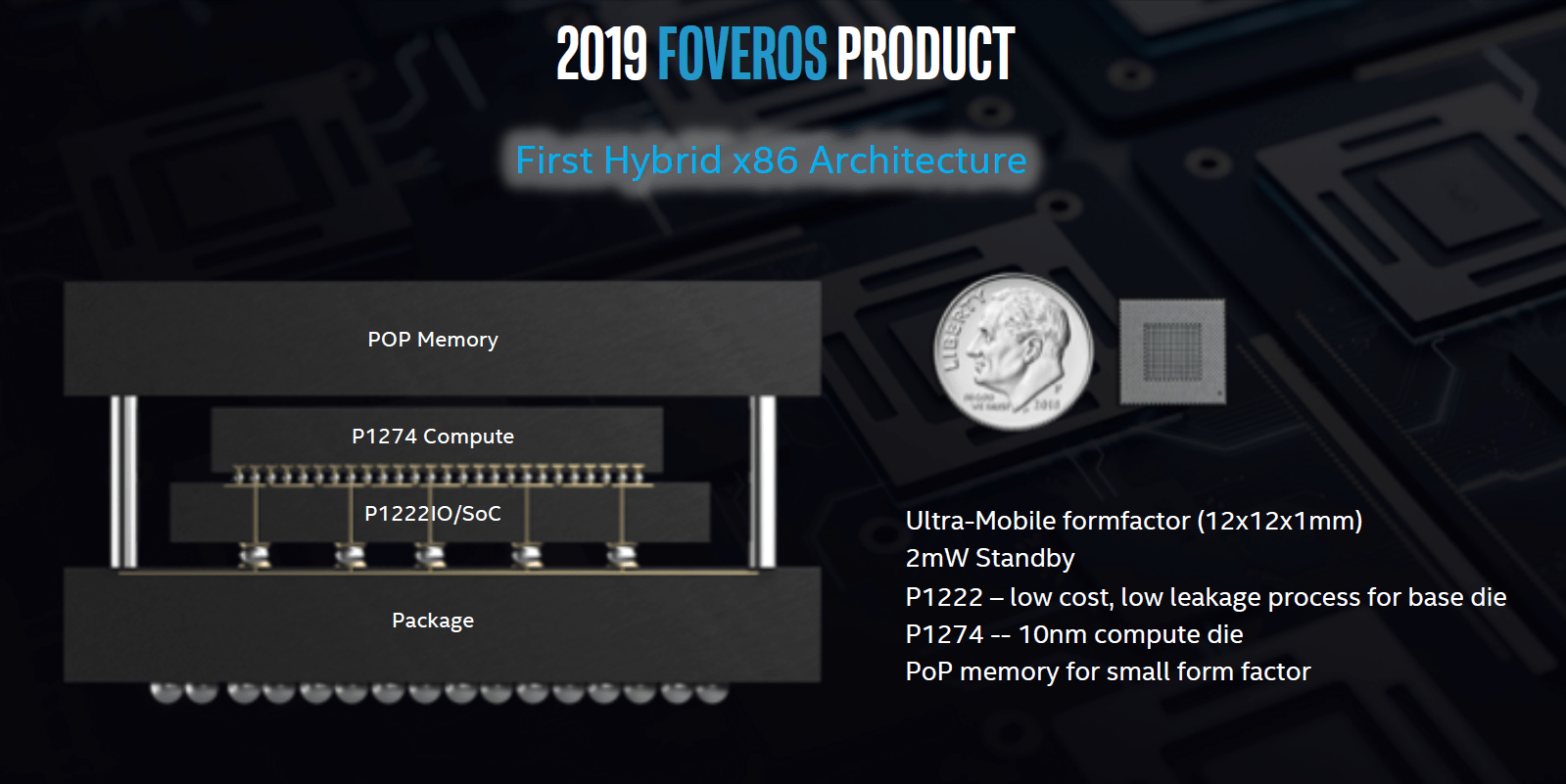

In Foveros werden mehrere bekannte Technologien vereint, um ein gestapeltes System-in-Package zu bauen. Das klassische Package bildet immer die „Bodenplatte“, darüber folgt ein für das System wichtiges Bauteil, in dem I/O, SRAM und beispielsweise die Stromversorgung liegen können und das klassisch mit dem Package verlötet ist. Der wiederum darauf gestapelte Chip ist auf der einen Seite direkt mit dem I/O-Chip verbunden, durch Thru-Silicon Via (TSV) aber auch mit der Bodenplatte. Unabhängig von den beiden ersten Chips kann mit der Bodenplatte auch noch ein ganz anderes Bauteil verbunden werden, wie Intel in seinem ersten Design zeigen will.

Das erste Produkt von Intel soll im zweiten Halbjahr 2019 ein 10-nm-Prozessor auf einem 22-nm-Chip sein und darüber positionierten Speicher auf einem 12 × 12 × 1 mm kleinem Package werden, vermutlich der eigentlich bereits zur Computex 2018 geplante aber verschobene Lakefield. Dieses soll als Komplettpaket eine sehr hohe Leistung bei geringerem Energiebedarf auf kleinem Raum bieten. Ein neu aufgelegter Compute Stick könnte so beispielsweise mit vielfältigen Möglichkeiten auf kleinstem Raum aufwarten. Aber auch Mini-PCs aus der Serie NUC oder kleine und leichte Notebooks könnten in Zukunft auf einem Stapelchip eventuell nicht der ersten, aber der darauffolgenden zweiten Generation aufbauen. Denn diese ist bereits geplant. Die Bodenplatte wäre dann nicht mehr aus der 22-nm- sondern 10-nm-Fertigung, Chips darauf könnten dann bereits 7-nm-CPUs sein.

ComputerBase hat Informationen zu diesem Artikel von Intel unter NDA erhalten. Die einzige Vorgabe war der Veröffentlichungszeitpunkt.