Sunny Cove: Erste Details zu Intels neuer CPU-Architektur

Auf dem Architecture Day hat Intel erstmals Details zur neuen CPU-Architektur Sunny Cove bekannt gegeben, die Grundlage der Ice-Lake-Prozessoren ist. Sie wird ab dem kommenden Jahr die Skylake-Architektur beerben, die dann vier Jahre in mehreren Generationen bis zur aktuellen Coffee-Lake-Familie genutzt wurde.

Sunny Cove heißt die neue CPU-Architektur

Ice Lake ist der Codename für die kommenden ersten 10-nm-Prozessoren für alle Märkte, doch besteht er aus mehreren Teilen, allen voran CPU und GPU. Der Prozessorteil trägt den Codenamen Sunny Cove (oder auch Sunnycove) und ist die erste neue Architektur seit Skylake und damit seit vier Jahren. Entsprechend groß sind die Erwartungen, einige Details hat Intel nun bestätigt.

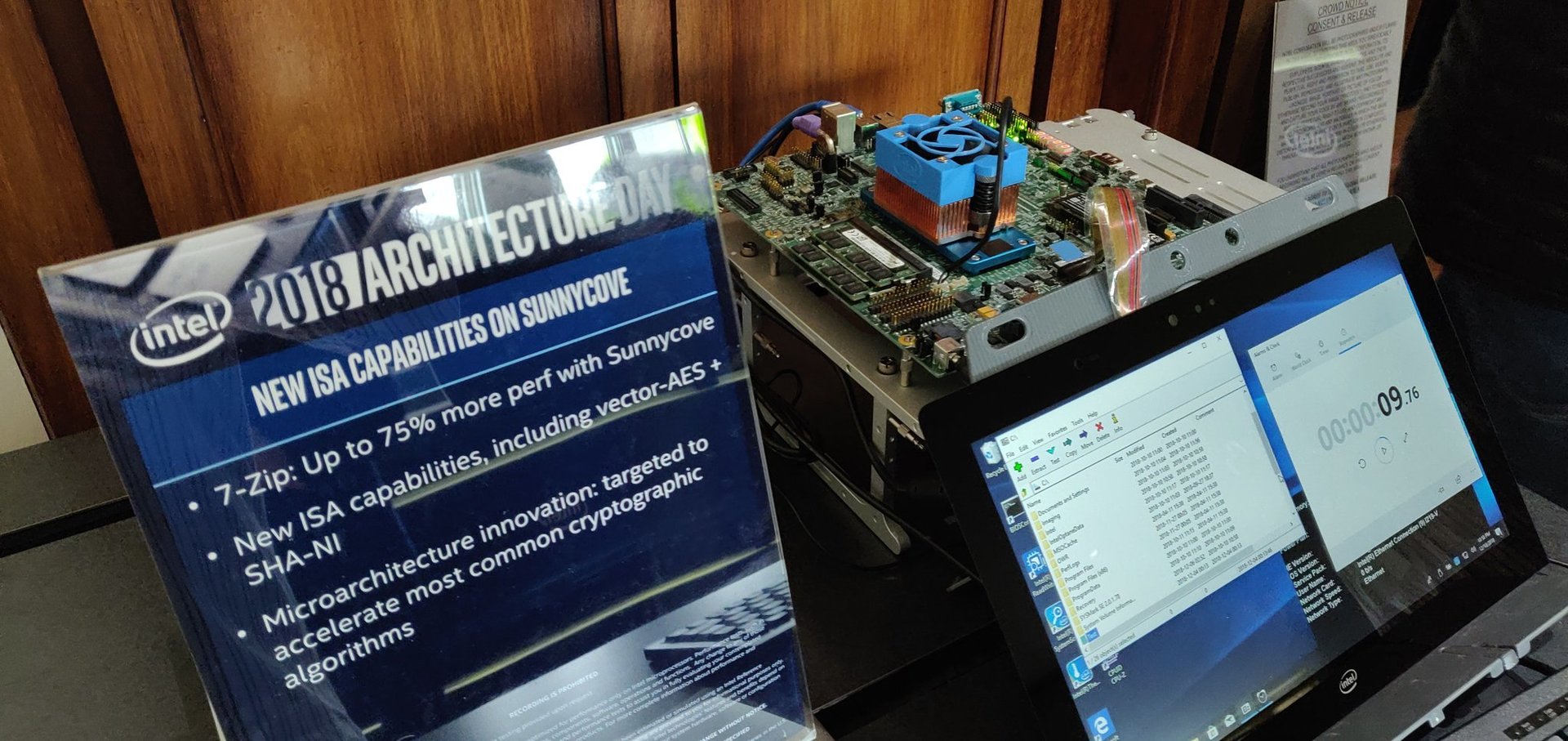

Die neue Architektur legt den Fokus auf zusätzliche parallele Ausführungen zur gleichen Zeit, reduzierte Latenzen durch neue Algorithmen, mehr Leistung durch vergrößerte Buffer und Caches sowie neue Befehlssatzerweiterungen. Vector-AES und SHA-NI sollen beim Packen, Entpacken und der Verschlüsselung von Datenpaketen helfen. Passend dazu hatte Intel eine erste Demo mitgebracht: Auf einer CPU-Validierungsplattform für Notebook-Chips zeigte der Hersteller mit Ice Lake-U in 7-Zip 75 Prozent Leistungszuwachs gegenüber dem Vorgänger.

Erste Details zum Aufbau

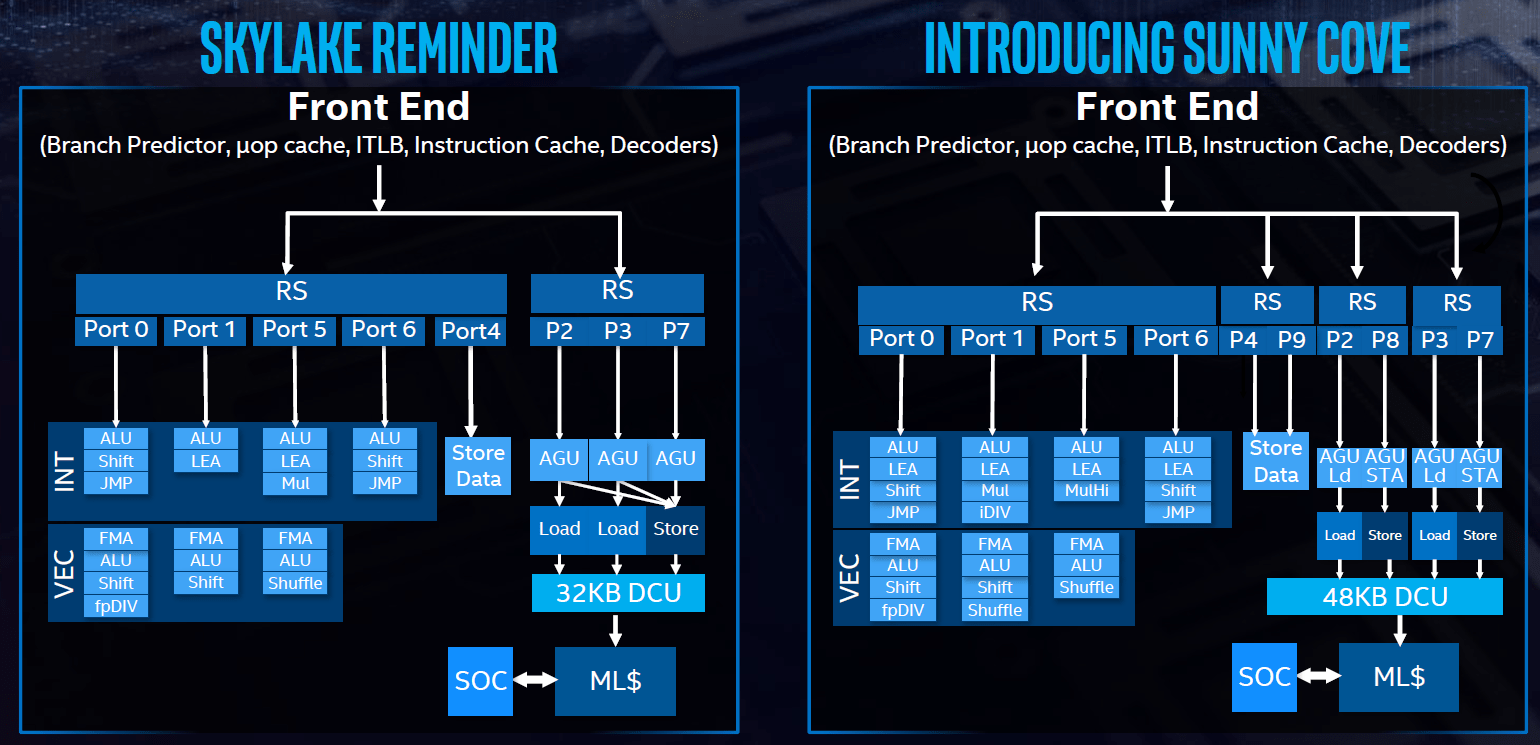

Intel hat im Rahmen der Veranstaltung die ersten tiefer gehenden Details zur Architektur der Prozessoren preisgegeben. Dies beginnt traditionell im Front End, das die Sprungvorhersage, aber auch den Micro-op Cache, L1-Instruktion-Cache, ITLB sowie Decoder enthält. In all diesen Bereichen wurde bereits optimiert, Caches vergrößert. Die größten Anpassungen erfolgen aber dann auf dem Weg zum sogenannten Back-End und beginnen bei einer neuen 5-Wide-Out-of-Order-Architektur-Pipeline.

Bei Haswell war es noch eine Unified Reservation Station (RS) für acht Ports, ab Skylake waren es bereits zwei getrennte für weiterhin acht Ports, nun sind sogar vier sogenannte Reservation Station für zehn Ports. Heraus kommt eine deutlich erhöhte Parallelisierung in gewissen Bereichen. Während die ursprünglichen Ports nahezu gleich bleiben und nur im Detail geändert werden, bekommt die AGU (Adress-Generierungs-Einheit) für Speicherbefehle nun insgesamt vier Ports zugewiesen, wobei jeweils zwei vollständig mit Load/Store-Einheiten versehen wurden. Bisher war Port 7 als exklusiver Store für Port 2 und 3 gedacht, damit dort neue Loads aufgefangen werden konnten. Um die neuen Store-Einheiten mit notwendigem Rückhalt zu versehen, wird in dem Bereich der L1-Datencache um 50 Prozent auf 48 KByte ausgebaut.

Doch die vermeintlichen Kleinigkeiten, die Intel noch geändert und integriert hat, sind zum Teil mit größeren Auswirkungen versehen als auf den ersten Blick sichtbar, erklärte Intel. Eine weitere Shuffle-Einheit hier, ein zusätzlicher Integer Divider da und mehr kommen beispielsweise auch den zusätzlich neu unterstützten Instruktionen zugute. Aber auch an eine vergrößerte maximale Speicherkapazität sowie zusätzliche Sicherheitsfeatures hat Intel gedacht.

Intels Ausblick für 2019 und darüber hinaus

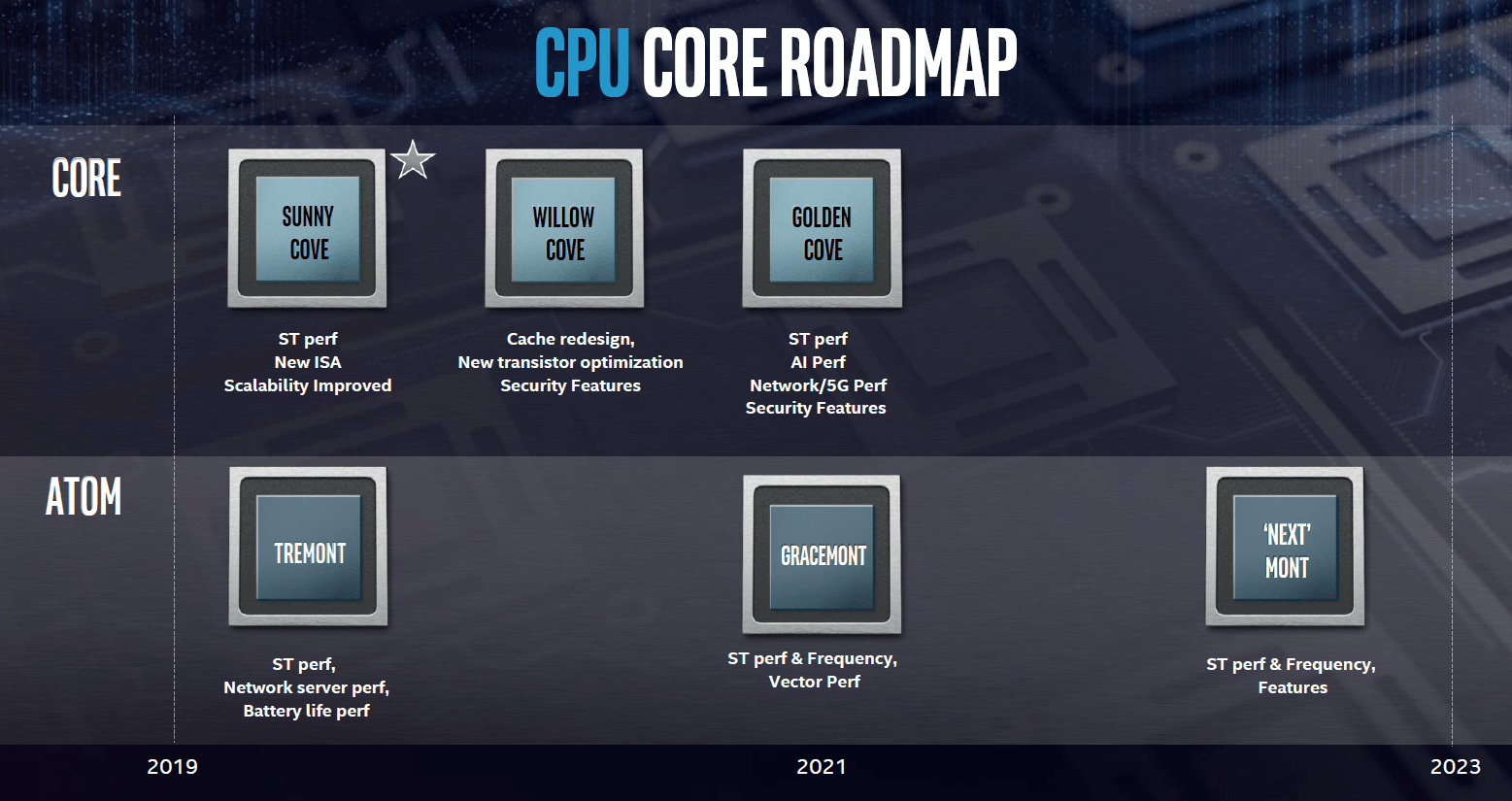

Laut Intel wird die neue Architektur durch das Gesamtpaket an „reduced latency and high throughput, as well as much greater parallelism“ gleichermaßen für Gaming bis hin zum Data-Center geeignet sein. Sie ist deshalb die Basis für alle kommenden Produkte aus den Serien Intel Core und Intel Xeon, die ab 2019 in 10 nm gefertigt und ausgeliefert werden. Sunny Cove ist dabei nur der Grundstein, jeweils binnen eines Jahres sollen Willow Cove und Golden Cove folgen.

ComputerBase hat Informationen zu diesem Artikel von Intel unter NDA erhalten. Die einzige Vorgabe war der Veröffentlichungszeitpunkt.