LPDDR5: Neuer Speicherstandard ist 50 Prozent schneller

Die JEDEC hat mit LPDDR5 eine neue Version des sparsamen Arbeitsspeichers für Mobilgeräte verabschiedet. Die Bruttodatenrate steigt auf bis zu 6.400 Mbit/s, was gegenüber LPDDR4 ein Plus von 50 Prozent bedeutet. Dafür wurde die Architektur des Low-Power DDR SDRAM neu gestaltet.

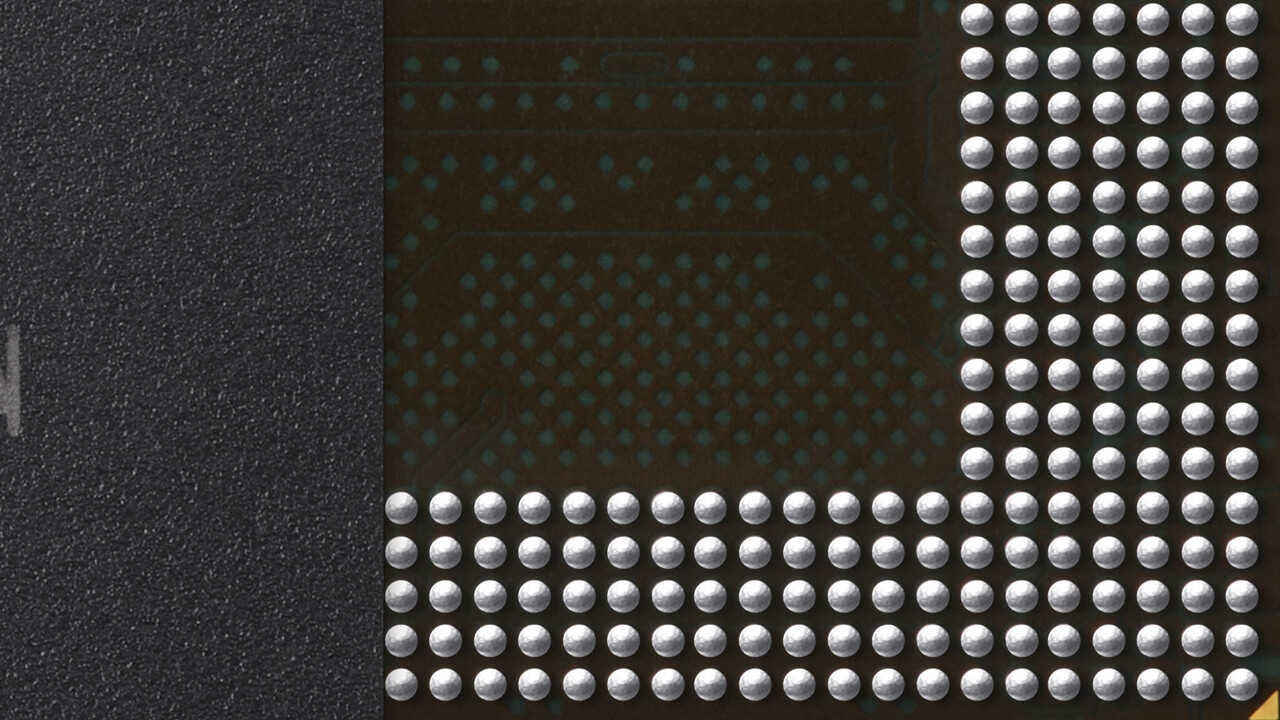

Für regelmäßige Leser von ComputerBase kommt der LPDDR5-Standard nicht überraschend, denn der Speicherhersteller Samsung hatte bereits im vergangenen Sommer die Entwicklung seines ersten LPDDR5-Speichers abgeschlossen und die wesentlichen Eckdaten genannt. Jetzt folgte die offizielle Verankerung des Standards in Form der Spezifikation JESD209-5 durch die JEDEC Solid State Technology Association. Neben Samsung ist auch LPDDR5 von Micron und SK Hynix zu erwarten.

LPDDR5 bringt 50 Prozent mehr Durchsatz

Die wesentliche Neuerung ist die erneut angehobene I/O-Datenrate, die bei LPDDR5 maximal 6.400 Mbit/s pro Pin beträgt. LPDDR4 war zunächst mit der Hälfte, also 3.200 Mbit/s, gestartet, bot im Laufe der Zeit aber bis zu 4.266 Mbit/s. Gemeint ist die Bruttodatenrate, die netto nutzbare Datenübertragungsrate liegt durch den Overhead niedriger.

Pro Kanal unterstützt LPDDR5 nun 16 Memory Banks, was eine Verdoppelung gegenüber den 8 Banks bei LPDDR4 bedeutet. Dies sowie die differenzielle Signalübertragung der „multi-clocking architecture“ trägt zur Leistungssteigerung bei. Der sogenannte WCK Clock kann die doppelte oder gar vierfache Datenrate des internen Command-Interfaces bieten, was für einen deutlichen Leistungsschub sorgt.

Neuer Ruhemodus spart Strom

Der im Vorfeld beschriebene Deep Sleep Mode (DSM) soll derweil Strom sparen. Samsung hatte eine bis zu 30 Prozent niedrigere Leistungsaufnahme gegenüber LPDDR4 in Aussicht gestellt. Optional wird mit Link ECC eine zusätzliche Fehlerkorrektur geboten, die im Automotive-Bereich Verwendung finden soll.

Die LPDDR5-Speicherchips werden voraussichtlich vor allem in Mobilgeräten wie Smartphones und Tablets als auch in Systemen für Fahrzeuge eingesetzt. Samsung versieht aber auch seine Solid State Drives (SSD) mit LPDDR-Chips als Cache.

- I/O throughput up to 6400 Mbps

- Signaling voltage – 250mV

- Non-Target ODT for DQ was added to support higher data rate

- Signal integrity enhancement by DFE

- Clocking architecture: WCK & Read Strobe (RDQS) added to support higher data rate

- Programmable Multi-bank organization (8Banks, 4Bank groups/4Banks, and 16Banks)

- Selectable background and command based ZQ calibration

- Low-power features added include

- Dynamic Frequency and Voltage Scaling for Core and I/O

- Selectable differential and single-ended CK, WCK, and RDQS

- Partial array self-refresh and auto-refresh

- Low power read/write operation with Data-Copy and Write-X functions

- Function/Features targeting automotive applications including

- Optional Link ECC

- New packaging definition