Toshiba auf der ISSCC: BiCS5-NAND mit 128 Layern und die höchste Datendichte

Zur ISSCC geben Toshiba und Western Digital einen Ausblick auf die kommende 3D-NAND-Generation mit 128-Layer-Architektur (BiCS5). Eine TLC-Variante im 4-Plane-Design soll eine hohe Schreibleistung liefern. Zudem gibt es nähere Details zum QLC-NAND mit der bis dato größten Speicherkapazität von 1,33 Terabit.

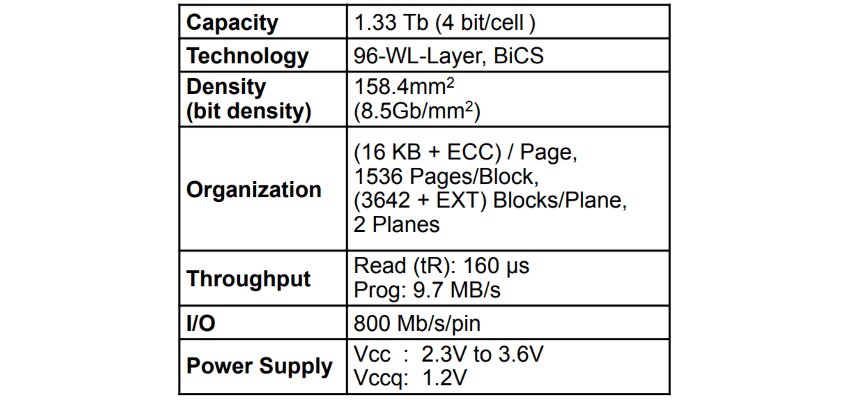

Bereits im August hatten Toshiba und Western Digital neuen 3D-NAND mit vier Bit pro Speicherzelle (QLC) und 96-Layer-Architektur der aktuellen Generation BiCS4 angekündigt, der mit 1,33 Terabit pro Chip (Die) die bisher größte Speicherkapazität für NAND-Flash bietet. Die Konkurrenz liefert bis dato maximal 1 Terabit pro Die.

In einer Präsentation auf der diesjährigen International Solid-State Circuits Conference (ISSCC) lieferten Toshiba und Western Digital nähere Details zu den 1,33-Tbit-Chips. Demnach besitzen diese eine Fläche von 158,4 mm², was auch als Die-Size bezeichnet wird. Daraus ergibt sich eine Speicherdichte von rund 8,5 Gigabit pro mm², die nach Kenntnis der Redaktion aktuell größte Datendichte für 3D-NAND.

Bei QLC-NAND müssen 16 Spannungszustände pro Speicherzelle unterschieden werden, was den Speichervorgang und die Fehlerkorrektur komplex gestaltet. Daher verwundert es nicht, dass QLC-SSDs wie die Intel 660p, die Crucial P1 oder die Samsung 860 QVO unter einer Schreibschwäche leiden und jenseits des SLC-Schreibpuffers sogar teils langsamer als eine HDD arbeiten. Für SSDs mit höherer Leistung und Haltbarkeit ist daher TLC-NAND mit 3 Bit pro Speicherzelle und acht Spannungen die bessere Wahl. 2-Bit-MLC und SLC mit 1 Bit pro Zelle sind diesbezüglich noch besser aufgestellt, werden aufgrund der geringeren Datendichte und den damit verbundenen höheren Kosten jedoch fast nur noch in Nischenprodukten für das High-End-Segment eingesetzt.

Erste Details zu BiCS5 mit 128 Layern

Bei der kommenden fünften 3D-NAND-Generation (BiCS5) von Toshiba und Western Digital wird die Zahl der Zellebenen (Layer) auf 128 erhöht. In Verbindung mit einem „Circuit-Under-Array“-Design, bei dem die Chip-Logik in einer eigenen Ebene unter die Speicherebenen verfrachtet wird, soll die Speicherdichte weiter erhöht werden. Dies zeigt sich bei der zum ISSCC angekündigten TLC-Version des BiCS5 eindrucksvoll: Der 128-Layer-Chip bietet 512 Gigabit Speicherplatz auf nur 66 mm². Die Speicherdichte beträgt somit rund 7,8 Gbit/mm², was eine Steigerung von rund einem Drittel gegenüber BiCS4 in der TLC-Variante mit 512 Gbit auf 96 Layern bedeutet. Der BiCS5-TLC-NAND erreicht damit fast die Speicherdichte des 96-Layer-QLC-NAND und BiCS5 als QLC-Version sollte diese in Zukunft noch deutlich übertreffen.

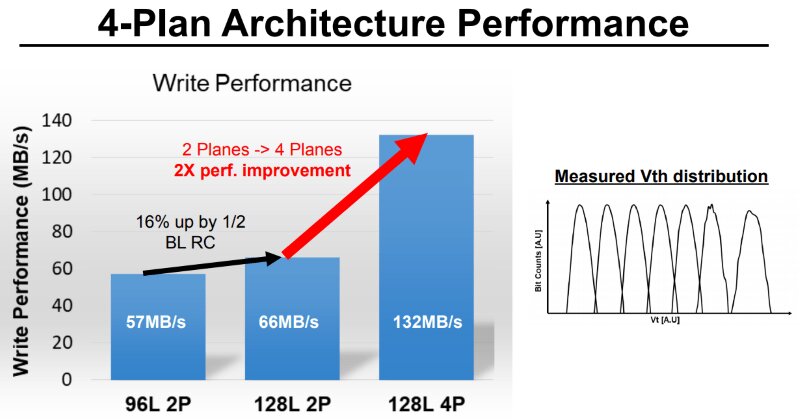

Bei dem 128-Layer-TLC-Chip soll außerdem ein 4-Plane-Design zum Einsatz kommen. Das bedeutet, dass der Speicherbereich in mehrere Abschnitte (Planes) auf dem Die unterteilt ist, die separat angesprochen werden, was eine höhere Schreibleistung durch parallele Zugriffe ermöglicht. Bei NAND-Flash sind zwei oder vier Planes üblich. Toshiba verspricht mit dem 4-Plane-Chip eine Verdoppelung der Schreibrate auf 132 MB/s gegenüber dem 96-Layer-NAND im 2-Plane-Design. Eine Grafik beschreibt aber auch eine 2-Plane-Version der 128-Layer-Generation, die mit 66 MB/s rund 16 Prozent schneller als der Vorgänger schreibt.

The 128-layer device is enabled by three key technologies, including a four-plane architecture with circuit-under-array technology to improve performance per bit density, a multi-die peak-power management system to manage power consumption and improve write throughput, and a 4-KB page-read mode to reduce power consumption, according to the paper.

EE Times

| Hersteller | Generation | Layer | Bit/Zelle | Kapazität/Die | Die-Fläche | Dichte |

|---|---|---|---|---|---|---|

| Toshiba/WD | BiCS3 | 64 | 3 (TLC) 4 (QLC) |

512 Gbit 768 Gbit |

132 mm² ? |

3,9 Gbit/mm² ? |

| BiCS4 | 96 | 3 (TLC) 4 (QLC) |

512 Gbit 1,33 Tbit |

86,1 mm² 158,4 mm² |

5,9 Gbit/mm² 8,5 Gbit/mm² |

|

| BiCS5 | 128 | 3 (TLC) 4 (QLC) |

512 Gbit ? |

66 mm ² ? |

7,8 Gbit/mm² ? |

|

| Samsung | V-NAND V4 | 64 | 3 (TLC) 4 (QLC) |

512 Gbit 1 Tbit |

128,5 mm² 181,9 mm² |

4,0 Gbit/mm² 5,6 Gbit/mm² |

| V-NAND V5 | 96 | 3 (TLC) 4 (QLC) |

256 Gbit bis 1 Tbit |

? | ? | |

| Intel/Micron | Gen 2 | 64 | 3 (TLC) 4 (QLC) |

256/512 Gbit 1 Tbit |

59 mm² (256 Gbit) ? |

4,3 Gbit/mm² (256 Gbit) ? |

| Gen 3 | 96 | 3 (TLC) 4 (QLC) |

512 Gbit ? |

? | ? | |

| SK Hynix | 3D V4 | 72 | 3 (TLC) | 256/512 Gbit | ? | ? |

| 3D V5 („4D“) | 96 | 3 (TLC) 4 (QLC) |

512 Gbit/1 Tbit 1 Tbit |

? | ? | |

| YMTC | Gen 1 | 32 | ? | ? | ? | ? |

| Gen 2 | 64 | 3 (TLC) | 256 Gbit | ? | ? |