AMD-Gerüchte: Termine raten, Leistung erraten und das Stacking

Mai, Juni, Juli oder August, September und Oktober – eine neue Woche und neue Gerüchte über AMDs Produktstart von CPUs und GPUs. Ebenfalls mit dabei sind die stetig geschürten Hoffnungen auf „noch mehr“ CPU-Leistung mit Ryzen 3000 sowie AMDs Bekenntnis zum Stacking, welches jedoch quasi nichts mit Intel zu tun hat.

Stacking in aller Munde

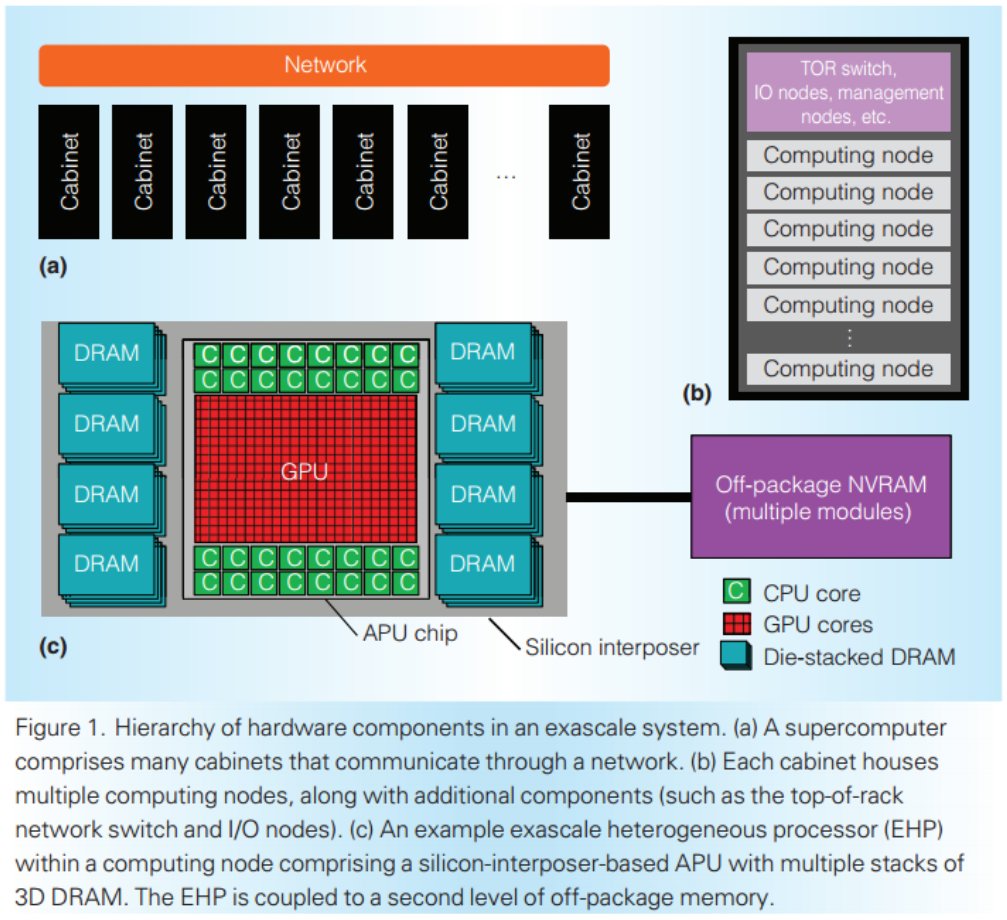

Wenngleich in Medien über das Wochenende primär der Vergleich von AMD mit Intel angebracht wurde, liegen die Themenbereiche doch unter dem Begriff sehr weit auseinander. AMD will Speicher auf Chips/Packages stapeln, einen Ansatz, den das Unternehmen nicht erst seit kurzer Zeit verfolgt, sondern schon fast ein Jahrzehnt, respektive bereits seit 2007 mit einem Design experimentierte, welches einen Chip samt Speicher auf einem Package unterbrachte. Die ganzen Zwischenlösungen wurden jedoch über einen Interposer an den Start gebracht, marktreif ist beispielsweise ein echtes Wafer-Stacking bei TSMC in der Fertigung seit dem letzten Jahr. Intel Foverors hingegen ist einen Schritt weiter: Dort können verschiedene CPU-Dies, ein I/O-Package und noch DRAM übereinander auf einem BGA-Package gestapelt werden.

Doch AMDs Aussage hinsichtlich einer Entwicklung in dem Bereich, heißt nicht, dass es auch zu einem Produkt in direkt dieser Form führt. Im Mai 2015 hatte AMD eine monströse HPC-APU angekündigt und schon detaillierte Pläne mit Stacked DRAM vorgelegt, davon war danach aber nie wieder etwas zu sehen.

Mai, Juni, Juli, August, ... – der Kalender ist voll

Fast täglich wird das Rad an der Termin-Front neu gedreht. Aufbauend auf den Gerüchten, dass Navi im Oktober kommen soll, resultiert Wccftech mit der Aussage, dass die GPU einen Monat nach den Prozessoren kommt, Ryzen 3000 würde im August erscheinen. So soll die Gamescom 2019 als Plattform für den Start dienen, sie beginnt am 21. August. Daraus wird dann am Ende kurioserweise aber Navi plötzlich im September, in den Überschriften sogar Mid Q3, was ja eigentlich August ist – Verständnis von Monaten und Quartalen vorausgesetzt. Klarheit bringt das am Ende letztlich gar nicht.

Nach Ende Mai/Anfang Juni zur Computex 2019 und dem 7.7. (einem Sonntag!), der von vielen Medien ungefragt als Starttermin genannt wurde, sind nunmehr alle Monate im Sommer 2019 abgedeckt worden. Denn AMD hatte erklärt, dass es zur Mitte des Jahres, im Sommer, soweit sein soll. Am Ende wird durch das Stochern im Nebel und dem Nennen einfach aller Monate jemand Recht haben. Gewusst hat es vorher aber keiner.

Ryzen soll schneller werden

Bereits zur ersten Vorstellung von AMD mit dem Acht-Kern-Prozessor hatte ComputerBase angemerkt, dass AMD den Takt und damit auch die Leistungsaufnahme exakt so gesetzt hat, dass der Konkurrent ganz knapp geschlagen wird. Anhand der 75 Watt Leistungsaufnahme spekulieren zehn Wochen später Medien noch einmal, dass 30 Watt bis 40 Watt zur TDP von 105 Watt oder auch 115 Watt fehlen und somit Luft für viel mehr Takt und „deutlich mehr“ Leistung sei. Doch dass eine CPU bei 100 Watt schneller ist als bei 75 Watt ist bisher auch schon immer so gewesen. Aktuell sind es bei 105 Watt zu 65 Watt TDP mit Ryzen 2700X zu Ryzen 2700 500 MHz Basistakt und 200 MHz im maximalen Turbo, im Schnitt 7 Prozent bis maximal 17 Prozent mehr Leistung, die durch 40 Prozent mehr TDP realisiert werden. Da sich die Physik nicht ändert, wird der Rahmen ähnlich ausfallen.

In den Fokus rückt AMD erwartungsgemäß auch den RAM, hier gab es viel Potenzial von der ersten Zen-Generation. Entwickler von Tools wurden demnach erste Einblicke gewährt, die von einem insgesamt aufgewerteten Speichercontroller sprechen. Doch auch diese Meldungen sind bisher noch unbestätigt und deshalb als Gerücht zu benennen.

- New memory controller with partial error correction for nonECC memory

- Desktop processor with two (2 CCD) chiplets on board, 32 threads maximum

- New MBIST (Memory built-in self-test)

- Core watchdog - is a fail/safe function used to reset a system in case the microprocessor gets lost due to address or data errors

- XFR - at the moment I do not see anything special about it, the algorithm and limits have been updated. Scalar Controll come back with new processors.

- Updated core control has a symmetric configuration of the active cores . In 2CCD configurations, each chiplet has its own RAM channel in order to minimize latency to memory access. 1 channel on 8 cores will be a bottleneck if you use the system in the default state.

UPD: point number 6 is questionable, perhaps there will be a special long-range interface for connecting a chiplet with IO