Interconnect Day: Intel will mit CXL auch PCI Express 6.0 voran bringen

Intel im Wandel: Nach einem guten Jahrzehnt PCI Express 3.0 und dem Fast-Verschlafen von PCIe 4.0 will Intel jetzt quasi direkt zu PCIe 5.0 gehen. Doch dem Hersteller ist das an Ausblick noch nicht genug: Erstmals schreibt Intel auch PCI Express in der sechsten Generation auf die Roadmaps.

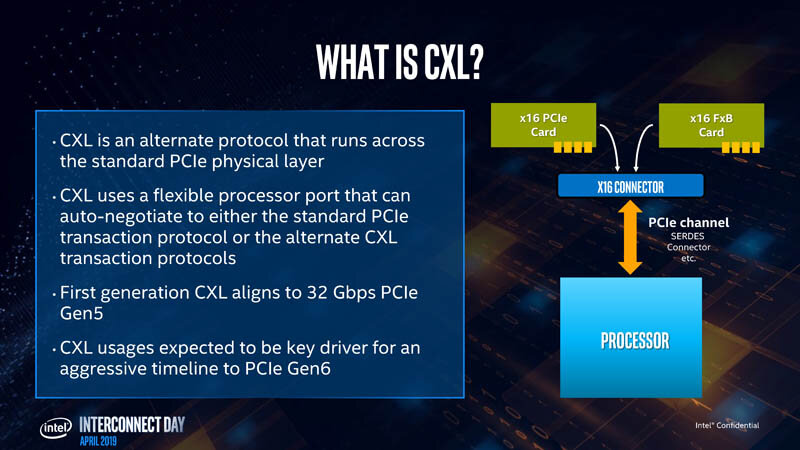

Wie unter anderem STH vom Intel Interconnect Day 2019 in Santa Clara berichtet, hat Intel die Pläne für CXL weiter ausgeführt. CXL alias Compute Express Link steht für die zukünftige Generation Interconnect bei Intel sowie Partnern, die auf PCIe 5.0 aufbauen wird. Doch Intel plant bereits darüber hinaus, erstmals wird PCI Express 6.0 auf einer Roadmap öffentlich benannt, wenn auch ohne festen Zeitraum und weitere Parameter. CXL könnte so PCIe quasi überholen oder PCIe könnte einige der mit CXL gewählten Parameter übernehmen. Intel würde dem Standard wie zuletzt bei USB 4.0/Thunderbolt dann seinen Stempel aufdrücken. Das ist allerdings noch ferne Zukunftsmusik, vor 2022 ist weder das eine noch das andere zu erwarten.

CXL soll bis dahin erst einmal einige Probleme lösen, die mit PCI Express in Form von mitunter großen Flaschenhälsen bestehen. Vor allem geht es dabei um Skalierbarkeit, was bereits im kleinen Server anfängt und in Rechenzentren und Supercomputern mit einer Mischung aus CPU, GPUs und Beschleunigern, die alle miteinander kommunizieren sollen, endet. Via PCI Express können kaum Ressourcen geteilt werden, wenn es geht, sind die Verluste deutlich und der Ansatz somit wenig effizient. Hinzu kommt eine am Ende sehr hohe Latenz.

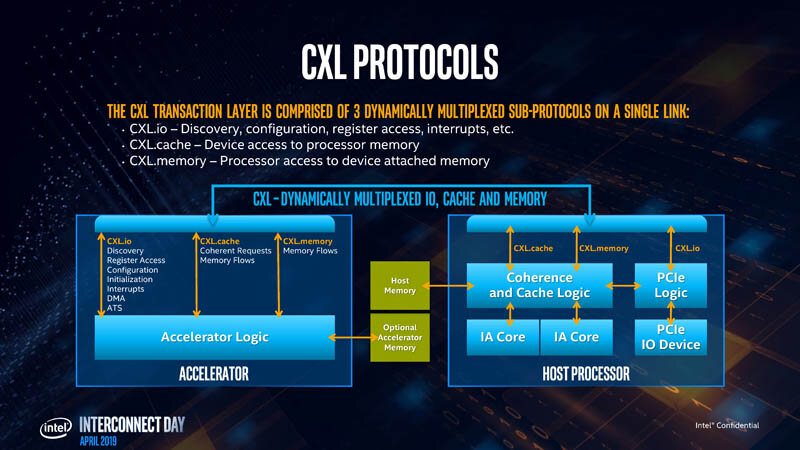

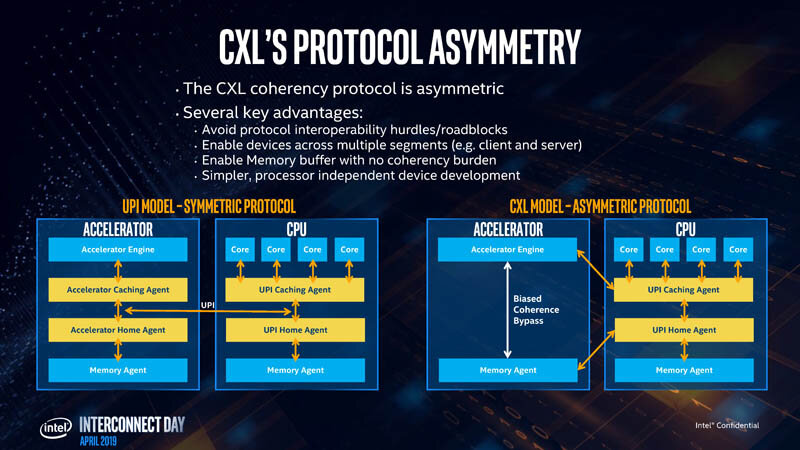

CXL will exakt diese Punkte angehen, ohne die Vorzüge von PCIe dabei komplett zu den Akten zu legen. Zu diesem Zweck bietet CXL unter anderem drei Sub-Protokolle, die sich um lokale Geräte, den Speicher und ferne Komponenten kümmern. An einem Beispiel zeigt Intel, wie die bisherige symmetrische UPI-Verbindung in Xeon-CPU und Beschleuniger-Karten, die ihren eigenen Home- und Caching-Agent nutzen, in Zukunft durch den asymmetrischen CXL ersetzt wird, bei dem alles die CPU übernimmt. Damit könnten auch 3rd-Party-Lösungen problemlos eingesetzt werden, selbst wenn sie intern mit einem anderen Interconnect wie beispielsweise CCIX oder NVLink arbeiten. CCIX ist CLX allerdings auch sehr ähnlich und wird bereits in ersten Produkten ausgeliefert – die beiden Protokolle konkurrieren letztlich, obwohl sie fast das gleiche bieten.

Die Zeit- und Produktfrage

Wann CXL erstmals genutzt wird, ist noch nicht genau bekannt, vor 2021 wird es jedoch nicht der Fall sein. Ohnehin ist auch nicht davon auszugehen, dass die Umstellung auf einen Schlag erfolgt, CPUs mit CXL sind noch lange nicht in Sicht. Vielmehr dürften erst kleine Teilbereiche damit adressiert und gewisse Produkte wie Intels FPGA Agilex damit ausgestattet werden. Und CXL 2.0 steht bereits auf den Roadmaps, die Entwicklung dafür soll noch in diesem Quartal beginnen, erklärt das Konsortium (PDF).

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!