3 nm Gate-All-Around: Samsungs neue Chips bieten massives Leistungsplus

Auf dem aktuellen Samsung Foundry Forum hat der Halbleiterbereich des Konzerns bekannt gegeben, die ersten Designrichtlinien für den vermutlich größten Fertigungsschritt seit vielen Jahren gelegt zu haben. Die Gate-All-Around-Technologie soll erstmals bei 3 nm zum Einsatz kommen, die ab dem Jahr 2021 erwartet wird.

Version 0.1A des Process Design Kits (PDK) ist nur der Grundstein für die Fertigungsstufe 3GAE, was für 3 nm Gate-All-Around Early steht und die erste Ausbaustufe markieren wird. Darauf folgen soll zügig 3GAP (Gate-All-Around Plus), als optimierte und verbesserte Version.

Gate-All-Around steht bei Samsung bereits seit Jahren auf der Roadmap, doch nun wird es ernst. Erste Leistungsangaben versprechen nun nicht nur eine 45 Prozent kleinere Fläche als bei der noch sehr jungen 7-nm-Fertigung, hinzu kommen sollen auch noch eine 50 Prozent geringere Leistungsaufnahme und 35 Prozent gesteigerte Leistung. In der Regel sind derartige Kombinationen aber nie gleichzeitig anzutreffen, oft ist entweder von mehr Leistung oder weniger Verbrauch die Rede. Sollte dies am Ende Wirklichkeit werden, wäre der neue Prozess wirklich ein Meilenstein.

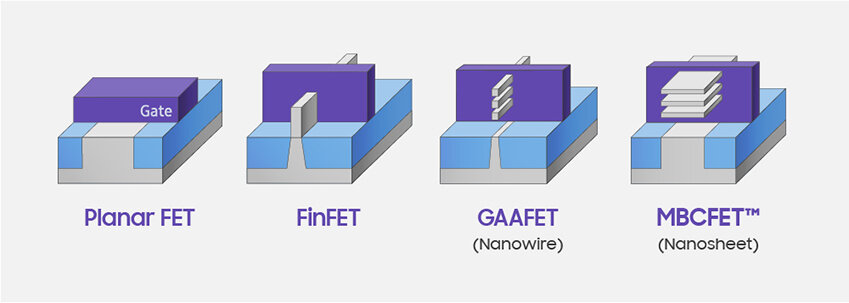

Gate-All-Around ist in der Basis dem heute gängigen FinFET sehr ähnlich, aber anstatt „nur“ von drei Seiten, soll – wie der Name schon vermuten lässt – das Gate-All-Around die Nanowires komplett umschließen und so den quasi „perfekten Transistor“ ermöglichen. Samsung nennt einen Teil der Technik auch MBCFET (Multi Bridge Channel FET).

Sollte sich der Zeitplan für das Jahr 2021 als korrekt herausstellen, wird Samsung mit 3GAE unter anderem gegen Intels bis dahin anvisierten 7-nm-Prozess antreten, von TSMC ist mindestens ein 5-nm-Prozess zu erwarten. Zuletzt lag TSMC aber stets leicht in Führung bei neuen Technologien, hier bleibt abzuwarten, was die Taiwaner noch ankündigen werden. Ob dabei auch GAA genutzt wird, ist noch nicht bekannt. Nach bisherigem Wissensstand ist Samsung hier führend.