3D-NAND: Mit Vollgas Richtung 128 Layer für mehr Profit

Mit Flash-Speicher lässt sich momentan kaum Geld verdienen, denn der Speicher ist aufgrund der Überversorgung so günstig wie nie. Was Kunden freut, sehen die Speicherhersteller anders. Die kommende 3D-NAND-Generation mit 120 respektive 128 Zellschichten (Layer) soll wieder für Profitabilität sorgen.

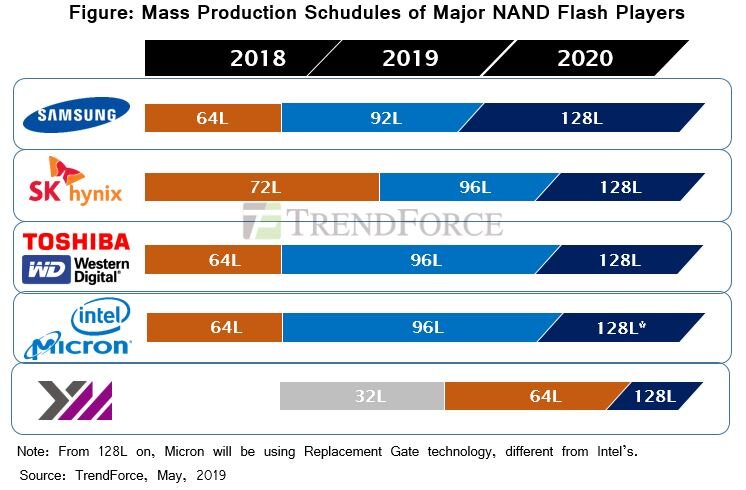

Unter Berufung auf Quellen aus der Branche berichtet DigiTimes, dass die NAND-Hersteller alles daran setzen, um die 120/128-Layer-Generation so schnell wie möglich auf den Markt zu bringen. Einige der führenden Hersteller sollen schon Samples ihrer 128-Layer-Chips ausgeliefert haben und peilen den Start der Massenproduktion für das erste Halbjahr 2020 an. Von einer beschleunigten Entwicklung kann aber eigentlich keine Rede sein, denn Branchenexperten haben schon letztes Jahr den Start der 120/128-Layer-Fertigung für Ende 2019 oder Anfang 2020 prognostiziert und sahen dabei zeitlich Samsung vor Toshiba/Western Digital und Intel/Micron sowie SK Hynix.

YMTC als aufstrebender Speicherriese aus China könnte nach mancher Einschätzung ebenfalls schon ab 2020 128-Layer-NAND fertigen. So sieht dies auch die jüngste Roadmap von TrendForce:

Weniger Kosten pro Bit für mehr Profit

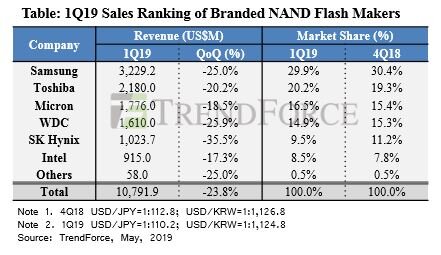

Von der neuen NAND-Generation erhoffen sich die Hersteller einmal mehr niedrigere Herstellungskosten pro Bit, was den derzeit sehr niedrigen Preisen für NAND-Flash entgegenkommt und somit wieder für mehr Profit sorgt. Laut dem Bericht aus Taiwan habe Marktführer Samsung inzwischen fast den „break-even point“ erreicht, bei dem die Einnahmen nur noch die Selbstkosten decken, aber keinen Gewinn mehr bringen.

Gegen Ende des Jahres 2018 haben die NAND-Hersteller zum Teil ihre Produktion heruntergefahren, um der Überversorgung und damit dem Preisverfall Einhalt zu gebieten. Diese Maßnahmen haben aber bisher kaum Früchte getragen und jüngsten Prognosen von Marktforschern sehen weiter sinkende Preise voraus. Die Überversorgung betrifft vor allem die schon etwas ältere 64-Layer-Generation, deren Herstellungsverfahren weit gereift und entsprechend ertragreich sind. Die Chip-Ausbeute bei der jüngeren 90/96-Layer-Generation sei dagegen noch „instabil“, was bei der weiteren Preisentwicklung in diesem Jahr dann doch noch für „mehr Variablen“ sorgen könnte.

Technischer Ausblick auf die 120/128-Layer-Generation

Einen Ausblick auf die kommenden 3D-NAND-Chips lieferten Samsung und Toshiba auf der diesjährigen ISSCC. Der BiCS5-NAND von Toshiba und Western Digital soll die bis dato höchste Speicherdichte für TLC-3D-NAND mit drei Bit pro Speicherzelle liefern. Die Speicherdichte ist ein wesentlicher aber nicht der einzige Faktor bei den Herstellungskosten.

| Samsung V-NAND V6 | Toshiba/WD BiCS5 | |

|---|---|---|

| Chip | 512 Gbit TLC (4 Planes) | |

| Layer | 110~120 | 128 |

| Die | 101,58 mm² | 66 mm² |

| Dichte | 5,0 Gb/mm² | 7,8 Gb/mm² |

| Read (tR) | 45 µs | 56 µs |

| Program | 82 MB/s | 132 MB/s |

| I/O | 1,2 Gb/s | 1,066 Gb/s |

| Power | Vcc: 2,35 V bis 3,6 V Vccq: 1,2 V |

Vcc: 2,3 V bis 3,6 V Vccq: 1,2 V, 1,8 V |

Samsungs V-NAND V6 liegt in der TLC-Version mit 512 Gbit bei der Speicherdichte weit zurück. Der Hersteller spricht bisher von 110 Layern bis 120 Layern, gibt sich allerdings in letzter Zeit ohnehin sehr bedeckt, was kommende Speichergenerationen angeht und hat letztes Jahr weder am Flash Memory Summit teilgenommen, noch wie sonst ein eigenes Flash-Event ausgerichtet.

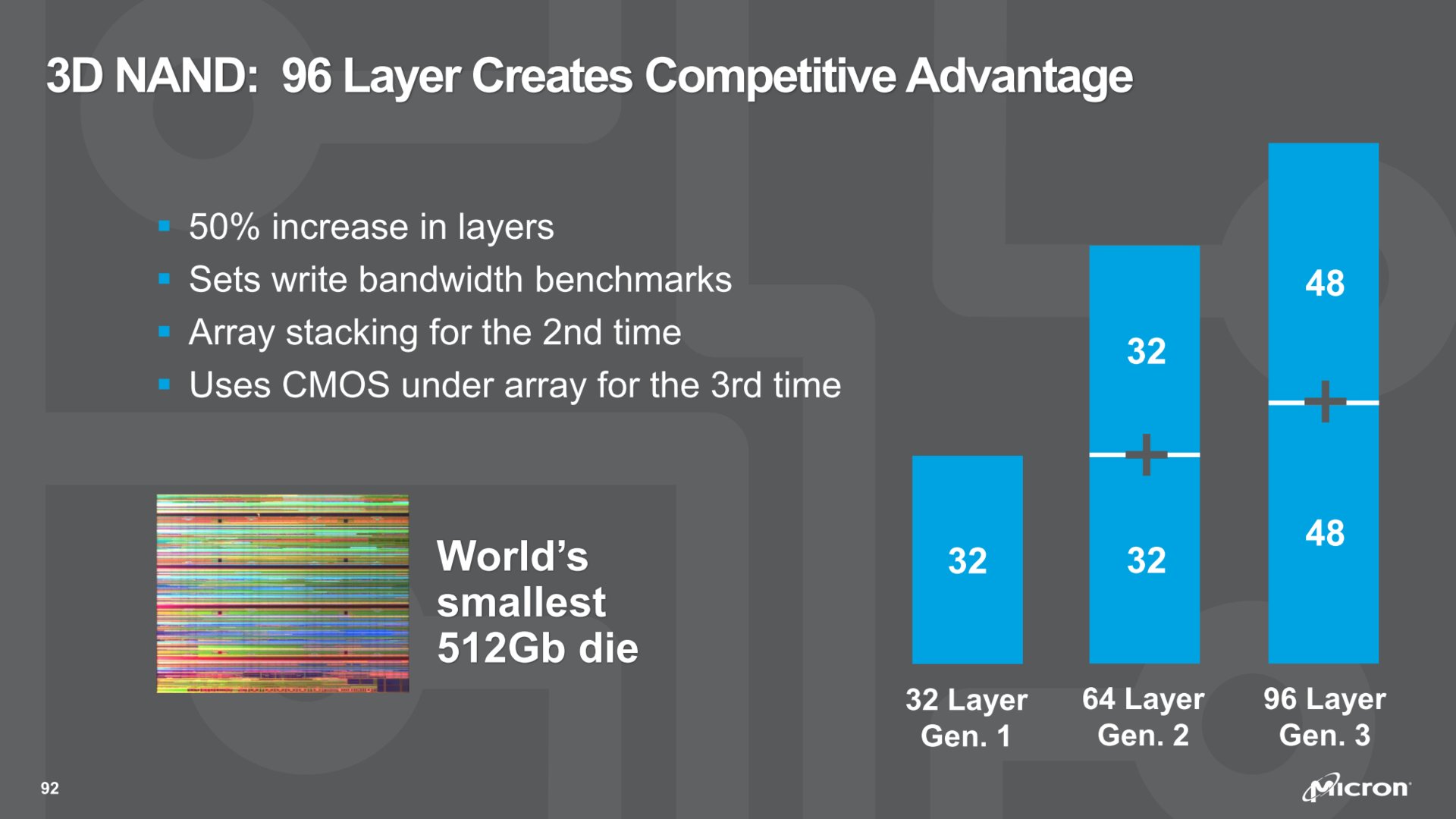

Die Gigabit pro Quadratmillimeter bestimmen aber nicht allein die Herstellungskosten. Toshiba und Western Digital wie auch Intel und Micron setzen bereits bei 96-Layern auf das sogenannte String Stacking (auch „Array Stacking“): Dabei werden im Prinzip zwei 48-Layer-Speicher gefertigt und anschließend übereinander gestapelt. Während dies die Entwicklungszeit beschleunigt, sind die Herstellungskosten pro Chip höher als bei einem nativen (monolithischen) Chip, wie ihn Samsung sowohl mit 96 Layern als auch mit ~120 Layern produziert.

| Hersteller | Generation | Layer | Bit/Zelle | Kapazität/Die | Die-Fläche | Dichte |

|---|---|---|---|---|---|---|

| Toshiba/WD | BiCS3 | 64 | 3 (TLC) 4 (QLC) |

512 Gbit 768 Gbit |

132 mm² ? |

3,9 Gbit/mm² ? |

| BiCS4 | 96 | 3 (TLC) 4 (QLC) |

512 Gbit 1,33 Tbit |

86,1 mm² 158,4 mm² |

5,9 Gbit/mm² 8,5 Gbit/mm² |

|

| BiCS5 | 128 | 3 (TLC) 4 (QLC) |

512 Gbit ? |

66 mm ² ? |

7,8 Gbit/mm² ? |

|

| Samsung | V-NAND V4 | 64 | 3 (TLC) 4 (QLC) |

512 Gbit 1 Tbit |

128,5 mm² 181,9 mm² |

4,0 Gbit/mm² 5,6 Gbit/mm² |

| V-NAND V5 | 96 | 3 (TLC) 4 (QLC) |

256 Gbit bis 1 Tbit |

? | ? | |

| V-NAND V6 | 110+ | 3 (TLC) | 512 Gbit | 101,58 mm² | 5,0 Gbit/mm² | |

| Intel/Micron | Gen 2 | 64 | 3 (TLC) 4 (QLC) |

256/512 Gbit 1 Tbit |

59 mm² (256 Gbit) ? |

4,3 Gbit/mm² (256 Gbit) ? |

| Gen 3 | 96 | 3 (TLC) 4 (QLC) |

512 Gbit ? |

? | ? | |

| SK Hynix | 3D V4 | 72 | 3 (TLC) | 256/512 Gbit | ? | ? |

| 3D V5 („4D“) | 96 | 3 (TLC) 4 (QLC) |

512 Gbit/1 Tbit 1 Tbit |

? | ? | |

| YMTC | Gen 1 | 32 | ? | ? | ? | ? |

| Gen 2 | 64 | 3 (TLC) | 256 Gbit | ? | ? |