Co-EMIB, Foveros und ODI: Intel spricht über neue Packaging-Technologien

Intel hat auf der SemiCon West 2019 über neue Packaging-Technologien gesprochen. Auf Basis von EMIB und Foveros will Intel mit Co-EMIB sehr komplexere Designs mit bis zu 36 Chiplets realisieren können. Darüber hinaus würde Co-EMIB das Chipdesign mit mehreren Layern aber auch flexibler machen.

Intel will unterschiedliche Chips zukünftig stapeln

Bereits Ende 2018 hat Intel angekündigt, den EMIB-Ansatz stärker verfolgen zu wollen und verschiedene Chips ab 2019 auf einem Package zu stapeln. Durch das sogenannte 3D-Stacking von Chips mit unterschiedlichen Funktionen sollen ganz neue Produkte möglich sein.

EMIB bleibt eine kostengünstige Alternative

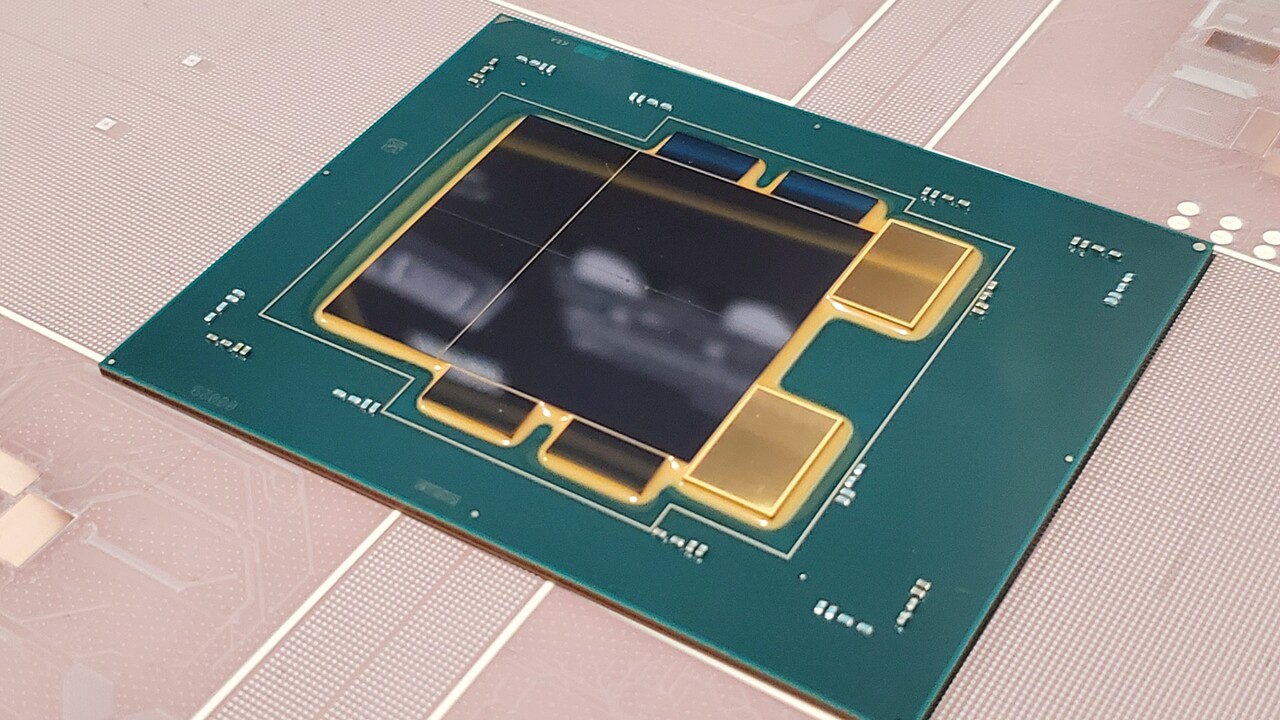

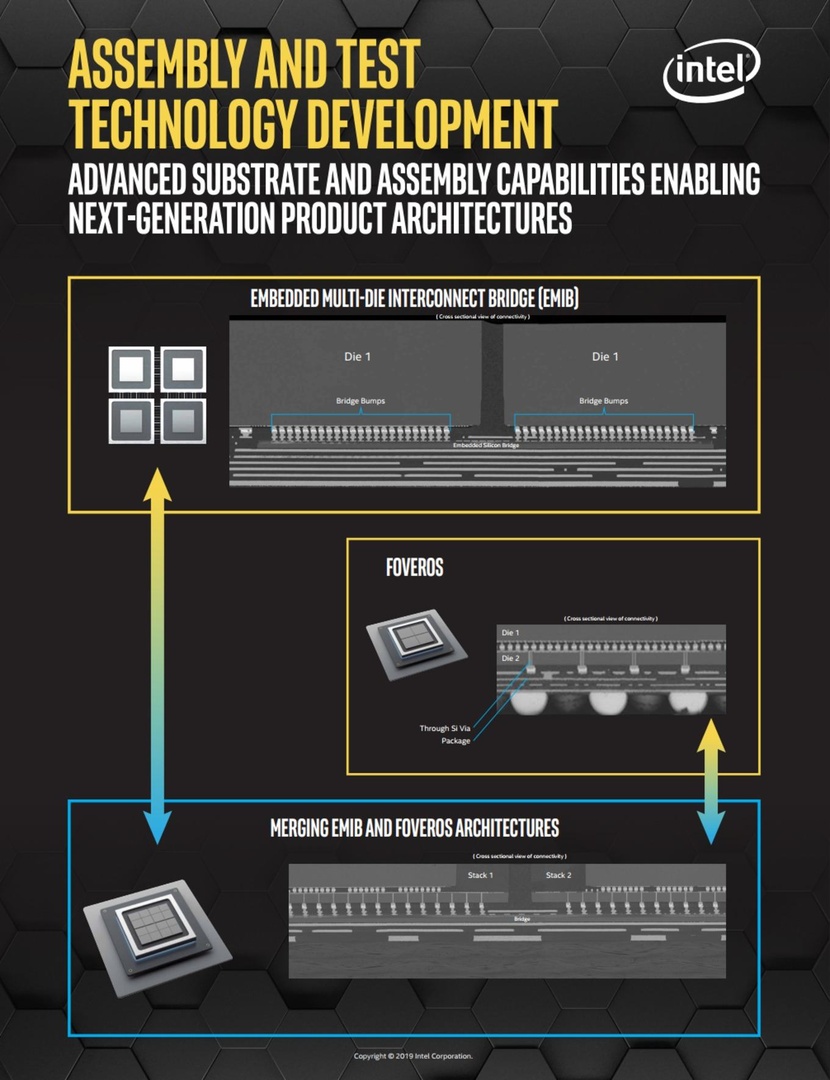

Intel nutzt EMIB (Embedded Multi-Die Interconnect Bridge) seit 2017 als kostengünstige Alternative zu Interposern und plant, diese Packaging-Technologie auch auf seine Mainstream-Chips zu übertragen. EMIB ist eine Siliziumbrücke, die eine Hochgeschwindigkeitsverbindung zwischen zwei benachbarten Chips ermöglicht.

Der große Vorteil einer solchen Siliziumbrücke gegenüber Interposern ist vor allem die kostengünstige Realisierung. Während ein Interposer eine Größe von 800 mm² und mehr haben kann, handelt es sich beim EMIB-Ansatz um ein winziges Stück Silizium. Derzeit verwendet Intel diese Technologie für Stratix-FPGAs, Agilex-FPGAs und Kaby Lake-G.

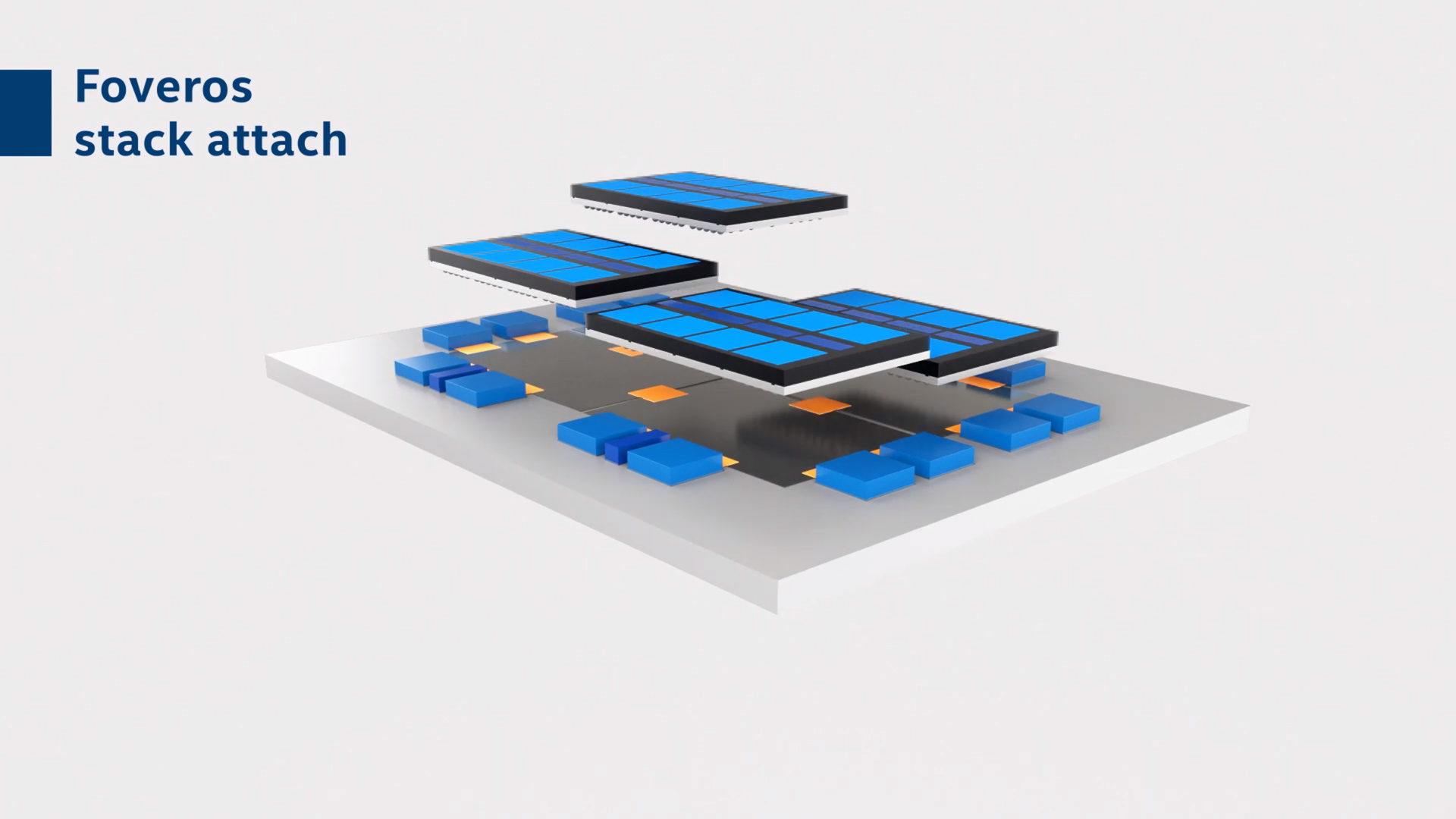

Foveros für Siliziumschichten in 3D

Auf einem Architecture Day im vergangenen Jahr beschrieb Intel die kommende 3D-Foveros-Technologie, die erstmalig in Lakefield zum Einsatz kommen wird, im Detail. Hierbei handelt es sich um einen aktiven Interposer, der Through-Silicon-Vias (TSVs) verwendet, um mehrere Siliziumschichten übereinander zu stapeln.

In Lakefield wird die Foveros-Technologie verwendet, um den 22-nm-Basis-Die (der die Stromversorgung und die PCH-Funktionalität bereitstellt) mit dem 10-nm-Computing-Die aus vier Tremont- und einem Sunny Cove-Kern zu verbinden.

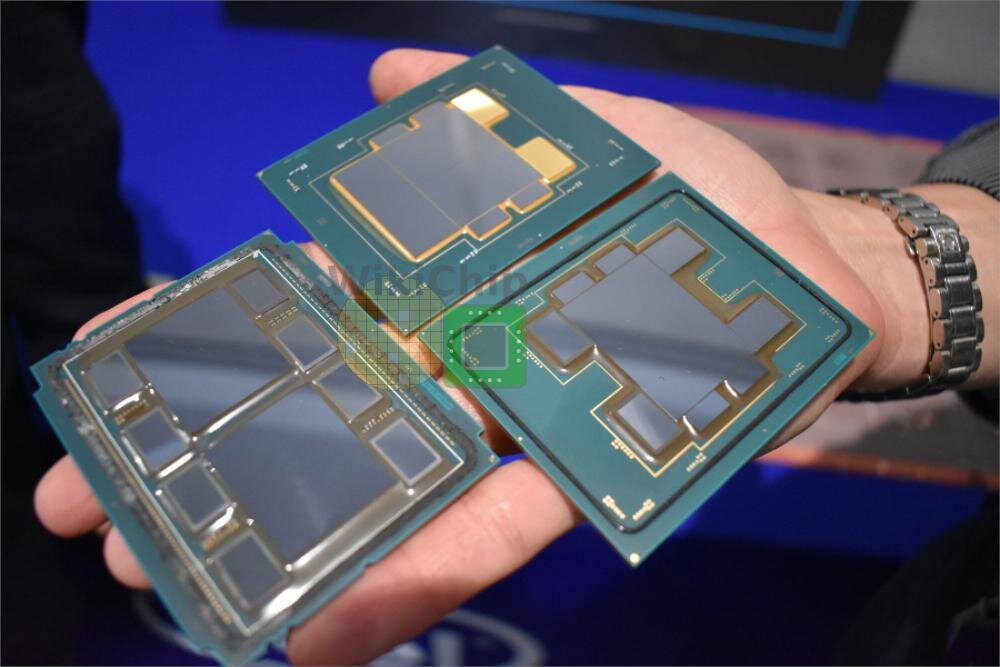

Im Mai dieses Jahres testete Intel erstmalig einen neuen Ansatz, bei dem sowohl EMIB als auch Foveros zusammen verwendet wurden, um bis zu 36 Chiplet auf nur einem Package zu realisieren. Die neue Packaging-Technologie trägt den Namen Co-EMIB und soll die Vorteile von 2D- und 3D-Packaging vereinen.

Co-EMIB verbindet EMIB und Foveros

Co-EMIB nutz einen EMIB-Part, auf dem dann die einzelnen Dies sitzen. Diese neue Packaging-Technologie soll es Intel ermöglichen, mehrere 3D-gestapelte Foveros-Chips miteinander zu verbinden, um noch größere und flexiblere Packages zu erstellen.

Intel zeigte bereits ein Konzeptprodukt aus vier Foveros-Stapeln. Jeder Foveros-Stapel bestand dabei aus acht Small-Compute-Chips, die über eine Silizium-Durchkontaktierung, das sogenannte Through-Silicon-Vias (TSVs), mit dem Basis-Die verbunden sind. Foveros verbindet die einzelnen Chips so miteinander, als würde es sich dabei um einen großen monolithischen Chip handeln.

Jeder der vier Foveros-Stapel ist wiederum zweimal über Co-EMIB mit seinen zwei benachbarten Stacks verbunden. Co-EMIB wird ferner verwendet, um den HBM und die Transceiver mit den Rechenstapeln zu verbinden.

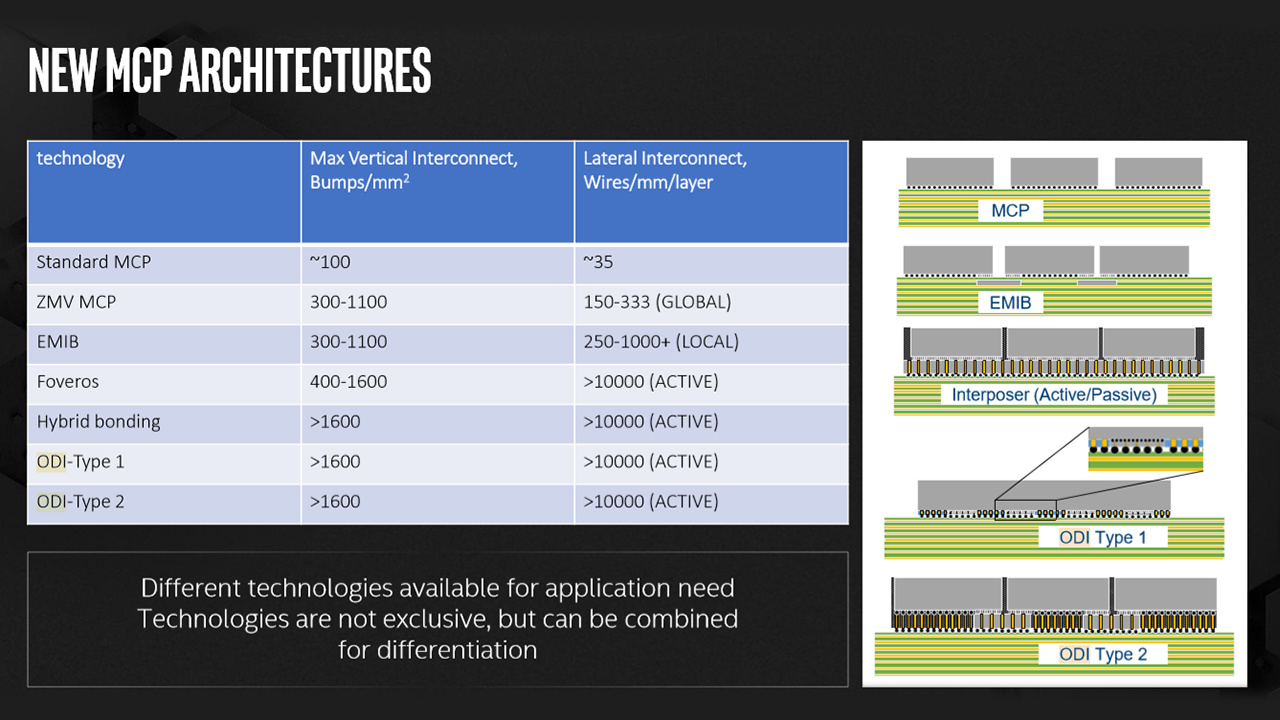

Mehr Bandbreite und geringere Latenzen durch ODI und MDIO

Omni-Directional Interconnect (ODI) ist eine neue Art von Multi-Chip-Verbindung neben dem Standard-MCP, EMIB und Foveros. ODI ermöglicht sowohl eine horizontale als auch eine vertikale Übertragung und eine höhere Bandbreite als die bisherigen Through-Silicon-Vias (TSVs). Zudem besitzt ODI geringere Widerstände und niedrigere Latenzen und benötigt weniger vertikale Kanäle im Basis-Die. Der neue Interconnect minimiert die Chipfläche und gibt Platz für aktive Transistoren frei.

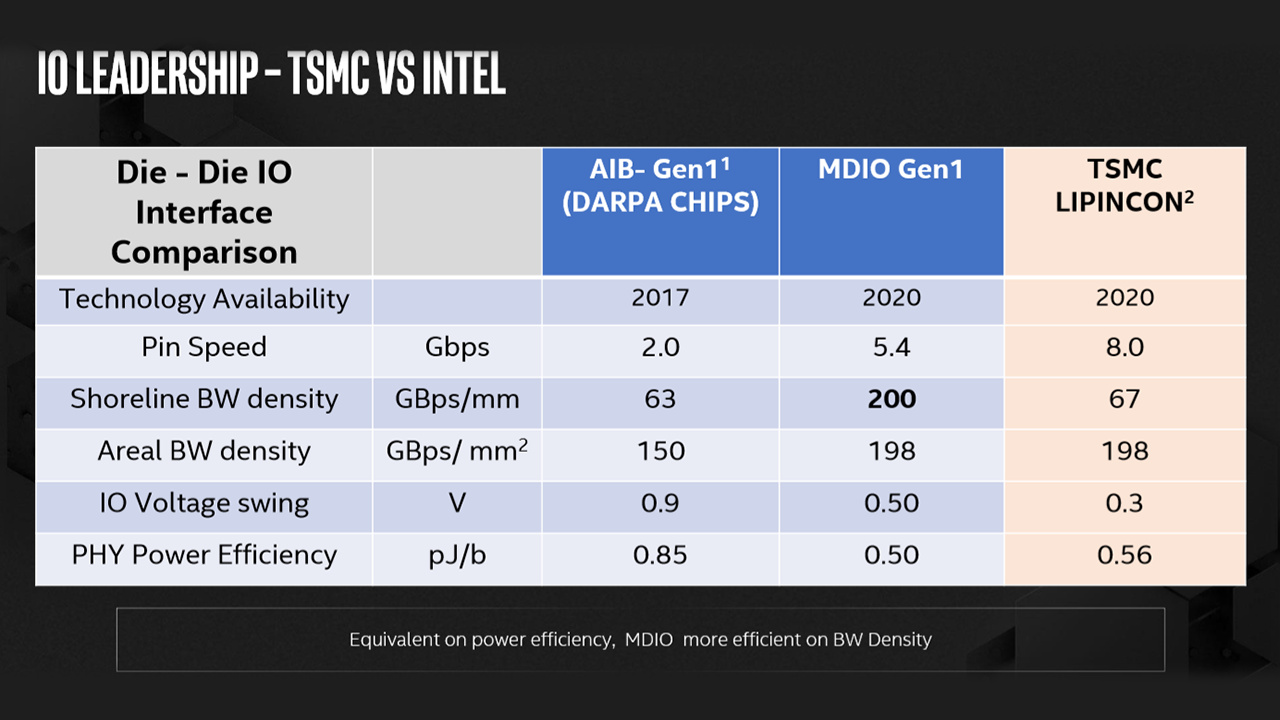

Multi-Die I/O (MDIO) ist eine Weiterentwicklung des Advanced Interconnect Bus (AIB), der eine standardisierte Schnittstelle auf SiP-PHY-Ebene für EMIB und die Kommunikation von Chip zu Chip bereitstellte. MDIO soll dank einer geringeren I/O-Spannung (0,5 Volt) effizienter sein als AIB (0,9 Volt) und die Bandbreite von 2 Gbit/s auf 5,4 Gbit/s anheben. Intel vergleicht MDIO mit dem kürzlich vorgestellten LIPINCON von TSMC.