Flash Memory Summit: Über PLC-NAND mit 5 Bit und halbierte Speicherzellen

Um die Speicherdichte von NAND-Flash weiter zu steigern sollen künftig noch mehr Bit pro Speicherzelle untergebracht werden. Nach SLC mit 1 Bit, MLC mit 2 Bit, TLC mit 3 Bit und QLC mit 4 Bit folgt PLC (Penta-Level Cell) mit 5 Bit pro Zelle. Außerdem sollen Zellen „halbiert“ und damit deren Speicherdichte erhöht werden.

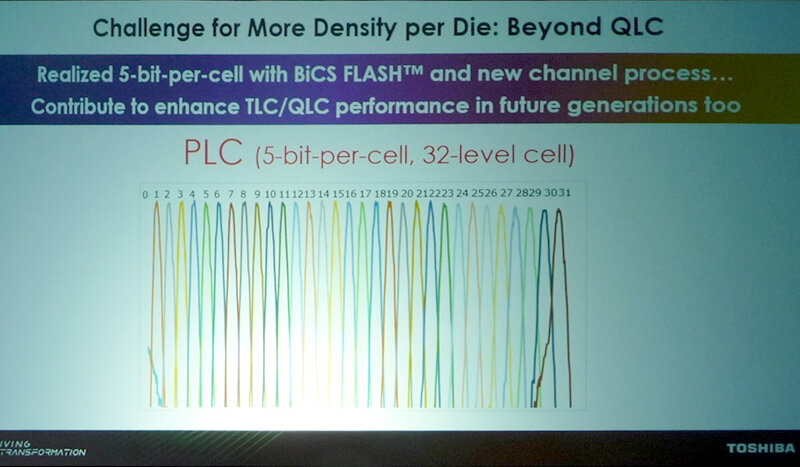

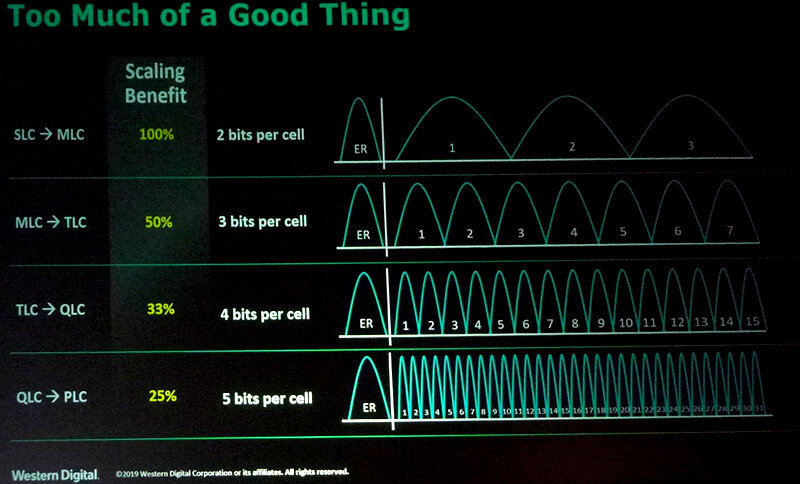

Der Schritt zu PLC mit 5 Bit bedeutet eine Steigerung der Speicherkapazität pro Zelle gegenüber QLC-NAND um weitere 25 Prozent. Allerdings werden dafür nun nicht nur 16, sondern gleich 32 verschiedene Spannungslevel nötig, um 5 Bit abzubilden. Der Speichervorgang ist damit noch weitaus komplexer und fehleranfälliger als bei QLC-NAND. Je mehr Spannungslevel unterschieden werden müssen, desto mehr haben Controller respektive die Engines zur Fehlerkorrektur zu tun.

Dennoch haben NAND-Hersteller Penta-Level Cell, kurz PLC, mit 5 Bit auf dem Zettel, wie Präsentationen auf dem Flash Memory Summit 2019 darlegen. Eine Folie von Western Digital ist allerdings mit „Zu viel des Guten“ betitelt, was zeigt, dass die Umsetzung weder einfach, noch gesichert ist.

Noch weniger Schreibzyklen als mit QLC

Tendenziell nimmt nicht nur die Schreibleistung mit jedem weiteren Bit pro Zelle ab, sondern auch die anhand der möglichen Schreibzyklen gemessene Haltbarkeit des Speichers. QLC-NAND werden noch etwa 1.000 Schreibzyklen nachgesagt, während TLC-NAND immerhin bis zu 3.000 Zyklen überstehen soll. Seltener werdender 2-Bit-MLC-Flash wird noch mit Werten im fünfstelligen Bereich angegeben und der vor allem aus Kostengründen nur noch in Nischenprodukten eingesetzte SLC-Flash wurde sogar mit 100.000 oder mehr Zyklen beworben.

Schon QLC-NAND ist mit seiner begrenzten Haltbarkeit vor allem für Einsatzgebiete mit geringem Schreibaufkommen beispielsweise in Mainstream-SSDs für Verbraucher oder als sogenannter Write-Once-Read-Many-Speicher (WORM) im Server-Bereich vorgesehen. Mit vier Bit pro Speicherzelle sinkt auch die Schreibgeschwindigkeit der Chips. Dies wird zwar meist durch einen Pseudo-SLC-Cache kaschiert, bei dem ein Teil des SSD-Speichers im SLC-Modus mit nur einem Bit beschrieben wird. Doch ist dieser Zwischenspeicher erschöpft, sinkt die Schreibrate oft unter HDD-Niveau. Samsungs 860 QVO zum Beispiel schreibt dann nicht mehr mit 520 MB/s, sondern nur noch mit 80 MB/s bis 160 MB/s je nach Modell.

Welche Haltbarkeit PLC-NAND erreichen wird, bleibt abzuwarten. Die Prognosen von Autor Chris Mellor mit gegenüber QLC-NAND halbierter Haltbarkeit sind als schlichtweg geraten einzustufen. Denn belastbare Informationen liegen hierzu noch nicht vor.

Halbierte Zellen für mehr Speicherdichte

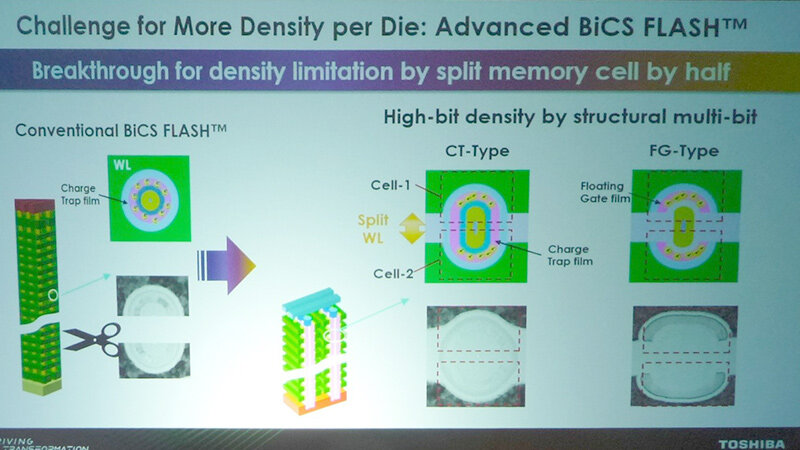

Über einen weiteren von Toshiba Memory verfolgten Ansatz zur Erhöhung der Speicherdichte berichtet die japanische Website PC Watch. Demnach hat der Hersteller auf dem Flash Memory Summit ein Konzept vorgestellt, bei dem die sogenannte Word Line einer Speicherzelle halbiert wird. Vereinfacht spricht Toshiba vom Halbieren einer Speicherzelle, allerdings ist unklar, was mit der Bit Line passiert.

Laut dem Bericht soll dadurch die Speicherdichte „effektiv verdoppelt“ werden. Das Konzept sei sowohl für nach dem Charge-Trap-Flash-Prinzip arbeitende Zellen wie auch bei der Floating-Gate-Technik denkbar. Allerdings gilt es als schwierig umzusetzen in der Fertigung. Ob die theoretisch denkbare Verdoppelung der Speicherdichte in der Praxis möglich wird, bleibt ebenso fraglich.

Vor diesem Hintergrund wirkt das zunächst absurd anmutende Gerücht um Octa-Level Cell NAND (OLC) aus dem Februar gar nicht mehr ganz so abwegig. Wccftech wollte aus mehreren Quellen erfahren haben, dass Micron schon bald mit OLC-NAND plant. Allerdings hatte Micron den Inhalt des Berichts als „erfunden“ bezeichnet und somit dementiert. Zumindest der seinerzeit auf das erste oder zweite Quartal 2019 datierte Termin zur Einführung von OLC, ist ohnehin längst hinfällig.