Kioxia Twin BiCS Flash: Neues Speicherzellendesign für PLC mit 5 Bit

Kioxia (vormals Toshiba Memory) hat eine neue Technik zur Erhöhung der Speicherdichte von Flash-Speicher entwickelt. Die „Twin BiCS Flash“ genannte Speicherzellenstruktur soll 3D-NAND mit kleineren Zellen und potenziell mehr Bit pro Zelle ermöglichen. Die Technik sei ein Kandidat für mehr als vier Bit (QLC).

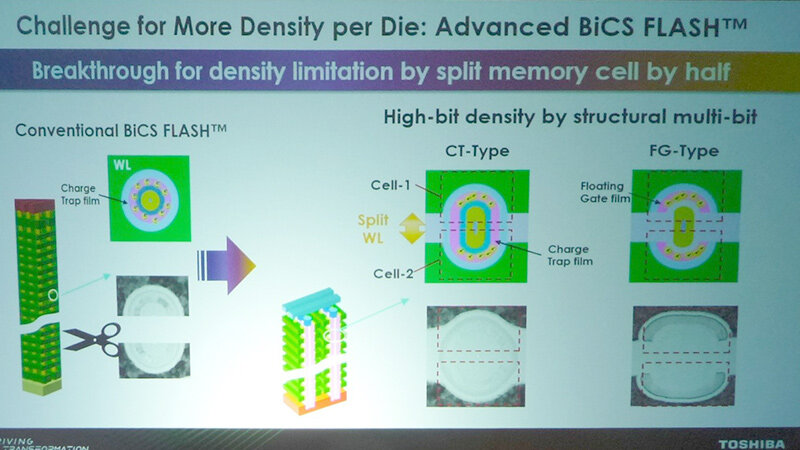

Die Ankündigung von Kioxia kam nicht überraschend, denn bereits auf dem Flash Memory Summit 2019 hatte das Unternehmen, das seinerzeit noch unter dem Namen Toshiba Memory firmierte, bereits das Grundprinzip der „halbierten Speicherzelle“ vorgestellt.

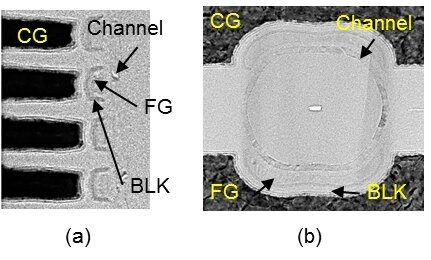

Am Donnerstag ließ Kioxia nun die Entwicklung der weltweit ersten „three-dimensional (3D) semicircular split-gate flash memory cell structure“ verlauten, die das Unternehmen „Twin BiCS FLASH“ taufte; unter dem Namen „BiCS Flash“ läuft der 3D-NAND, den Kioxia gemeinsam mit Partner Western Digital entwickelt und produziert.

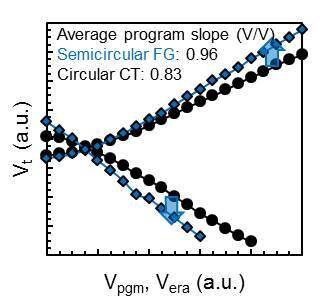

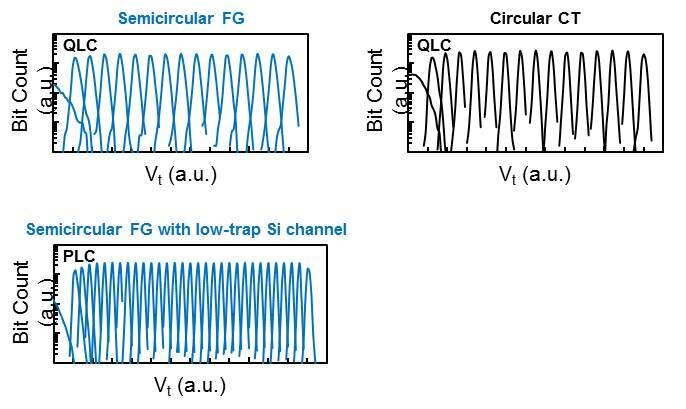

Im Vergleich zum bisherigen BiCS-Flash mit kreisförmigen Charge-Trap-Zellen (CT) nutzt Kioxia nun halbkreisförmige Floating-Gate-Zellen (FG). Die neue Struktur soll das Fenster zur Programmierung der Zelle vergrößern, obgleich die Zellen sogar kleiner als bei den bisherigen CT-Zellen ausfallen. Damit sei die Technik „ein vielversprechender Anwärter“, um vier Bits pro Zelle (QLC) noch zu übertreffen. Auf dem Flash Memory Summit wurde passend dazu bereits über Penta-Level-Cell-NAND (PLC) mit fünf Bit pro Zelle philosophiert.

Mehr kleinere Zellen und/oder mehr Bit pro Zelle sind Ansätze, um die Speicherdichte von 3D-NAND weiter zu erhöhen, ohne noch mehr Zellschichten (Layer) übereinander zu stapeln. Inzwischen hat 3D-NAND 128 Layer erreicht und zumindest in der Theorie denken Hersteller bereits an über 500 oder sogar 800 Layer mit kommenden Generationen. Doch irgendwann ist das Limit erreicht, denn jede Schicht bedeutet auch einen zusätzlichen mit Kosten verbundenen Arbeitsschritt, weswegen Hersteller wie Kioxia nach anderen Möglichkeiten forschen.

3D flash memory technology has achieved high bit density with low cost per bit by increasing the number of cell stacked layers as well as by implementing multilayer stack deposition and high aspect ratio etching. In recent years, as the number of cell layers exceeds 100, managing the trade-offs among etch profile control, size uniformity and productivity is becoming increasingly challenging. To overcome this problem, Kioxia developed a new semicircular cell design by splitting the gate electrode in the conventional circular cell to reduce cell size compared to the conventional circular cell, enabling higher-density memory at a lower number of cell layers.

Kioxia

Vorerst nur Potenzial für die (ferne) Zukunft

Doch zunächst ist die neue Zellstruktur nur besagter „vielversprechender Anwärter“ unter den Techniken zur weiteren Steigerung der Datendichte von NAND-Flash. Wann und ob überhaupt das neuartige Zellendesign in einer kommenden Generation BiCS-Flash eingesetzt wird, bleibt abzuwarten. Kioxia will zumindest auf diesem Gebiet weiter forschen und ist noch „auf der Suche nach praktischen Anwendungen“.

Bis dahin wird im nächsten Jahr zunächst der Wechsel von BiCS4 mit 96 Layer auf BiCS5 mit 128 Layer erwartet. SK Hynix (128 Layer „4D-NAND“) und Samsung (V-NAND v6) sind bereits bei mehr als 100 Zellschichten angekommen.