Fertigungsverfahren: 5-nm-Prozess von TSMC skaliert zu 184 Prozent

In beeindruckender Weise hat TSMC in den letzten Jahren die gesteckten Ziele beim Fortschritt der Fertigungstechnologie umgesetzt. Die in Kürze in Massenproduktion startende 5-nm-Fertigung (N5) ist nur der letzte Meilenstein, der gegenüber der aktuellen 7-nm-Fertigung eine Skalierung um den Faktor 1,84 erreicht.

Deutlich mehr Schaltungen pro mm²

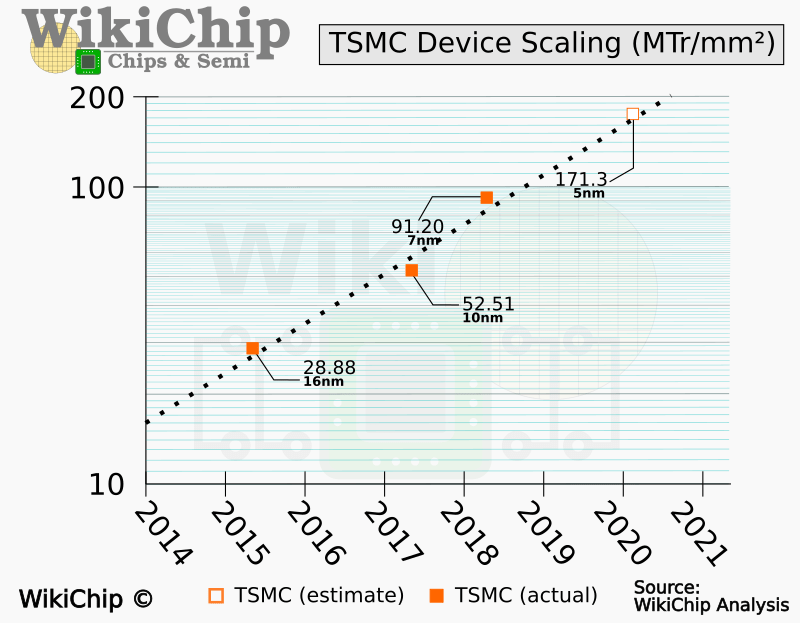

Er bezieht sich auf die Dichte der Transistoren, die pro Quadratmillimeter zu finden sind. Die 5-nm-Fertigung sorgt laut TSMC nun dafür, dass 84 Prozent mehr Transistoren in der gleichen Fläche ihren Platz finden als in der aktuellen 7-nm-Fertigung. In nackten Zahlen ausgedrückt errechnet WikiChip 171,3 MTr/mm² für die 5-nm-Fertigung, bei 7 nm waren es 91,2 MTr/mm² (MTr = Millionen Transistoren). Auch der Vergleich zu den vorangegangen Prozessen ist interessant, da er verdeutlicht, wie die Entwicklung in dem Bereich nach wie vor sehr rasch vonstatten geht: Vor knapp fünf Jahren zur Einführung des 16-nm-Prozesses lag der Wert noch bei 28,88 MTr/mm².

Überhaupt verdeutlicht die Grafik die imposante Umsetzung neuer Technologien bei TSMC in den letzten fünf Jahren. Aus Problemen mit den vorangegangenen Fertigungsstufen gelernt, wird inzwischen jeder neue Schritt umgesetzt wie ein Uhrwerk. Dabei werden sogar Vorgängervarianten noch übertroffen. So beispielsweise beim 7-nm-Prozess, der laut Hersteller der am schnellsten hochgefahrene Prozess ist und dazu auch noch die schnellste Reduzierung von Fehlern in Chips aufweisen konnte. Daraus ergeben sich sehr schnell eine hohe Ausbeute (Yield) und entsprechend viele funktionsfähige Chips.

Mit N5 alleiniger Marktführer

Der Produktionsschritt N5 soll genau dort weiter machen. Hier erwartet TSMC sogar ein noch besseres Verhältnis, was das Unternehmen klar zum Marktführer machen würde. Samsungs 5-nm-Lösung ist nur eine minimal optimierte 7-nm-Lösung und kein Konkurrent. Der könnte am Ende nach aktuellem Stand nur Intels Produkt in Form eines 7-nm-Chips sein, der jedoch nicht vor Ende des nächsten Jahres erwartet wird. TSMC hat mindestens 1,5 Jahre Vorsprung.

Bei den neuen Chips werden über zehn Lagen mit EUV belichtet. Es ist der erste direkt auf die EUV-Lithografie ausgelegte Prozess, N7 und N7P waren klassische Produktionslinien mit Immersionslithografie (DUV), N7+ ein Ableger davon, bei dem einige Lagen mit EUV, alle anderen klassisch mit DUV belichtet wurden. Das erlaubt unterm Strich eine geringere Anzahl an Produktionsschritten, die bei N5 auf dem Niveau der 10-nm-Fertigung liegt. Ohne den Einsatz von EUV wären es rund 30 Prozent mehr. Allmählich rechnet sich der erhoffte Vorteil von EUV. Details zu dem Thema liefert der ComputerBase-Bericht „Was steckt hinter der EUV-Lithografie?“

In der neuen Fab 18, deren Baubeginn erst vor zwei Jahren erfolgte, sollen die 5-nm-Chips in Serie produziert werden. Die neue Fabrik wurde explizit für die Nutzung von EUV-Scannern ausgelegt und soll neben der 5-nm-Fertigung auch den nächsten Schritt, die 3-nm-Fertigung, bieten können. Dafür wird sie in zwei weiteren Bauphasen erweitert und soll Ende 2021 mit 4.000 Mitarbeiter eine Million 300-mm-Wafer pro Jahr fertigen.