3D-NAND: Micron stapelt erstmals 176 Layer übereinander

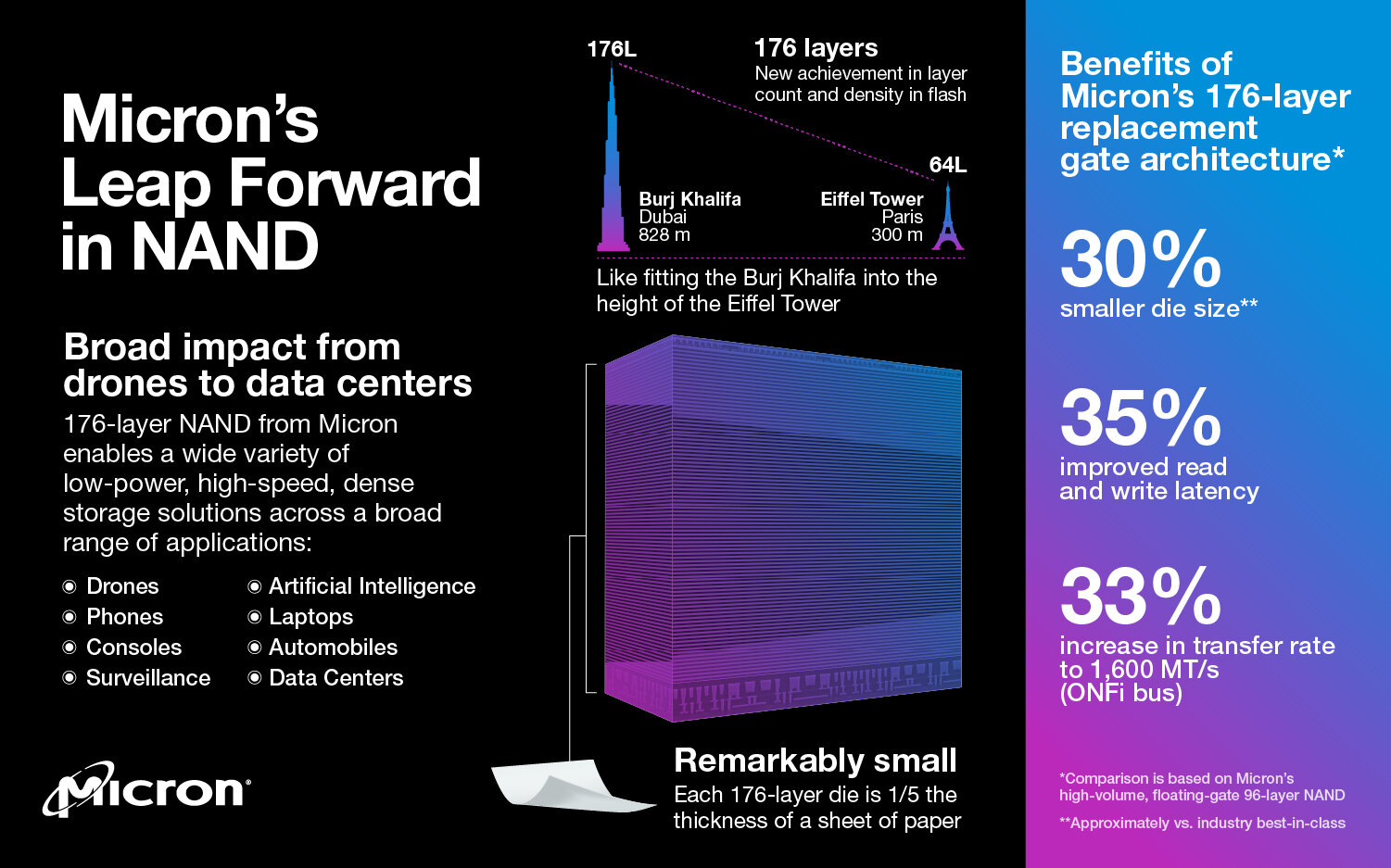

Micron gibt nun Vollgas beim in Eigenregie ohne Ex-Partner Intel entwickelten 3D-NAND. Mit neuer Replacement-Gate-Technik waren 128 Layer nur ein kleiner Zwischenschritt. Mit der zweiten Generation mit 176 Layern und 30 Prozent kleinerem Chip als bei der Konkurrenz geht die Fahrt erst richtig los.

Viele Jahre waren Intel und Micron im Joint Venture IM Flash Technologies (IMFT) Partner bei der Entwicklung und Herstellung von NAND-Flash-Speicher, wie er in Smartphones, SSDs, Speicherkarten und vielen anderen Produkten zu finden ist. Doch vor rund einem Jahr endete die Ära von IMFT und beide Unternehmen entwickeln 3D-NAND nun getrennt voneinander.

Micron ging neue Wege bei der Architektur

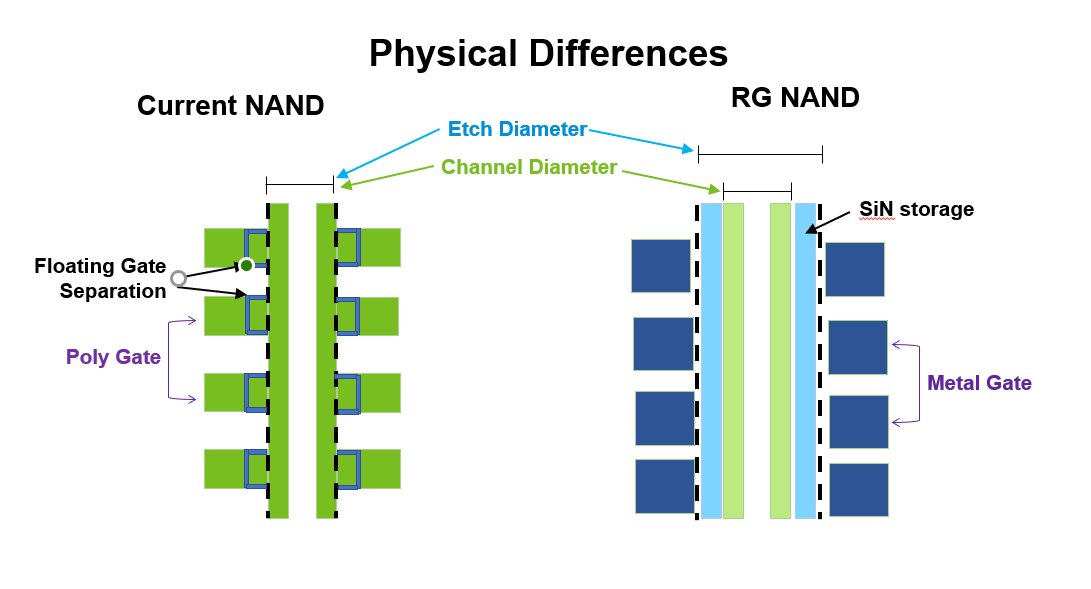

Während Intel den bisherigen Ansatz von IMFT mit einer Floating-Gate-Architektur weiter verfolgt und diese in Form eines 144-Layer-Designs als erste eigene Generation fortführt, hat Micron einen technischen Umbruch vollzogen. Replacement-Gate (RG) Technology nennt Micron die neue Architektur, die in einem Whitepaper (PDF) näher beschrieben wird.

176 hauchdünne Layer, 30 Prozent kleinerer Chip

Die erste Generation der RG-Architektur besitzt 128 Layer, hat kommerziell aber kaum Bedeutung erlangt und diente eher als Testvehikel. Bei der zweiten Generation macht Micron Nägel mit Köpfen und erhöht direkt auf 176 Layer. Micron ist es dabei gelungen, die Dicke der einzelnen Zellschichten (Layer) deutlich zu reduzieren, sodass der 176-Layer-Chip nicht höher als ein 64-Layer-Chip ausfällt. Konkret nennt Micron eine Dicke von 45 µm für ein 176-Layer-Die, das aus zwei übereinander gestapelten 88-Layer-Türmen besteht.

Die vorgestellte Variante speichert 512 Gigabit Daten pro Die und drei Bit pro Speicherzelle (TLC). Micron rühmt sich zudem damit, dass der Chip rund 30 Prozent kleiner als das bisher kleinste Pendant der Konkurrenz ausfällt, ohne jedoch konkrete Zahlen oder die Vergleichsbasis zu nennen. Der von Kioxia (früher Toshiba Memory) und Western Digital entwickelte BiCS5-Flash gilt mit 66 mm² bei 512 Gbit (TLC) bereits als sehr kompakt. Die Chipfläche ist ein wichtiger Aspekt bei den Herstellungskosten.

Durchsatz und Latenz optimiert

Doch nicht nur bei der Speicherdichte, sondern auch bei der Leistung verspricht Micron Fortschritte. So soll die Lese- und Schreiblatenz gegenüber der 96-Layer-Generation um über 35 Prozent und gegenüber der 128-Layer-Generation um mehr als 25 Prozent reduziert worden sein. Die NAND-Schnittstelle (ONFI) wurde von 1.200 MT/s auf 1.600 MT/s und somit um ein Drittel beschleunigt.

176L-NAND schon in Serie

Wie Micron angibt, läuft bereits die Serienfertigung des 176-Layer-NAND im Werk in Singapur und Kunden sollen auch schon mit Chips beliefert werden. Auch in SSDs der Tochtermarke Crucial soll der neue NAND Verwendung finden.

Für 2021 kündigt Micron „weitere neue Produkte auf Basis dieser Technologie“ an. Zu erwarten wäre etwa eine QLC-Variante mit vier Bit pro Speicherzelle und nochmals höherer Speicherdichte.