Sapphire Rapids: Details zu Intels CPUs mit bis zu 56 Kernen in vier Dies

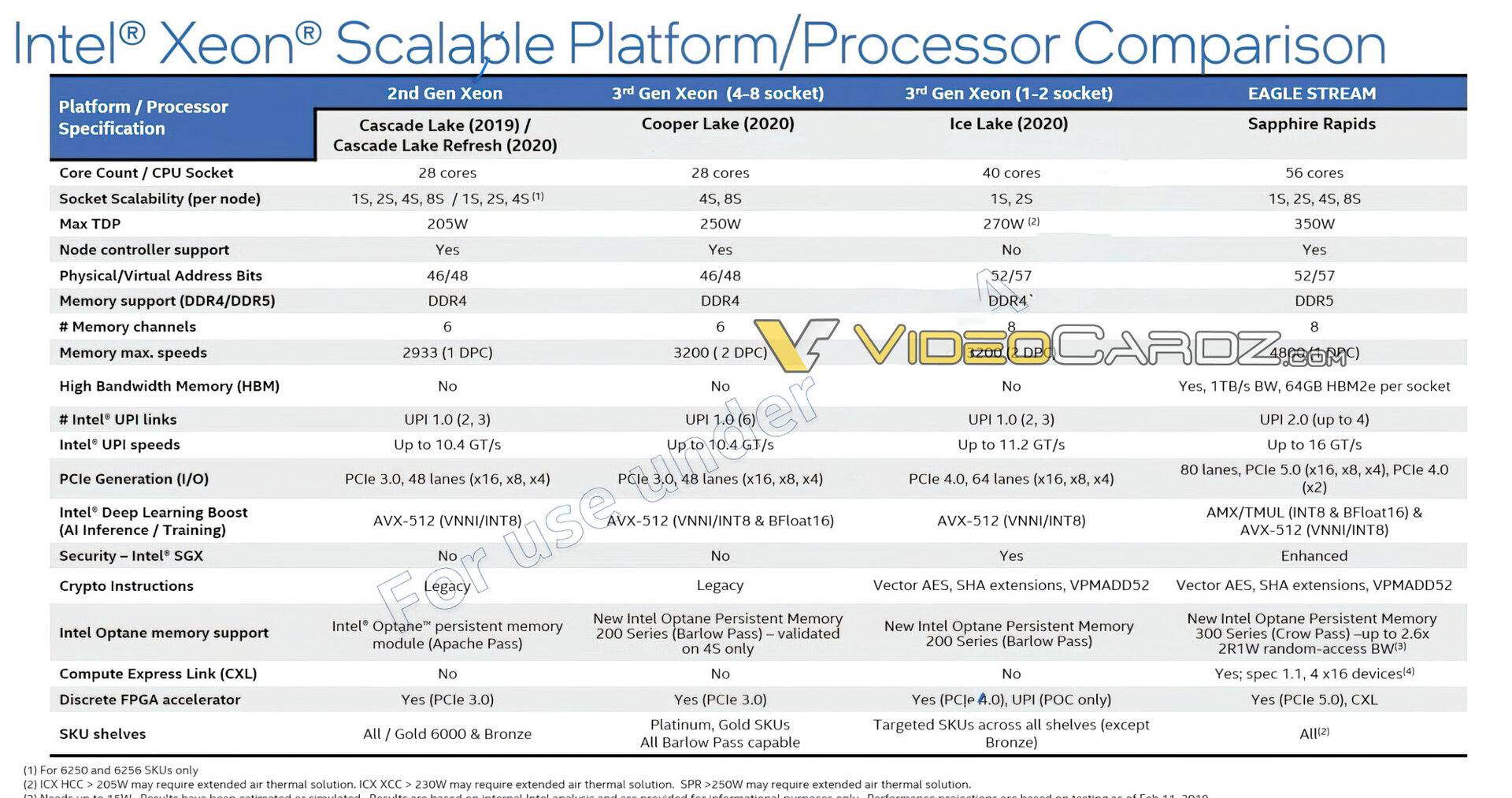

56 Kerne im Server, das gab es schon einmal bei Intel als „geklebte“ Experimental-CPU Cascade Lake-AP. Mit Sapphire Rapids sollen sie für zwei bis acht CPU-Sockel salonfähig werden, in kleinerem Package und auch geringerer TDP als bei CXL-AP. Maximal 350 Watt TDP können in Einzelfällen auch noch 64 GByte HBM2e abdecken.

Die TDP steigt gegenüber Ice Lake-SP

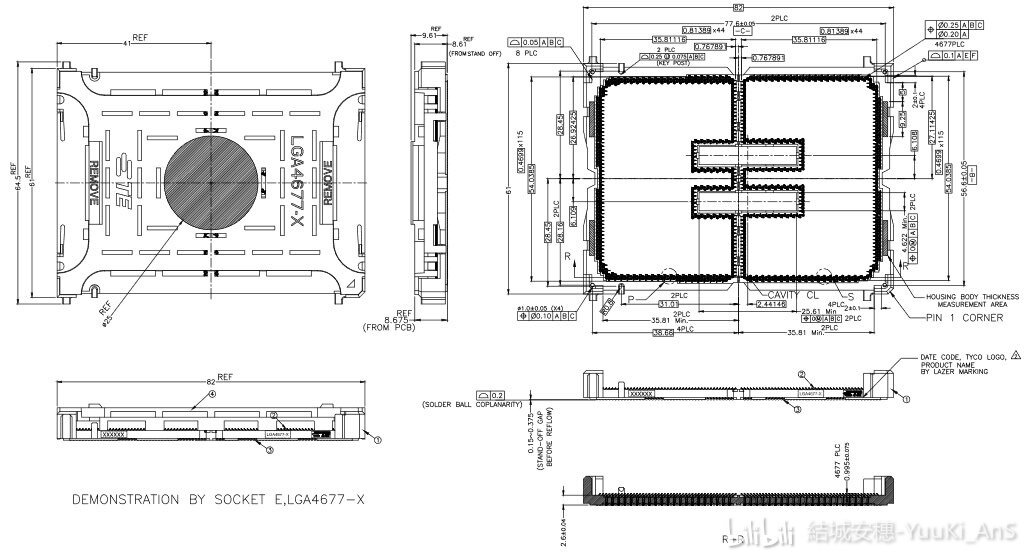

Sapphire Rapids wird gegenüber Ice Lake-SP im LGA 4189 wieder den Sockel wechseln. Die maximale TDP steigt von 270 auf 350 Watt an. TDP-Vergleiche über mehrere Generationen und Server hinweg sind jedoch stets eine schwierige Angelegenheit. Eine großflächige CPU kann auch mehr Wärme abführen. Intel Cascade Lake-AP konnte im riesigen Sockel mit 5.903 Kontaktflächen auch eine TDP von 400 Watt bewerkstelligen.

Von den Abmessungen des kompletten Packages scheint Sapphire Rapids allerdings kaum respektive nicht größer als Ice Lake-SP, sodass die TDP-Steigerung um bis zu 80 Watt oder 30 Prozent signifikant zu sein scheint. HBM2e dürfte, wie aktuell bereits Optane Memory, seinen Anteil daran haben. Fraglich ist auch, wie groß der Anteil durch CXL und PCIe 5.0 mit noch mehr Lanes als bisher ist und letztlich in der TDP zu Buche schlägt.

Multi-Chip-Ansatz mit vier Dies

Cascade Lake-AP war bereits eine Multi-Chip-CPU, geboren jedoch eher aus der Not heraus. Damals wurden einfach zwei reguläre Xeons mit jeweils 28 Kernen auf einem Package via UPI verbunden. Cascade Lake-AP war quasi eine Dual-Sockel-CPU nur auf einem Package. Sapphire Rapids wird den Multi-Chip-Ansatz anders umsetzen. Statt nur zwei Chips werden vier kleine CPUs mit je 15 Kernen zum Einsatz kommen, aus Yield-Gründen werden davon laut aktuellen Informationen jeweils 14 genutzt und bilden so die 56-Kern-CPU.

Das bereits erwähnte UPI wird darüber hinaus gehörig aufgewertet. Statt der zuletzt stetigen Tippelschritte mit minimaler Steigerung wird UPI 2.0 gleich den Sprung auf 16 GT/s machen und mit maximal 4 Links zur Verfügung stehen. Das dürfte notwendig sein, bieten die neuen CPUs doch nicht nur mehr Kerne, sondern eben auch viel mehr I/O und vor allem schnelleren Speicher, sei es abseits des Packages in Form von DDR5-4800 oder ganz nah an der CPU mit HBM2e.

Mehr PCIe-Lanes in erstmals 5. Generation

80 PCI-Lanes pro CPU sind zwar ein Fortschritt gegenüber Ice Lake-SP mit 64 Lanes, die größte Neuerung ist letztlich aber PCI Express 5.0 statt 4.0. Ob das am Ende gegenüber AMD reicht, bleibt abzuwarten. Dort gibt es bereits seit Epyc 7002 „Rome“ pro CPU 128 PCIe-4.0-Lanes, von denen in einem Dual-Sockel-Betrieb aber ein Teil für die Kommunikation der CPUs untereinander entfällt. Effektiv stehen dann am Ende maximal 162 Lanes zur Verfügung. Aber auch das sind auf dem Papier schon jetzt mehr und dürfte bei der nächsten Generation Genoa vermutlich nicht weniger werden.

Die 56-Kern-Variante dürfte wie aktuell bei Intel das Flaggschiff markieren, das Gros im Portfolio spielt sich hingegen darunter ab. Die Multi-Chip-Lösung dürfte vielfältige Möglichkeiten der Abstufung erlauben, ob mit HBM oder ohne kommt noch dazu. Durchgesickert waren zuletzt bereits eine 44-Kern-Version sowie eine Variante mit 24 Kernen. Da Sapphire Rapids sowohl Ice Lake-SP für Zwei-Sockel-Systeme als auch Cooper Lake-SP für Vier- und Acht-Sockel-Plattformen ablösen soll, wird das Portfolio an CPUs am Ende riesig ausfallen.

Viele neue Bilder zeigen mehr Details des Aufbaus der einzelnen Chips. Es lassen sich in der Tat 15 Kerne pro Die vermuten, was auf den Maximalausbau von 60 Kernen mit vier CPU-Chips pro Prozessor hinausläuft. Für eine bessere Ausbeute ist pro Die aber vermutlich ein Kern deaktiviert.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!