3D V-Cache Technology: AMD stapelt L3-Cache bei Ryzen auf 192 MByte

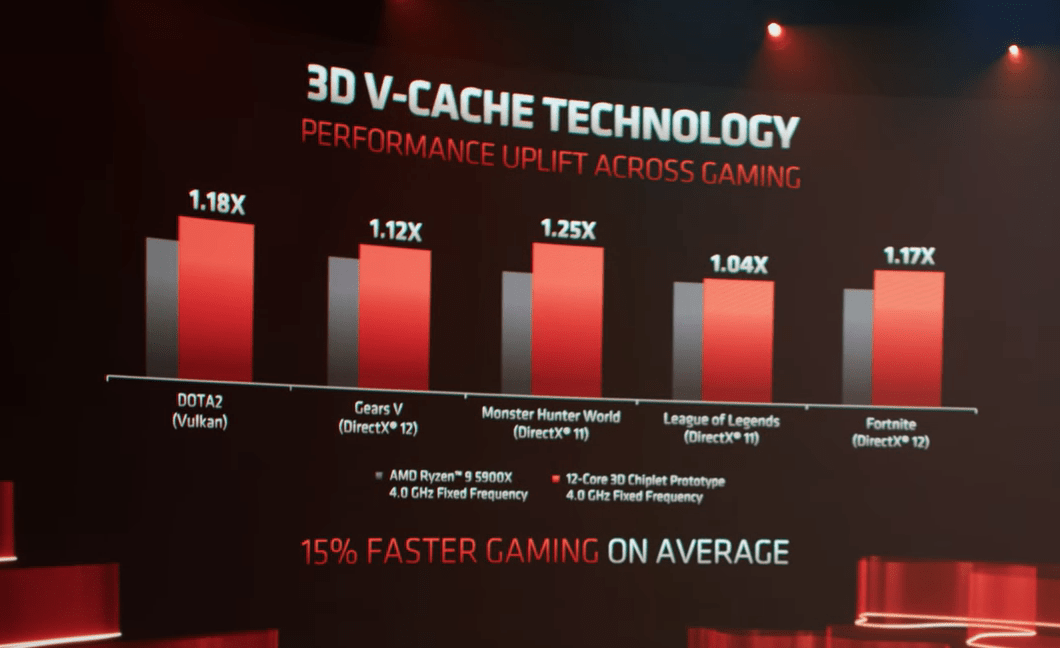

Eine Überraschung hob sich AMD im Rahmen ihrer Computex-2021-Keynote bis zum Schluss auf: Einen Prototyp mit gestapeltem L3-Cache, der einen Ryzen 5000 mit 192 MB ermöglicht. Dieses soll in Gaming-Szenarien im Schnitt rund 15 Prozent mehr Leistung ermöglichen. Ende des Jahres wird das in Produktion gehen.

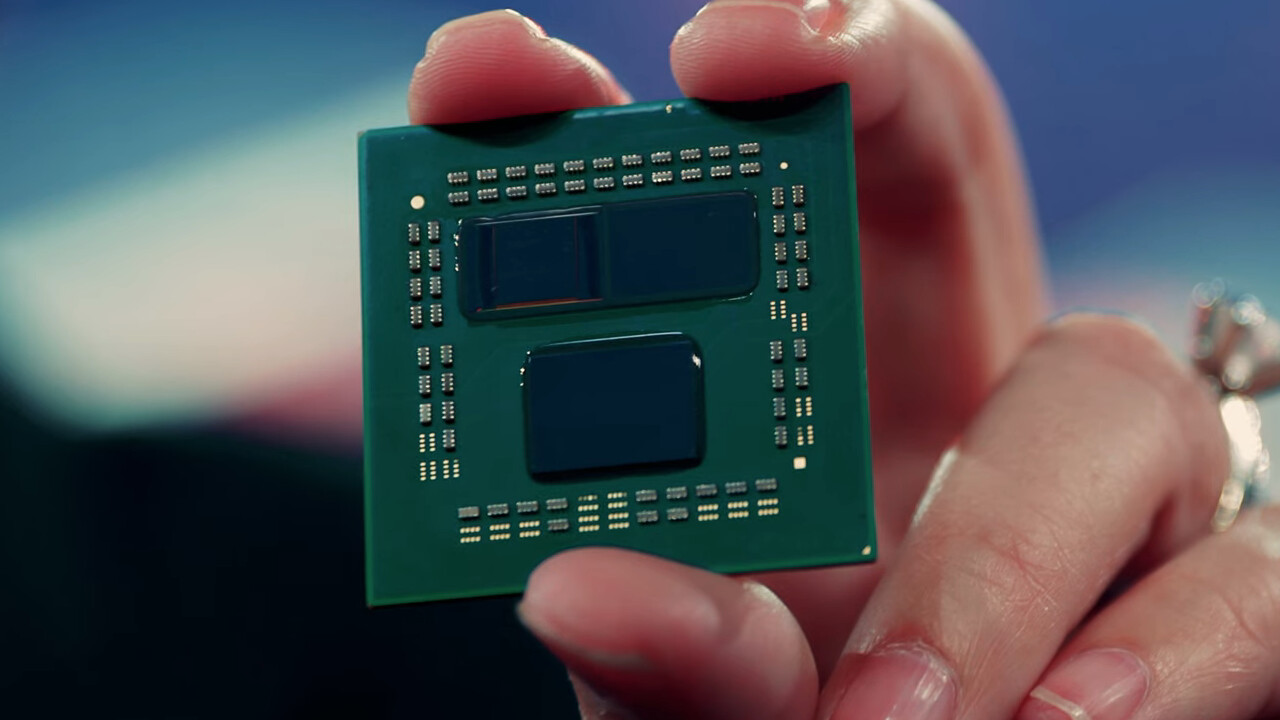

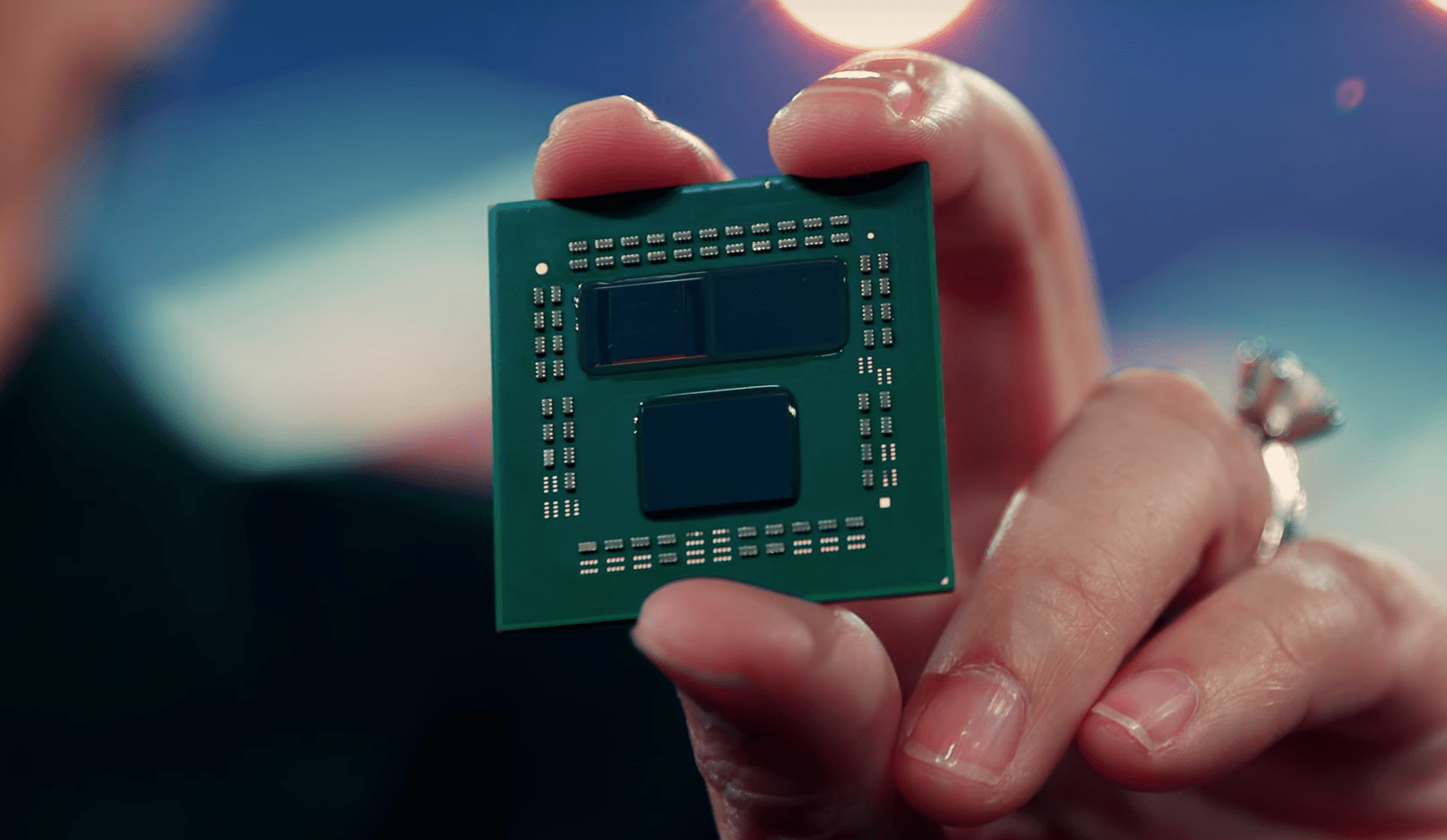

AMDs CEO Lisa Su zeigte den Prototypen eines Ryzen 9 5900X, bei dem auf einem CCD der Cache bereits gestapelt wurde. Der 64 MByte große zusätzliche Cache nimmt einen Platz von 6 mm × 6 mm ein und würde in Serie auf beiden CCDs seinen Platz finden. 96 MByte L3-Cache pro CCD sind das am Ende, insgesamt 192 MByte für einen 12- oder 16-Kern-Prozessor.

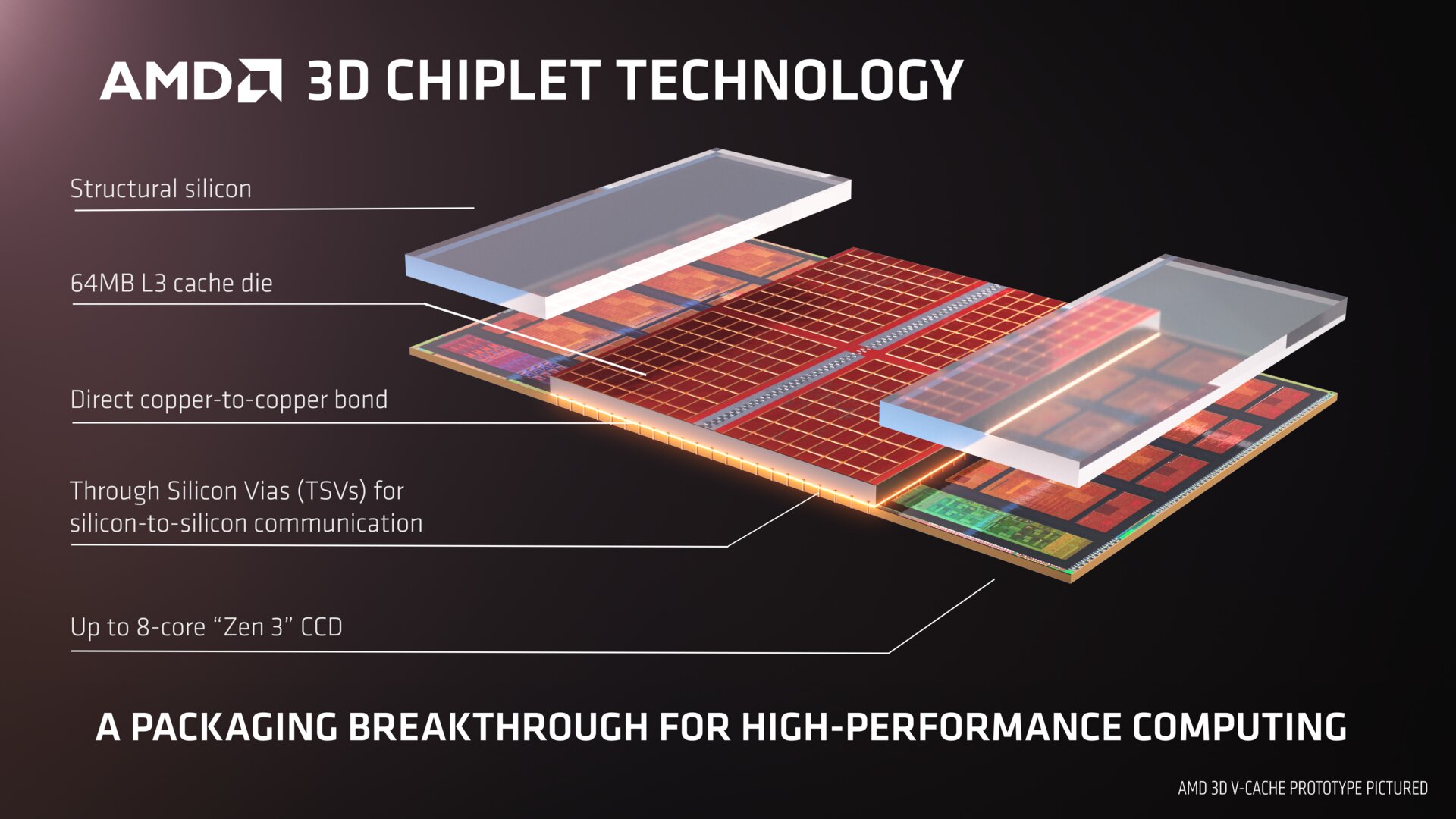

Die Technologie basiert auf TSVs, wie sie bereits bei diversen Stacking-Lösungen zum Einsatz kommen. Das Chipbonden erfolgt quasi über einen direkten Kontakt der Kupferschichten, keine zusätzlichen BGA-Kontaktflächen oder ähnliches, wie sie beispielsweise Intels Ansatz mit Stacking vorsieht. Der AMD-Ansatz soll vor allem bei der Energieaufnahme und den Temperaturen einen großen Vorteil bieten und am Ende ein viel effizienteres Gesamtpaket entstehen lassen und so die „most advanced stacking technology in the world“ hervorbringen, wie Lisa Su mit klarem Seitenhieb auf die letzten Intel-Präsentationen in dieser Richtung betonte.

Der Leistungszuwachs in Spielen, die am meisten von Cache profitieren, ist beeindruckend. Von vier über zwölf bis 17 Prozent und in den besten Spielen sogar 25 Prozent mehr Leistung heben die Messlatte deutlich an. Im Schnitt sieht AMD bei einem auf 4 GHz normierten 12-Kern-Prozessor den Zuwachs bei 15 Prozent.

Ende des Jahres sollen die Prozessoren der höchsten Serie damit produziert werden, ein Produktstart dürfte Anfang 2022 anstehen. Für Zen 4 ist das zu früh, das dürfte der Zen 3 Refresh sein, mit dem so bisher jedoch keiner gerechnet hatte. Für die Zukunft dürfte das Auswirkungen auf die gesamte Produktpalette haben, denn auch die Server-Lösung Milan sowie alle Nachfolger bieten sich bei dieser Technologie an.

Weitere Analysen im Nachgang der Keynote von vielfältiger Stelle offenbaren, dass AMD anscheinend zwei 32-MByte-Slices an L3-Cache für den Ryzen 5000 übereinander gestapelt hat, da nicht nur die Fläche dann ziemlich exakt mit der Lösung im CCD übereinstimmt.

Die zuletzt sehr oft zutreffenden Gerüchte vermelden zudem, dass AMD in Zukunft bis zu acht dieser 32-MByte-Lagen übereinander stapeln kann. Pro 8-Kern-Prozessor-Die mit bereits 32 MByte wären so zusätzlich 256 MByte L3-Cache möglich und würde bisher unrealistisch erscheinende 288 MByte L3-Cache für einen Acht-Kern-Prozessor erlauben.

AMD hat im Nachgang am Abend Fragen zur der 3D-Technologie beantwortet, die überraschende Erkenntnisse hervor brachten. Demnach ist der gestapelte L3-Cache ein nativer 64-MByte-Chip. Er fungiert als direkte Erweiterung des bestehenden L3-Caches im CCD, was keine Software-Anpassungen nötig macht, da er ohne Kontrollfunktionen und für alle der für die grundlegende Funktionalität benötigten Einheiten daherkommen kann. Da diese bereits vorhanden sind, kann AMD quasi 64 MByte reinen SRAM auf dem gleichen Raum wie zuvor 32 MByte unterbringen. Zen 3 war bereits von Vornherein für diese Möglichkeit vorbereitet, die Entwicklung und Umsetzung mit Partner TSMC nahm mehrere Jahre in Anspruch, erklärte AMD.

Leistungsaufnahme, Wärme und Latenzen sind wichtige Fragen, doch alle will AMD gelöst haben. Die Leistungsaufnahme soll extrem gering sein. Da der 3D V-Cache über den bisherigen L3-Cache gesetzt wird und dieser nicht der Hotspot der CPU ist, sollen thermische Probleme nicht auftreten. Dabei hilft aber auch effektives Powergating, nur aktive Teile nutzen auch Energie. Die Frage der Latenzen erklärt AMD knapp: Aus 2D wird 3D. Um von Punkt A nach B zu gelangen muss die Abfrage nicht den ganzen Cache durchlaufen, sondern kürzt über TSV in der 3. Dimension ab. So entsteht nahezu keine Strafzeit, in Tests soll diese quasi nicht einmal merkbar sein.

Um den zusätzlichen L3-Cache auf dem CCD unterzubringen, ohne die Höhe zu verändern, werden die CCDs der betreffenden Prozessoren in Zukunft dünner, um am Ende mit gestapeltem Zusatz-Cache wieder genau so hoch zu sein wie der I/O-Die und um letztlich unter den Heatspreader zu passen. AMD bestätigte noch einmal, dass es sich beim ersten Produkt um Zen-3-Prozessoren in 7-nm-Fertigung handeln wird, die als High-End-Ryzen auf den Markt kommen. Produktionsstart ist Ende des Jahres.

Zukünftige Produkte schloss AMD natürlich nicht aus, ohne jedoch welche zu nennen. APUs stehen dabei neben Server-Prozessoren hoch im Kurs. AMD erklärte aber, dass Cache kein Allheilmittel für alles sei. DRAM wird man damit nicht ersetzen können, der Cache helfe jedoch in gewissen Szenarien.

Ihr habt die Wahl: Macht mit bei den Reader's Choice Awards 2025 und bestimmt eure Hersteller des Jahres!

- ROG Strix G15/G17 Advantage: Asus' Gaming-Notebook mit RX 6800M und 5900HX

- MSI: Details zum SSD-Debüt mit M480, M470 und M370

- ASRock DeskMini Max: Ein DeskMini X300 mit Platz für diskrete Grafikkarten

- +26 weitere News