IPU statt DPU: FPGAs/CPUs mit SmartNIC von Intel fürs Datacenter

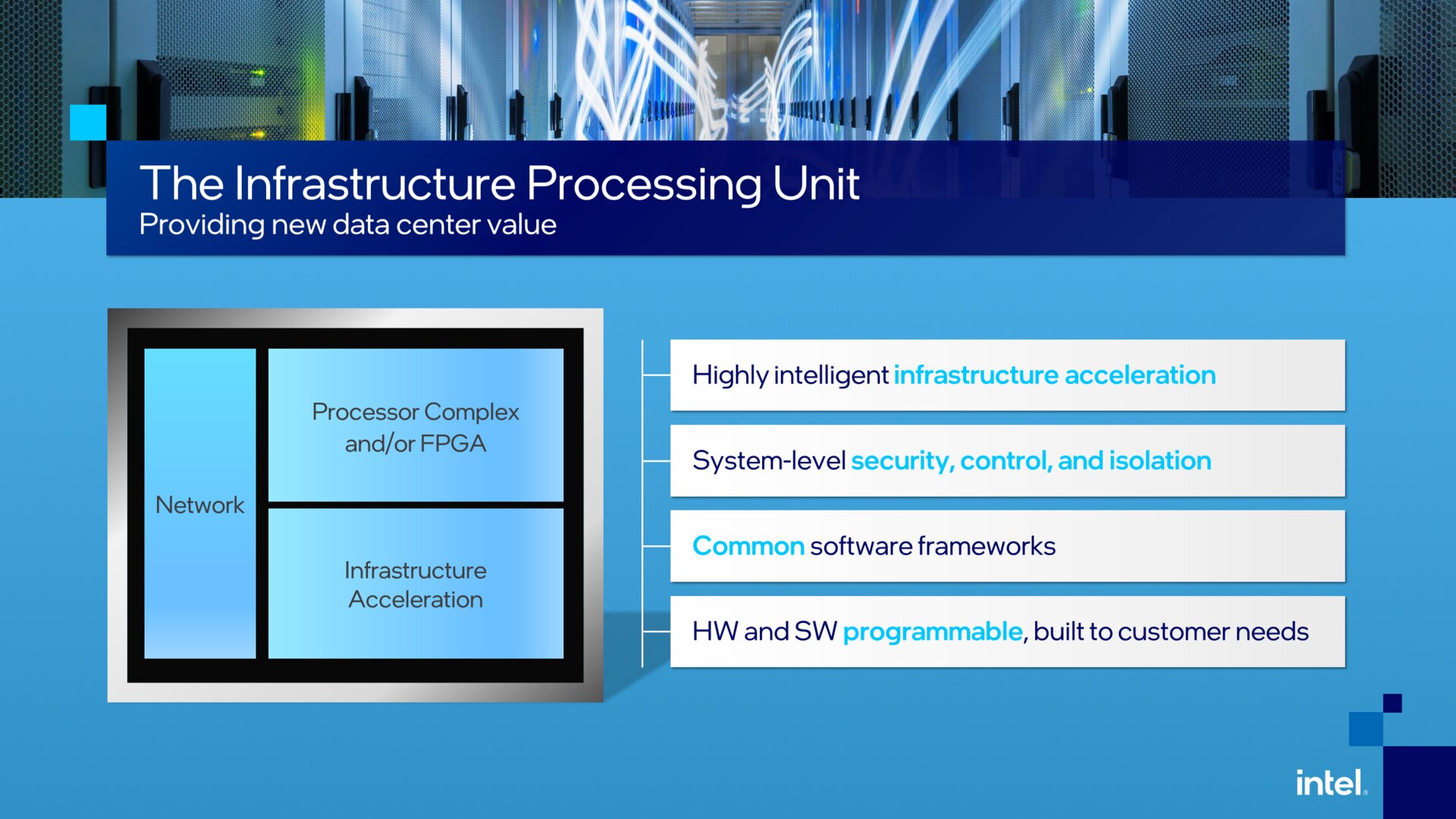

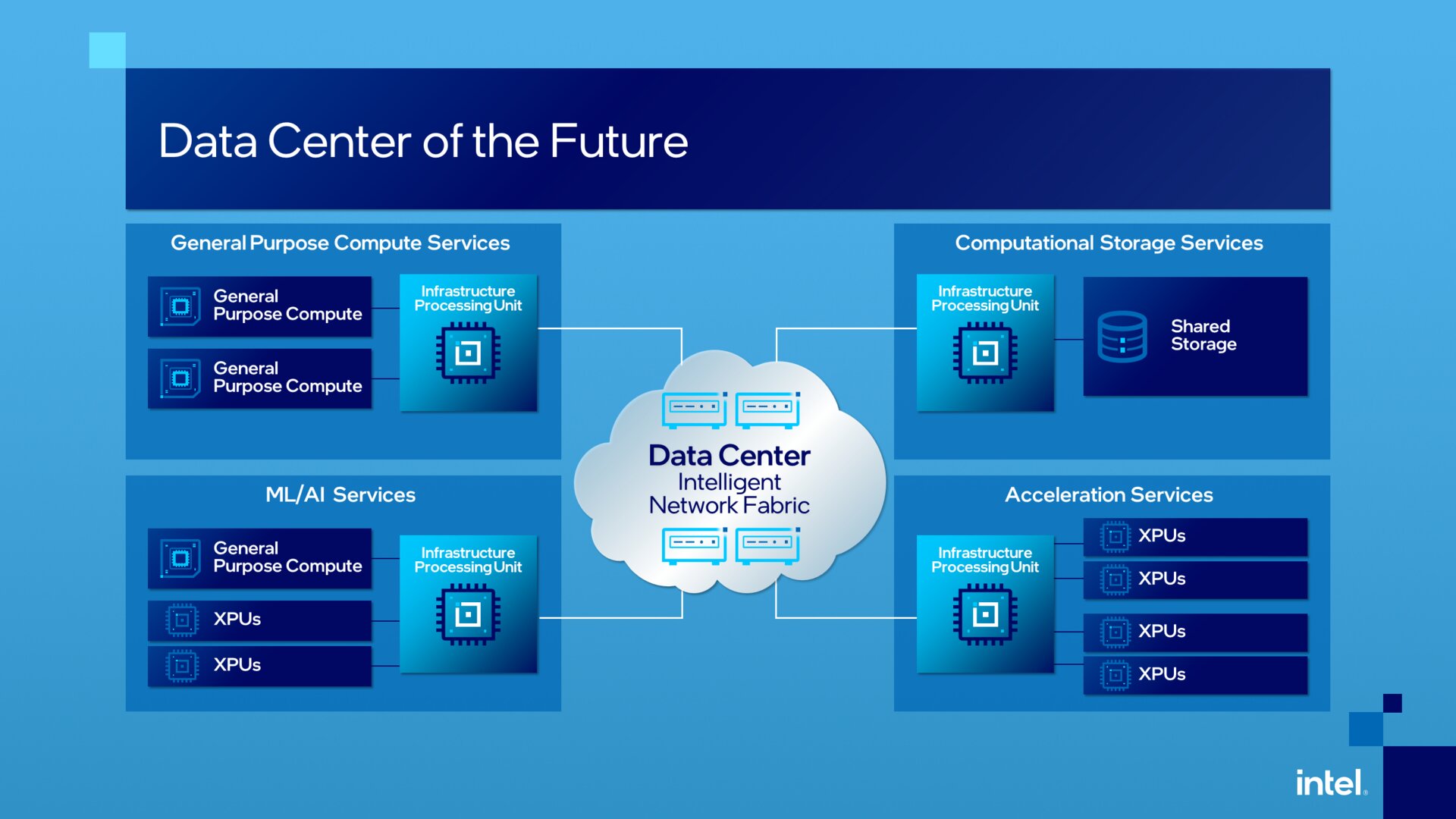

In einer Infrastructure Processing Unit (IPU) sieht Intel die teilweise Zukunft im Datacenter. Speziell auf die Bedürfnisse von Cloud-Anbietern oder Kommunikations-Dienstleistern abgestimmt, können die großen Kunden ein Wörtchen mitreden, was genau diese Lösung bieten soll. Grundlage dafür ist ein Multi-Chip-Design.

Bei Nvidia aber auch anderen Herstellern wie Marvell, Broadcom, Xilinx und VMware – von denen der Intel-CEO kommt – nennt sich die smarte Netzwerkkarte Data Processing Unit (DPU) und wurde beispielsweise wie von Nvidia als BlueField bereits in mehreren Generationen vorgestellt.

Intels IPU ist ein wenig anders und vor allem spezieller als General-Purpose-DPUs, zielt im Grunde genommen aber auf die gleichen Märkte. Nicht zu verwechseln ist IPU im Übrigen mit Intels eigener Imaging Processing Unit (IPU) oder Intel Platform Update (IPU), auch von Mellanox gibt es eine IPU sowie Graphcore IPU – für Verwirrung ist hier schnell gesorgt, denn alle meinen etwas anderes.

IPU ergänzt XPU und CPU

Die IPUs von Intel sind eine Mischung aus Prozessor samt moderner Netzwerktechnik, SmartNICs nennt sich das Segment. Sie sollen in den Bereichen helfen, in denen reguläre CPUs viel Overhead bilden und ihrer eigentlichen Aufgabe gar nicht nachkommen können. Einer Studie von Facebook aus dem vergangenen Jahr zufolge, die Intel anführt, kommt eine CPU bei den Microservices, die viele Cloud-Anbieter beispielsweise zur Lastverteilung nutzen, im schlimmsten Fall nur zu 18 Prozent ihrer eigentlichen Aufgabe nach, während sie sich zu 82 Prozent mit anderen Dingen befasst.

Our characterization reveals that microservices spend as few as 18% of CPU cycles executing core application logic (e.g., performing a key-value store); the remaining cycles are spent in common operations that are not core to the application logic (e.g., I/O processing, logging, and compression). Accelerating such common building blocks can greatly improve data center performance.

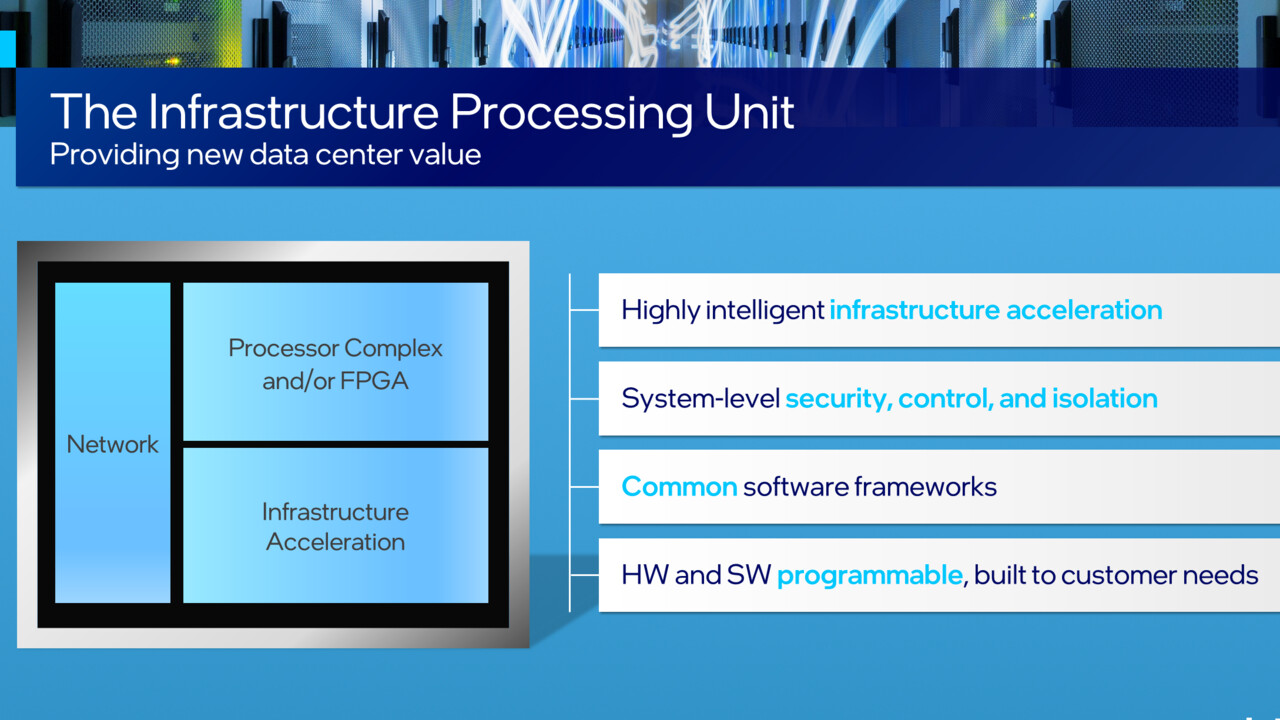

Facebook

Durch einen Zusatzchip neben dem eigentlichen Prozessor sollen diese Funktionen von der IPU übernommen werden, während sich die CPU wieder den eigentlichen Aufgaben widmet und so unterm Strich deutlich mehr Leistung dafür frei wird. Letztlich entsteht damit quasi eine Mischung aus CPU, FPGA und NIC – so etwas gab es von Intel und Partnern schon mehrfach, bisher aber als zwei- oder gar dreigeteilte Plattform-Lösung für einen PCIe-Slot, die jetzt auf einem Chip vereint wird. Es ist der nächste logische Schritt in der Entwicklung.

Die aktuell im Test bei „mehreren Partnern“ befindliche IPU ist laut Intel ein FPGA, diese stehen von sich aus für viel mehr Flexibilität seitens des Kunden, sind jedoch auch entsprechend teuer. Intel nennt unter anderem Microsoft, Baidu und VMWare als Abnehmer.

ASICs sollen in der nächsten Runde aufgelegt werden, Intel sieht Marktchancen für sie in vielen Bereichen. Wie genau diese letztlich aussehen und was sie leisten werden, wurde noch nicht benannt. Auf dem neu aufgelegten IDF, welches sich jetzt Intel ON nennt, will Intel im Oktober dieses Jahres mehr Details zu Hardware aber auch Software verraten.

Die sehr kurz gehaltene Vorstellung übernahm Intels Chef der Datacenter-Sparte Navin Shenoy. Interessierte finden die Ankündigung im Video.

- Für Notebooks & AIOs: Intel Meteor Lake kommt nicht für „klassische Desktop-PCs“

- Moore's Law lebt: Das „Grundgesetz“ wird mit neuen Technologien am Leben gehalten

- 576 E-Cores im Server: „Pro Kern will die Lizenz eher niemand bezahlen“

- +27 weitere News