Chip-Fertigung: Intel ist Erstkunde für High-NA-EUV-Systeme von ASML

Intel wird Erstkunde der High-NA-EUV-Systeme von ASML und damit ab 2025 Gate all Around (GAA) in der Chip-Fertigung zum Einsatz bringen. Die überraschende Ankündigung ist eine klare Ansage: Intel will wieder Marktführer in Sachen Chip-Fertigung werden, etwas, das der Hersteller mit EUV nahezu komplett verschlafen hat.

EUV verschlafen, bei High-NA-EUV auf Platz 1

Geld sparen und den Weg des geringsten Widerstandes gehen, hieß das Motto in den letzten Jahren bei Intel, was auch EUV einschloss. So sollte selbst die nächste CPU-Generation Meteor Lake aus der 7-nm-Fertigung, die seit heute offiziell „Intel 4“ heißt, so weit wie möglich auf EUV verzichten und mit klassischer Lithografie-Fertigung vor allem günstig werden. Mit dieser Planung hat sich Intel aber letztlich fast vollständig blamiert und musste sehr weit zurück an das Reißbrett gehen, um zu erkennen, dass es ohne EUV einfach nichts wird. Nun wirbt Intel damit, dass mit Meteor Lake viele Lagen mit EUV belichtet werden sollen, wenn die CPUs 2023 verfügbar sein werden. Doch erst in der Generation darauf wird die Umstellung auf EUV noch weiter forciert, was wiederum noch einmal deutlich macht, wie spät Intel in dieser Beziehung letztlich ist.

Leader statt Follower

Das soll sich in ferner Zukunft nicht wiederholen und Intel will das bereits heute beweisen, indem der Konzern erklärt: High-NA-EUV, die nächste Generation an Belichtungssystemen von ASML, wird Intel als Erstkunde erhalten. Intel will wieder Leader statt Follower sein.

Intel und ASML im selben Zeitplan

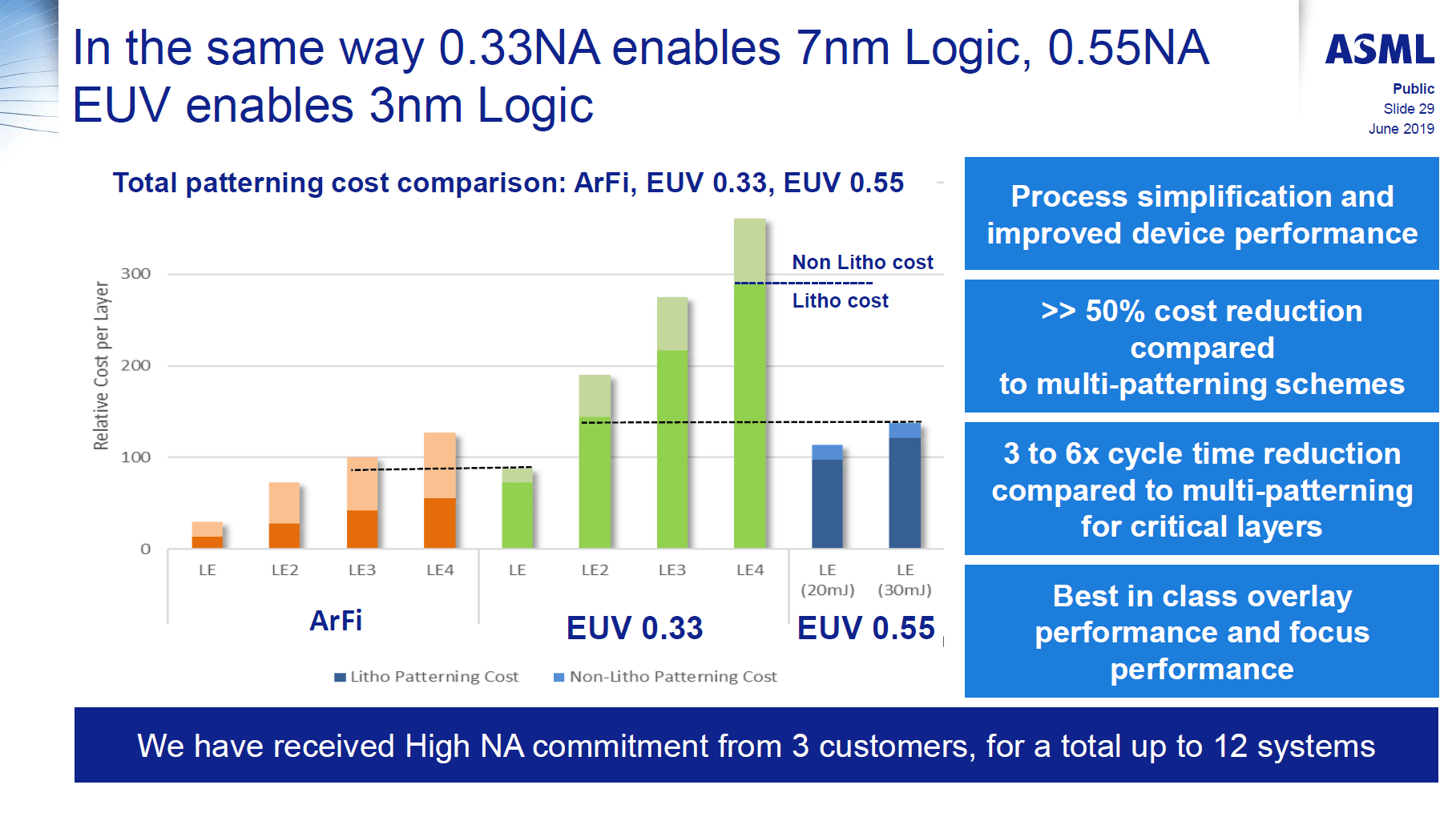

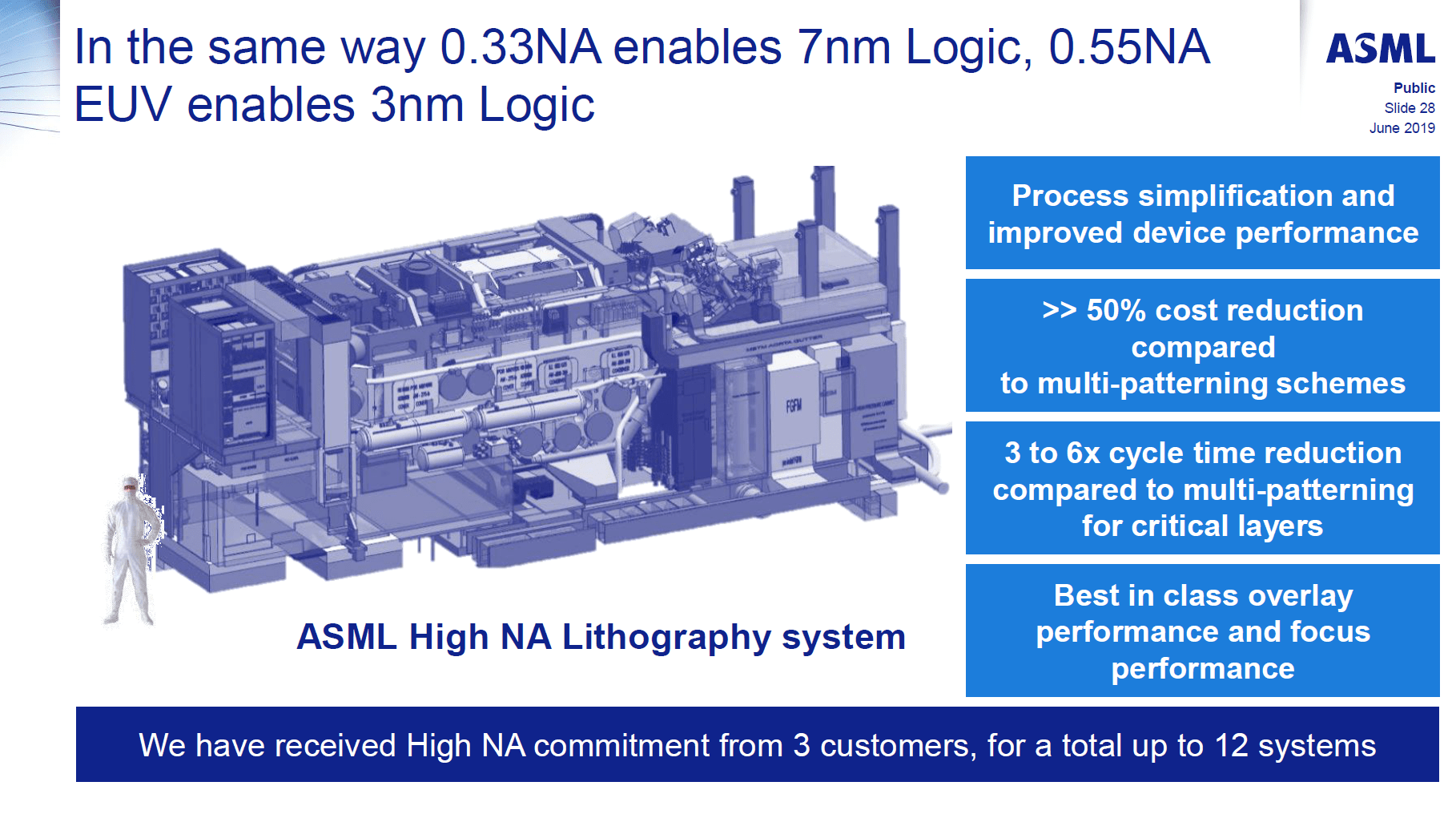

High-NA (High numerical aperture) verspricht einen ähnlichen Gewinn wie der Sprung von Immersions- zu EUV-Lithografie. Multi-Patterning soll dabei möglichst aus dem Weg gegangen werden, denn eine hohe Anzahl an Belichtungsschritten birgt stets Fehlerquellen und treibt die Kosten in die Höhe. Für kleiner werdende Strukturen kommt irgendwann einmal der Punkt, an dem es kaum noch weiter geht – so wie Intel es bei 7 nm lernen musste. ASML nannte zuletzt immer die 3- oder 2-nm-Fertigung als Einstieg in High-NA. Das passt zu dem heute umbenannten neuen Intel-Namensschema. Denn Intel will bei „Intel 18A“ (in Anlehnung an 1,8 nm) ab dem Jahr 2025 das erste Mal Chips damit fertigen, ASML plant für diesen Zeitraum die ersten Lieferungen.

Our next-generation EUV systems, High-NA (0.55NA), will enable further shrink and partly eliminate complicated exposure schemes involving several 0.33NA exposures by a single 0.55NA exposure. With High-NA, the number of non-litho processing steps can therefore also be reduced. This will effectively limit the energy consumption per wafer further.

ASML

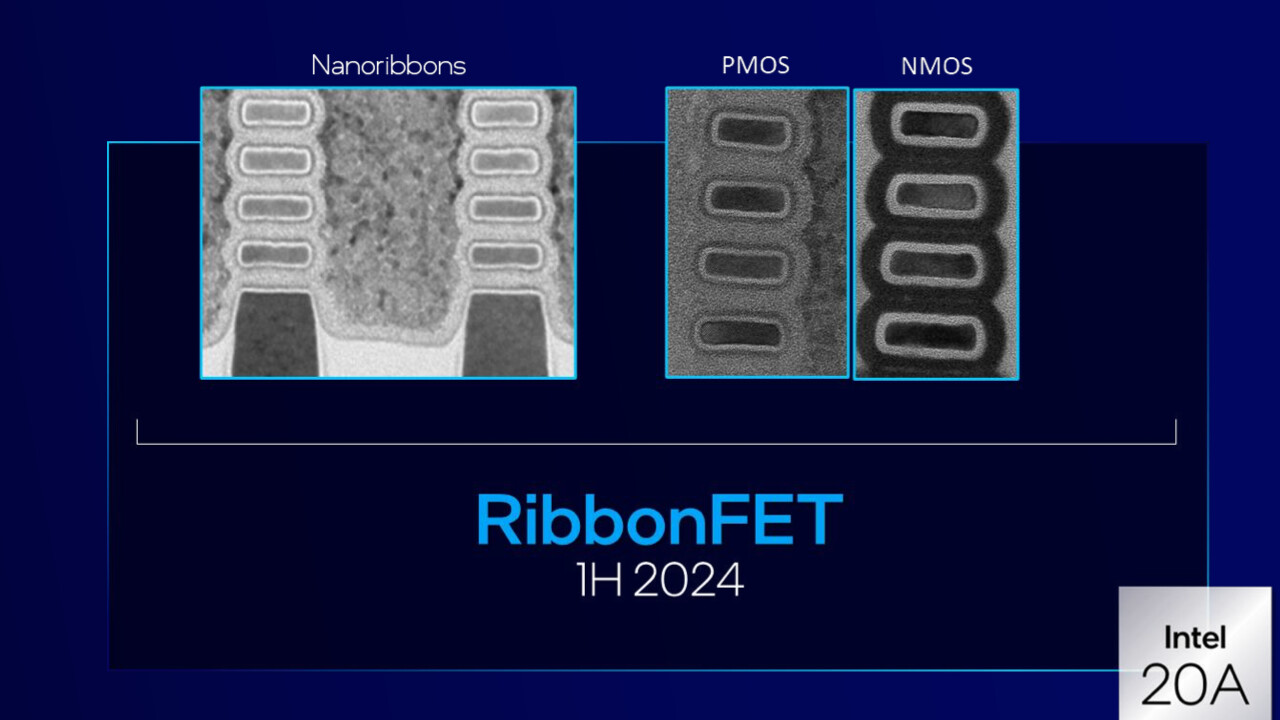

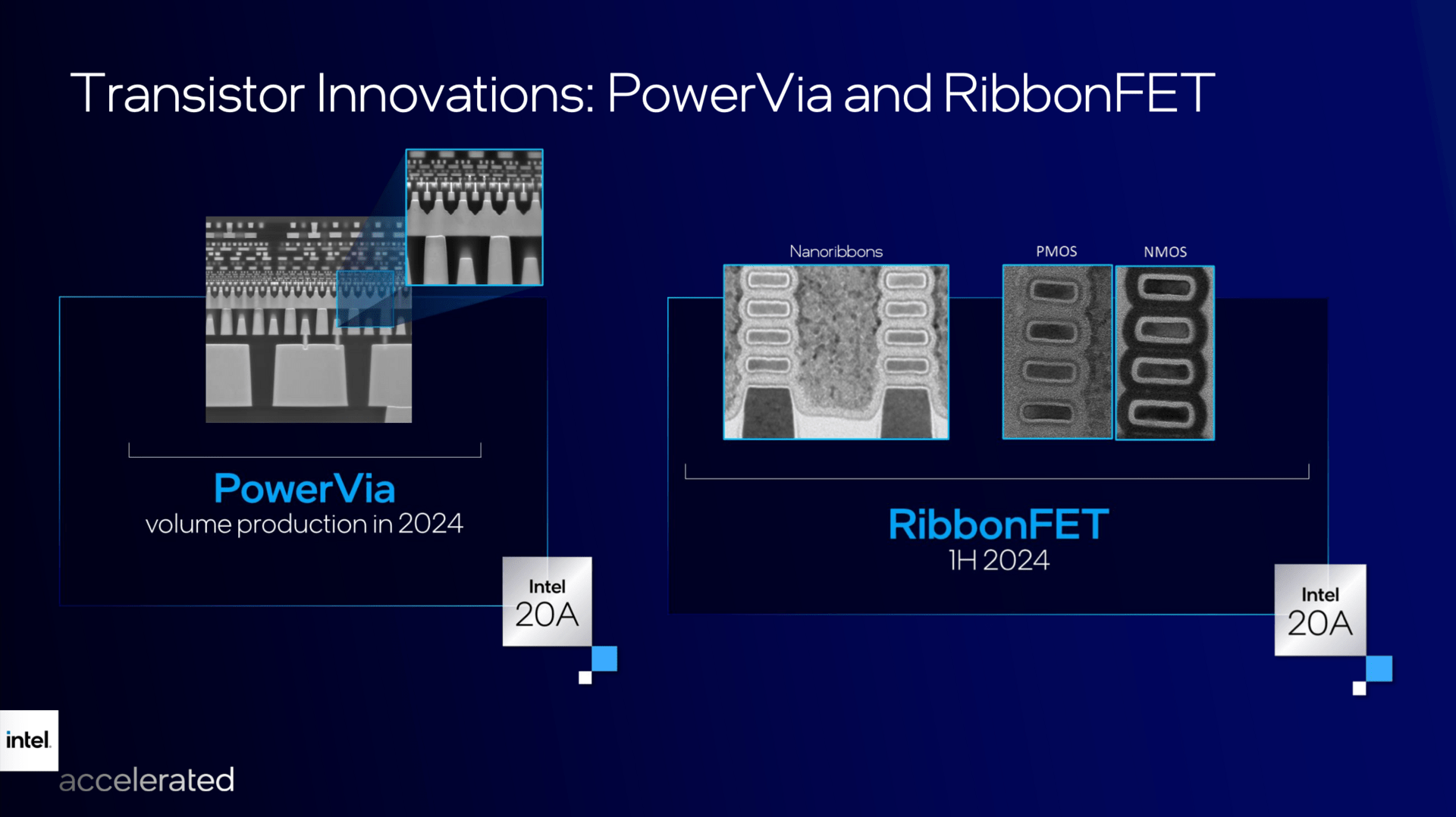

Gate All Around (GAA) heißt bei Intel RibbonFET

Ohne einen zusätzlichen Marketing-Schachzug kommt Intel auch bei der neuen Transistor-Generation nicht aus. Statt die Technologie Gate All Around zu nennen, wie jeder Hersteller in der Branche, nutzt Intel die Bezeichnung „RibbonFET“. Das erinnert an die Anfänge der 22-nm-Fertigung, als Intel die FinFETs stets 3D-Transistoren getauft hatte.

GAA soll bei Intel erstmals mit der Fertigungsstufe „Intel 20A“ noch vor dem Einsatz von High-NA-EUV ab 2024 eingeführt und genutzt werden – nicht nur für eigene Chips, sondern auch für die von anderen Firmen wie beispielsweise Qualcomm. Parallel zu den neuen FETs will Intel an der Stromversorgung respektive den Interconnects Änderungen vornehmen. Das Gesamtpaket dürfte deutlich effizienter werden, sofern sich die Vorhaben auch so umsetzen lassen wie geplant.

PowerVia is Intel’s unique, industry-first implementation of backside power delivery – eliminating the need for power routing on the front side of the wafer and providing optimized signal routing while reducing droop and lowering noise.

Intel

Kommt Intel bei GAA TSMC und Samsung zuvor?

Das könnte in Summe ein sehr interessantes Duell im Foundry-Markt ergeben. TSMC ist ebenfalls noch bei der Forschung an Gate All Around, traute sich zuletzt nicht, öffentlich einen Zeitplan dafür zu nennen. Vor dem Jahr 2023 und der für dann geplanten 2-nm-Fertigung wird aber nicht damit gerechnet, das Jahr 2024 dürfte realistischer sein.

Samsung wiederum hatte kürzlich eingestanden, für die Foundy-Kundschaft ebenfalls erst Ende 2023 respektive eher 2024 Gate All Around anbieten zu können. Offiziell forschen die Koreaner am längsten daran, respektive waren als Erster damit an die Öffentlichkeit gegangen, doch Rückschläge haben auch in diesem Fall für Verzögerungen gesorgt. Interessanterweise ist Qualcomm auch bei Samsung Kunde, der Entwickler der Snapdragon-SoCs kann ab 2024 also aller Voraussicht nach mindestens zwischen zwei GAA-Prozessen in zwei Foundrys wählen.

ComputerBase hat Informationen zu diesem Artikel von Intel unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.