Flash-Speicher: Tiefgefrorener HLC-NAND mit 6 Bit pro Zelle

Während PLC-NAND mit 5 Bit pro Speicherzelle noch Jahre von der Marktreife entfernt ist, wird bereits mit 6 Bit pro Zelle beim sogenannten Hexa-Level-Cell-NAND (HLC) experimentiert. Eine funktionierende HLC-Speicherzelle hat Kioxia bereits demonstriert, doch wurde dafür eine extreme Kühlung nötig.

Fast völlig unter dem Radar der westlichen Tech-Medien haben Forscher des NAND-Flash-Herstellers Kioxia (ehemals Toshiba Memory) im April über ihre Erkenntnisse auf dem Weg zur 6-Bit-Speicherzelle im Rahmen der IEEE Electron Devices Technology and Manufacturing (EDTM) 2021 Conference in China gesprochen. Im Mai wurde die Forschungsarbeit unter dem Titel „Cryogenic Operation of 3D Flash Memory for New Applications and Bit Cost Scaling with 6-Bit per Cell (HLC) and Beyond“ im Internet veröffentlicht. Darauf aufmerksam gemacht hat kürzlich die Website Blocks and Files, die auf einen detaillierten Bericht der japanischen Website PC Watch von Ende Juli verweist.

6-Bit-Zelle mit Stickstoffkühlung

Demnach haben die Forscher eine funktionierende Speicherzelle mit 6 Bit demonstriert. Mit jedem Bit verdoppelt sich die Zahl der nötigen Zustände: Bei SLC-NAND mit 1 Bit sind es 2, bei MLC mit 2 Bit sind es 4, bei TLC mit 3 Bit sind es 8, bei QLC mit 4 Bit sind es 16 und bei PLC mit 5 Bit deren 32. Je mehr Zustände unterschieden werden müssen, desto komplexer und langsamer ist das Programmieren respektive „Beschreiben“ der Speicherzelle. Leistung wie auch Haltbarkeit nehmen analog dazu ab und die Anforderungen an die Fehlerkorrektur steigen. Um die Information von 6 Bit abzubilden, werden also 64 unterschiedliche Spannungszustände innerhalb der Zelle benötigt.

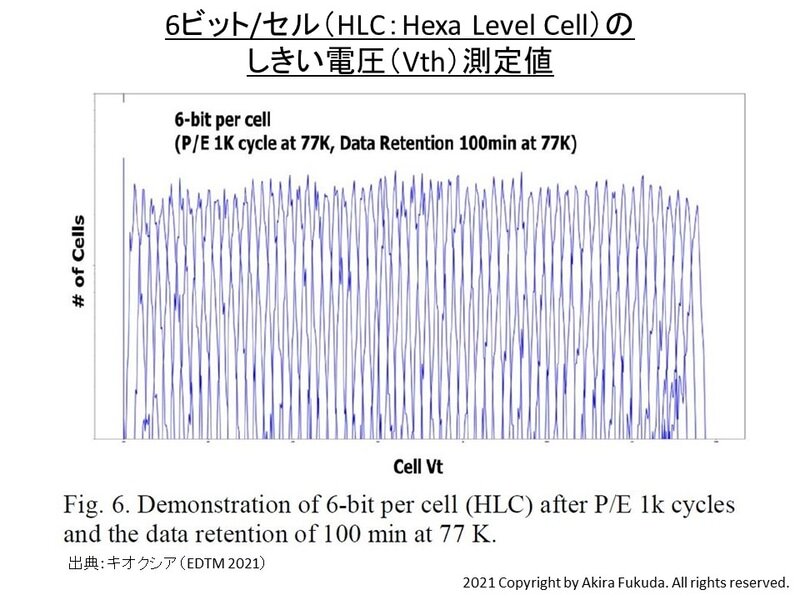

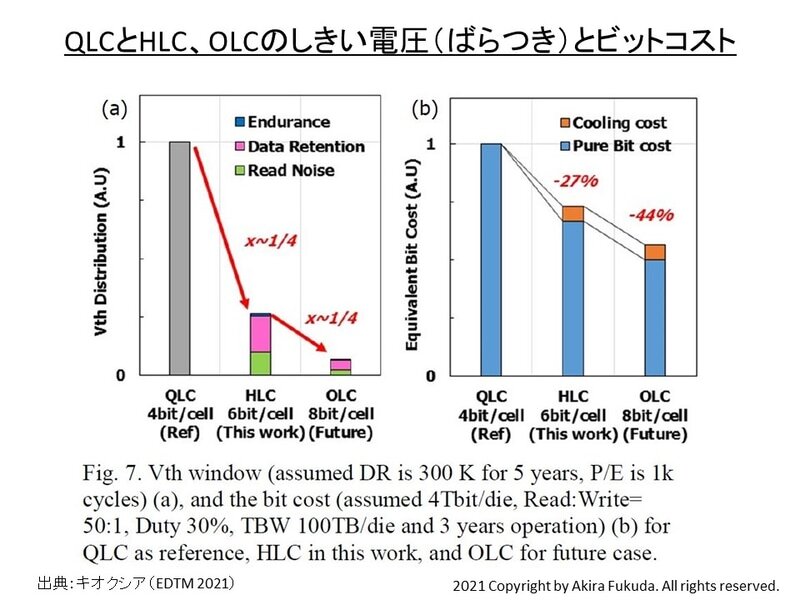

Um 64 Zustände mit bisheriger 3D-NAND-Technik zu erreichen, musste der Chip allerdings stark gekühlt werden und wurde in flüssigen Stickstoff bei -196 °C getaucht. Der Controller habe wiederum bei Zimmertemperatur gearbeitet. Durch die Kühlung wurden Spannungsschwankungen, das sogenannte Signalrauschen, sowie der Verlust von Elektronen durch „thermionische Emission“ reduziert. Die Haltbarkeit der HLC-Zelle soll dadurch von 100 auf 1000 Schreibzyklen gesteigert worden sein, was in etwa dem Niveau heutigen QLC-Speichers mit 4 Bit pro Zelle entspricht, der allerdings dafür keine Stickstoffkühlung benötigt.

8 Bit (OLC) ebenfalls denkbar

Auch Octa-Level-Cell-NAND (OLC) mit 8 Bit pro Speicherzelle sei unter diesen extrem niedrigen Temperaturen denkbar, doch würden dafür zusätzlich Änderungen bei Material und Design der Zellen nötig. Fraglich bleibt, wie die Praxis eines Massenspeichers mit derartigen Anforderungen zur Kühlung aussehen könnte.

PLC mit 5 Bit muss erst mal ankommen

Erst einmal heißt aber der nächste Schritt beim 3D-NAND Penta-Level-Cell (PLC) mit 5 Bit pro Speicherzelle. Auch hier forscht Kioxia zusammen mit Partner Western Digital an einer praxistauglichen Lösung. Bereits vor zwei Jahren haben beide Unternehmen PLC-NAND auf dem Flash Memory Summit 2019 thematisiert. Einige Monate später stellte Kioxia mit „Twin BiCS Flash“ eine neuartige Speicherzellenstruktur vor, die mehr als 4 Bit pro Zelle, also auch PLC, ermöglichen soll.

Im Vergleich zum bisherigen BiCS-Flash mit kreisförmigen Charge-Trap-Zellen (CT) nutzt Kioxia dafür halbkreisförmige Floating-Gate-Zellen (FG). Die neue Struktur soll das Fenster zur Programmierung der Zelle vergrößern, obgleich die Zellen sogar kleiner als bei den bisherigen CT-Zellen ausfallen. Damit sei die Technik „ein vielversprechender Anwärter“, um vier Bits pro Zelle (QLC) noch zu übertreffen.

Doch in Reichweite ist eine solche Lösung noch lange nicht. Der Technikchef von Western Digital Siva Sivaram hatte im Juni erklärt, dass er erst in der zweiten Hälfte der laufenden Dekade, also frühestens 2026, damit rechnet, dass PLC den Markt erreicht. Wann und ob überhaupt HLC- oder gar OLC-NAND erscheinen wird, steht daher noch in den Sternen.

Zunächst kommen mehr Layer

Erst einmal werden die Hersteller die Zahl der übereinander gestapelten Lagen mit Speicherzellen (Layer) beim 3D-NAND weiter erhöhen, um die Flächendichte nochmals zu steigern und mit mehr Bit pro Wafer die Kosten weiter zu senken. Aktuell ist die Branche bei 176 Layern angekommen. Micron liefert den 176-Layer-NAND schon länger in Serie aus, Samsung und SK Hynix ziehen in Kürze nach.

Samsung plant für seine 8. Generation 3D-NAND (V-NAND V8) schon fest mit mehr als 200 Layern und schließt für die Zukunft mehr als 1.000 Layer nicht aus.